基于PCIE的高速光纤图像实时采集系统设计

2013-12-07任国强徐永刚

雷 雨 ,任国强 , 孙 健 , 徐永刚 , 黄 辉

(1.中国科学院光电技术研究所,四川 成都 610209;2.中国科学院大学,北京 100149)

随着高分辨率、高频帧的CCD相机在航测中的广泛使用,如何对产生的高速图像数据进行实时记录,成为了一个技术难题。光纤通信具有带宽高、价格低廉、传输距离长等优点,单根光纤的传输带宽达到10.2 Tb/s。大量光电转换模块的出现,使光纤在高速图像采集传输系统中大量使用,常规光模块带宽达到2 Gb/s,而传统通过PCI总线与主机通信的理论带宽只有133 MB/s,但当实际数据采集速度到达100 MB/s左右时就变得相当困难 ,难以满足对记录带宽的要求。PCIE是继PCI后的第三代高性能I/O总线,与PCI相比,PCIE属于串行总线,引脚少,采用基于数据包的协议进行事务编码,每个传输通道独享带宽;硬件接口简单,采用点对点互联,X1的单向传输理论带宽即可达到2.5 Gb/s,用户可以根据实际需要将 PCIE链路配置为 X1、X2、X4、X8、X16等。

PCIE数据包在传输过程中要经过事务层,数据链路层及物理层。采用类似网络分层的思想,不同之处在于PCIE体系中的各个层都是采用硬件逻辑来实现。事务层是PCIE架构的上层,其主要功能是接收、缓冲和分发事务包TLP(Transaction Layer Packet)。TLP通过使用 I/O、存储器 、配置和消息事务来传递信息。数据链路层是保证可靠正确的数据传输,主要负责链路管理与数据完整性相关的功能,包括错误检测与改正,装配和拆解数据链路层包DLLP。物理层是PCIE协议的最底层,为设备链路提供物理支持,分为逻辑子块和电气子块。逻辑子块完成对数据包的合成分解、加扰和去扰、8 bit/10 bit编码和10 bit/8 bit解码、并串转换和串并转换;电气物理层负责对每路串行数据差分驱动的传输与接收及阻抗匹配[1-2]。

1 采集系统简述

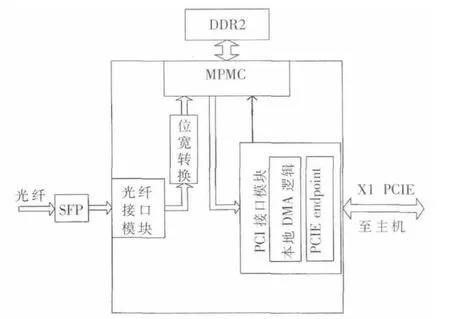

本文采用CCD相机的分辨率为2 352×1 728,灰度级别为 8 bit,帧频为 31 F/s,产生的数据量为 120.2 MB/s,则PCIE接口采用X1通道就可以满足带宽需要。采集系统的具体结构如图1所示。

图1 采集系统设计图

XC5VFX70T是Xilinx公司VIRTEX系列的一款具有5 328 KB RAM资源、内嵌3个PCIE硬核和16个可配置的高速串行收发器 GTX,速率可达 6.5 Gb/s,采用 CML电平标准,在系统中和SFP模块无缝连接。该芯片在系统中主要实现高速数据的接收和缓存,以及数据的实时采集[3-4]。

光纤信号通过光纤接口模块和位宽转换,数据被写入 DDR2中,DDR2分为 A、B两个独立的存储区。当 A储存区写满时,将数据写入PCIE接口模块的TX_FIFO中,这时DMA控制器发送中断给主机,主机会准备好接收缓存区,并将缓存区首地址告知DMA控制器,开始DMA传输,将数据写入到主机内存中,同时将采集的数据写入B存储区中。同理,当B存储区中的数据被写满时,也通过同样的方式写入主机的内存中。主机内存中的数据通过SATA总线被写到SATA硬盘并记录下来。DDR2采用交叉缓存工作,以保证高速数据流的不间断采集。

2 功能模块设计

2.1 光纤接口模块逻辑设计

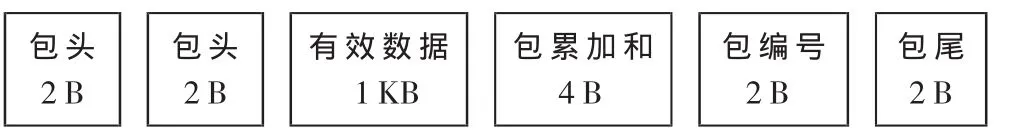

光纤接口模块分为GTX和包数据解析两个部分。光纤信号经GTX核后,输出16 bit位宽的并行数据和相应的K字符信号。根据K字符信号提取数据包。包数据解析根据自定义的协议进行数据包解析,得到帧头标志、帧尾标志、有效图像数据和附加信息等。附加信息是一组固定长度的双字组合,含有图像相关的一些信息,如大小、位数、编码方式等[5-6]。图2所示为自定义协议包。

图2 自定义协议包

包头和包尾作为数据包的起始和结尾标志,包长用于指示发送数据的有效长度,包累加和用于包内有效数据字节的统计,包编号用于统计发送的数据包有无丢失。帧头标志、帧尾标志、有效图像数据和附加信息等则放在有效数据中。

2.2 缓存模块

本文的DDR2控制器MPMC采用NPI接口,设计有2个NPI接口分别用于读写操作。一个是用于存储光纤的输入数据,另一个用于输出内存数据到PCIE接口。这样可以避免传输过程中内存的访问仲裁,提高系统的传输效率。

本文光纤接口模块输出的数据宽度为16 bit,而采用的NPI接口的数据宽度为64 bit。所以需要对原始数据进行位宽转换后才能进行后续处理。位宽转换模块根据需要将数据宽度从16 bit转换为64 bit。

2.3 PCIE接口模块设计

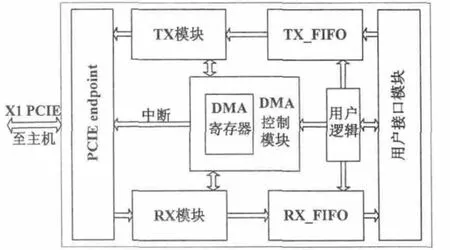

PCIE接口模块主要是实现主机PCIE总线与采集卡之间的通信。为了实现基于PCIE的DMA传输,需要设计以下8个模块[7-8],具体PCIE接口模块设计如图3所示。

图3 PCIE接口模块设计

图3中各个模块的作用如下:

(1)PCIE硬核:对外与其他PCIE设备通信,对内与TX和RX模块进行数据传输。

(2)TX模块:将待发送的数据和DMA寄存器中的信息填充到事务包TLP中,以并行的方式传输给PCIE硬核,实现PCIE写操作状态。

(3)RX模块:将接收的事务包TLP解析,根据TLPs的包头信息,将数据写入DMA寄存器。

(4)缓存:匹配FIFO两边不同传输速率的数据流,缓存待处理的数据和提高数据的传输效率。

(5)DMA控制模块:DMA寄存器是由发送寄存器、中断寄存器等构成。发送寄存器用于接收和存放主机内存写请求的DMA信息,主要为内存写请求地址寄存器及写长度寄存器、写包数寄存器。中断寄存器是存放中断产生的原因,为辨别何种中断提供依据。

(6)用户逻辑:一方面用户逻辑通过DMA控制模块向主机发起DMA传输中断,设置DMA传输的长度;另一方面控制数据的输入,保证TX_FIFO不会溢出,数据不会丢失。

(7)用户接口模块:提供简单的数据通道和控制信号通道。

3 DMA传输的逻辑设计与实现

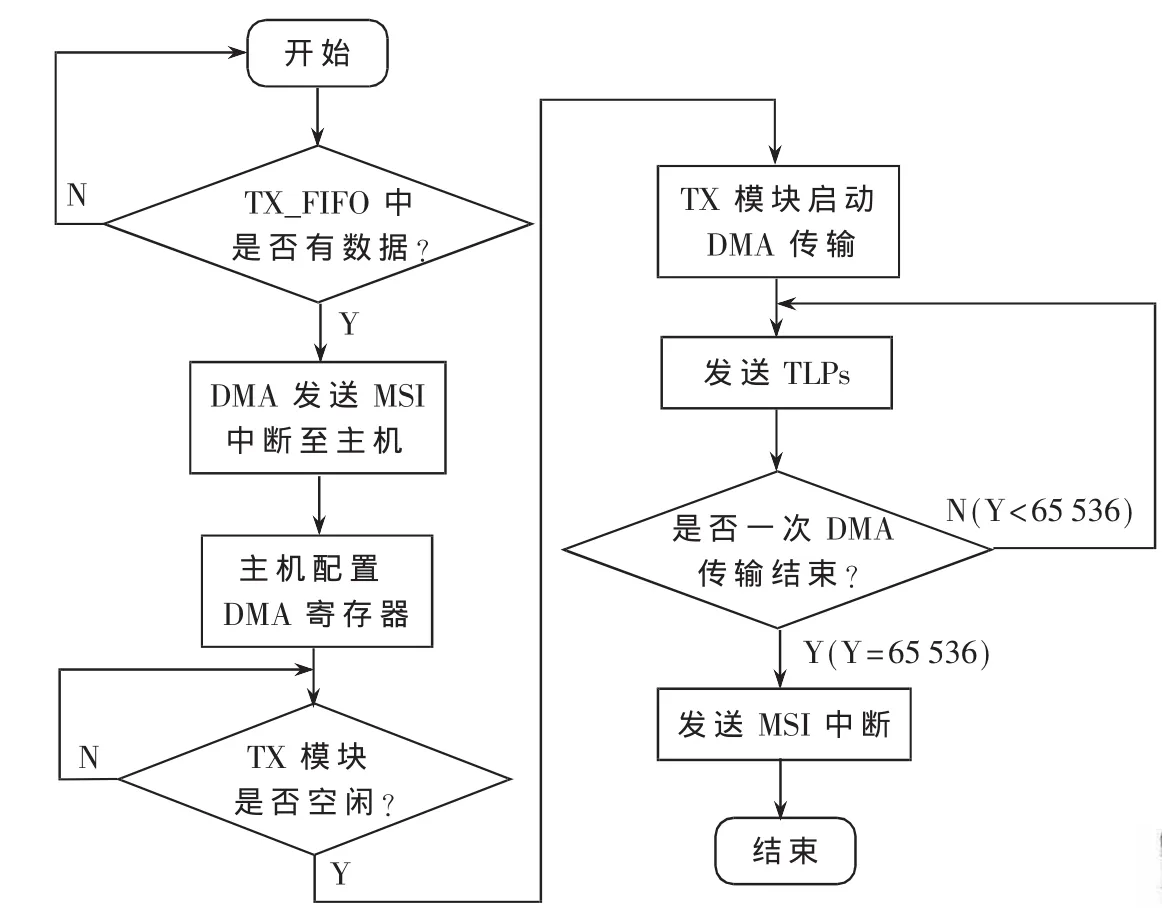

3.1 DMA写操作的设计与实现

首先用户逻辑检测到TX_FIFO中有需要传输的数据,这时用户逻辑通过DMA控制器发送MSI中断,请求DMA传输。主机响应中断,配置DMA寄存器,TX模块启动DMA传输,TX模块向TLP包加载信息,包括了控制字段、地址字段、数据长度字段以及数据字段等。当一次DMA传输结束后,向主机发送DMA传输结束的中断,这样一次完整的DMA写操作就完成了。具体流程图如图4所示,TX模块和PCIE硬核之间采用64 bit并行传输,在本文中一个TLP的载荷是128 B,一次DMA操作要进行65 536次包传输,则一次DMA写操作就传输了8 MB的数据量,PCIE写操作状态机是在TX模块中实现。

图4 DMA写操作流程图

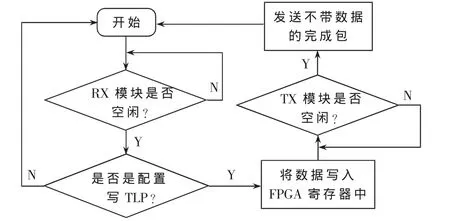

3.2 DMA寄存器配置的设计与实现

在本文中,DMA寄存器配置是通过配置写操作来实现的,当主机接收到DMA控制器的中断请求后,主机将正确填充对TLP包头的各个字段,并且将 32 bit的配置数据放在包头的后面发送给FPGA,FPGA通过解析TLP包获得配置信息,DMA控制器发送一个不带数据的完成包。接收和解析配置数据包是在RX模块中实现,发送完成包是在TX中实现。具体流程图如图5所示。

图5 DMA寄存器配置流程图

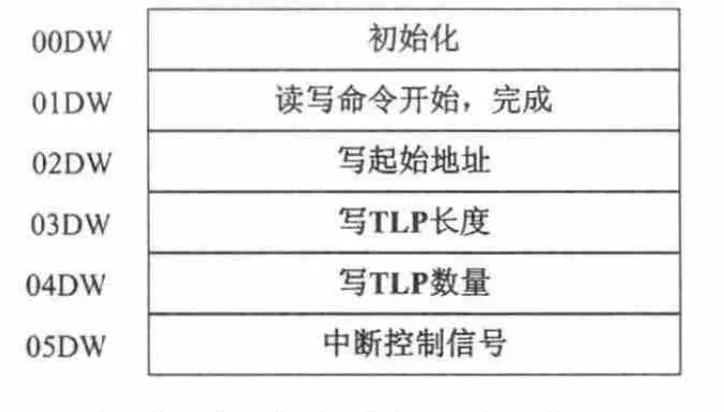

图6是DMA控制寄存器的设计图,初始化寄存器的Byte0用于DMA传输复位。1DW的Byte0用于读开始,Byte1用于读完成,Byte2用于写开始,Byte3用于写完成;2DW用于存放主机写入的缓存首地址;3DW用于存放一个TLP包携带的有效数据量;4DW用于存放一次每次DMA传输发送的TLP包数量;5DW的Byte0用于指示FPGA请求DMA传输,Byte1用于指示DMA传输结束。

图6 DMA控制寄存器的设计图

4 功能验证与性能测试

本文PCIE硬核采用X1通道,最大的理论传输带宽为2.5 Gb/s。使用ChipScope对DMA写操作进行了验证,具体时序如图7所示,trn_td是FPGA向主机发送的数据,trn_tsof_n为低时,表示TLP包的第一个64 bit数据;trn_teof_n为低时,表示TLP包的最后64 bit数据,这时trn_trem_n为0X0F,则说明最后一个64 bit只有高32位有效。传输一个TLP包大约需要108个时钟周期,采用125 MHz的采样频率,一个TLP包有效载荷为128 B,则可得出在X1的配置下,DMA的传输速度大约为141.3 MB/s。

图7 DMA写操作流程

在主机中添加计时程序分别对1次、5次、10次DMA写操作进行计时测速,速度大约为138 MB/s,低于ChipScope测得的速度,这主要是由于中断响应和配置DMA寄存器延时造成的,测试结果如表1所示。

表1 PCIE接口传输速度

本文针对高速光纤图像实时采集的需要,设计了一种基于PCIE的采集系统。经实际测试,系统运行稳定可靠。采用X1的PCIE总线接口,DMA写操作速度大约为138 MB/s,满足光纤图像实时记录的带宽要求。如果实际需要更高的采集带宽,可以参考本文设计,将PCIE接口设计为X4或X8,以实现更高的采集性能。本设计具有通用性,可被移植于其他内嵌有PCIE硬核及串行收发器GTX等资源的 FPGA平台。

[1]BUDRUK R,ANDERSON D,SHANLEY T.PCI Express系统体系结构标准教材[M].田玉敏,等译.北京:电子工业出版社,2005.

[2]PCI-SIG.PCI express card electromechanical specification Rev 1.0a[Z].USA:PCI-SIG,2003:5-33.

[3]Virtex-5 FPGA RocketIO GTX transceiver v2.1 user guide[Z].USA:Xilinx,2011.

[4]使用用于PCI Express设计的集成端点模块实现点到点连接[Z].USA:Xilinx,2007.

[5]孙科林,周维超,吴钦章.高速实时光纤图像传输系统的实现[J].光学精密工程,2011,19(9):2228-2235.

[6]缪露鹏,涂晓东,张新颖.光纤适配卡数据总线的研究与实现[J].光通信技术,2011(1):8-10.

[7]汪精华,胡善清,龙腾.基于FPGA实现的高速串行交换模块实现方法研究[J].电子技术应用,2010,36(5):37-40.

[8]何琼,陈铁,程鑫.基于FPGA的DMA方式高数数据采集系统设计[J].电子技术应用,2011,37(12):40-43.