基于PD SOI工艺的高压NMOS器件工艺研究*

2013-12-05廖聪湘陈正才

徐 静,廖聪湘,陈正才

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

SOI技术减弱的短沟道效应、较为陡直的亚阈值斜率等优点在功率器件应用中并没有显示出较大的优势,SOI技术所能提供的较理想的隔离结构却被广泛应用于功率器件的设计中[1~6]。而在SOI器件中,由于隐埋氧化层的存在阻止了表面电力线的再分布,因此,SOI器件中表面电力线的非均匀性导致了器件能承受的最大电压的降低[7]。通常会采用漂移区的线性梯度掺杂来提高器件的击穿电压[8]。

2 常规结构及剖面浓度仿真

常规体硅20 V高压结构采用的是P阱工艺,通过NHV注入将P阱反型形成N-漂移区来提高器件的耐压能力。这种结构的P阱浓度通常比较低。而对于PD SOI工艺,由于N+源漏区已经连接到埋氧层,会存在背栅开启。

因此,对于抗辐射PD SOI工艺,P阱都是采用表面低掺杂浓度,靠近埋氧高掺杂浓度,以便提高背栅开启,加强抗辐射能力。这样的P阱工艺使得常规高压结构移植到SOI材料上较难实现。以下是对抗辐射PD SOI工艺上的常规体硅高压结构进行的仿真研究。

仿真采用的SOI材料是全注入剂量的SIMOX SOI材料,顶层硅膜厚度为205 nm,埋氧层厚度为375 nm,衬底为P型硅,(100)晶向,电阻率为20 Ω.cm。仿真采用的结构是常规体硅20 V高压结构,剖面结构示意图如图1,其中虚线是仿真的剖面位置。

图1 常规结构仿真剖面示意图

工艺仿真流程如图2所示,NHV形成是本研究仿真的模块,主要目的是通过P注入将P阱反型掺杂,形成N-漂移区。

图2 工艺仿真流程图

仿真的浓度是在漂移区的位置上,具体见图1的虚线框。具体工艺是通过NHV注入将P阱反型掺杂,形成耐高压的漂移区。仿真时保持P阱掺杂浓度不变,通过改变NHV注入P的能量和剂量来实现将P阱反型,具体仿真条件及对应浓度分布结果如表1所示。

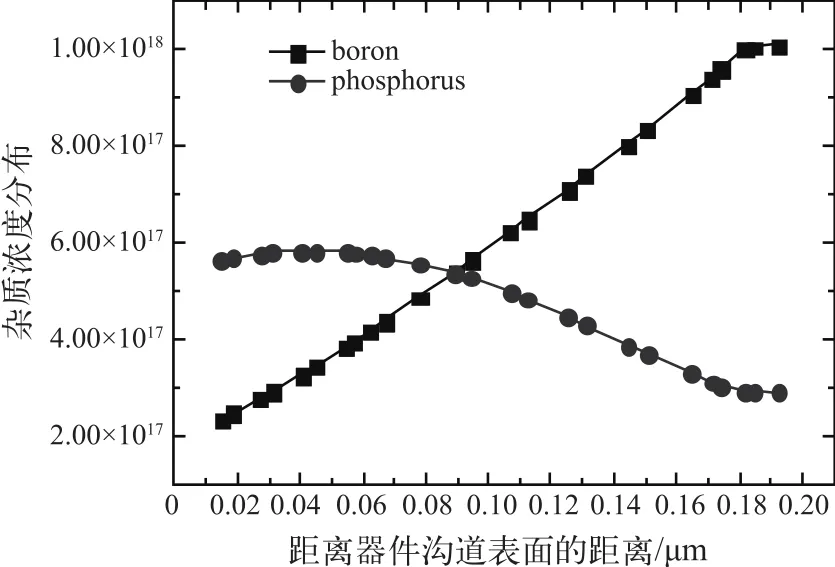

如图3~图5所示为仿真条件1~3下漂移区P阱boron杂质和NHV注入phosphorus杂质的浓度分布图,横坐标为距离器件沟道表面的距离,纵坐标为杂质浓度分布。由于SOI工艺平台上P阱浓度是表面浓度低(约为2×1017/cm-3),靠近埋氧的boron浓度高(约为1×1018/cm-3),因此,必须用高能量和高剂量的P注入才能将P阱反型。

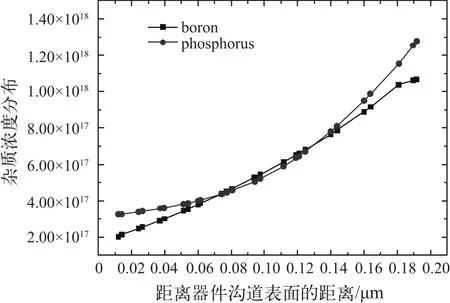

从图3~图5可以看出,注入能量在150 KeV以内,都没有办法将P阱反型掺杂。从图6~图7可以看出,P注入能量在180 KeV,剂量在6×1013以上能将P阱反型掺杂。

表1 NHV注入条件仿真表

图3 仿真条件1下漂移区杂质分布图

图4 仿真条件2下漂移区杂质分布图

由于工艺限制,图1所示结构中P的注入能量不能达到180 KeV,因此,只采用了表1中仿真工艺条件1~3。工艺流片出来测试器件没有特性,证实仿真结果中的猜想,由于P的注入能量不能达到180 KeV,无法使该结构中漂移区中P阱反型,因此,无法形成高压NMOS器件。

图5 仿真条件3下漂移区杂质分布图

图6 仿真条件4下漂移区杂质分布图

图7 仿真条件5下漂移区杂质分布图

3 新结构及工艺流片

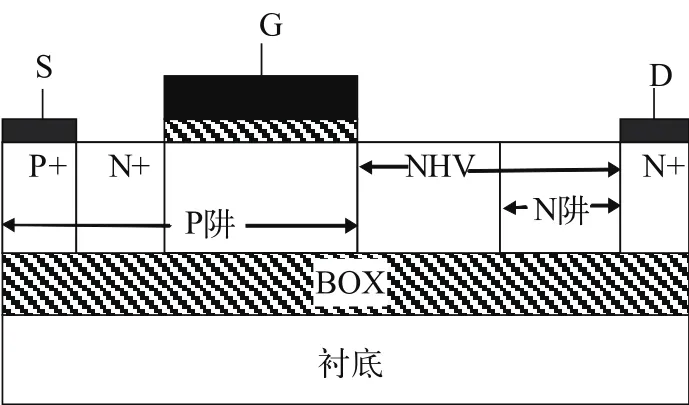

鉴于抗辐射PD SOI工艺的特殊性,设计了一种新结构的高压器件结构,如图8所示,新结构漂移区下没有P阱。

图8所示结构由于漂移区没有P阱而是N阱,因此漂移区P注入对能量和剂量没有那么高的要求,实际工艺时注入能量为40 KeV,注入剂量为6×1012。工艺流片后器件特性良好,转移特性ID-VG如图9所示,输出特性ID-VD如图10所示。

图8 新结构剖面示意图

图9 新结构转移特性

图10 新结构ID-VD输出特性

4 结果与讨论

常规体硅高压器件结构是做在P阱上,通过漂移区的反型掺杂注入,形成N-漂移区。这种器件结构简单,容易与低压器件集成,但是也有其局限性——其P阱浓度不能太高,而对于SIMOX材料抗辐射PD SOI工艺来说,其特有的背栅开启效应会影响总剂量辐射能力,因此,其P阱都是采用倒置掺杂,即表面浓度低,靠近埋氧层浓度高,以便提高背栅开启,采用常规体硅的高压管结构需要用高能量和大剂量的P注入工艺将漂移区的P阱反型掺杂,这在工艺上是不容易实现的。采用漂移区没有P阱的新结构在工艺上更容易实现。因此,对于本所顶层硅膜只有205 nm的SOI材料PD工艺,采用图8所示的新结构能取得较好的效果。

[1] Ratnam, P. Novel silicon-on-insulator MOSFET for highvolatage integrated circuits [J]. Electronics Letters, 1989,25(8)∶ 536-537.

[2] O’Connor, J M, Luciani V K, Caviglia A L. High voltage DMOS power FETs on thin SOI substrates [C]. Proc.IEEE SOS/SOI Technology Conference, 1990, 167-168.

[3] Nakagawa A, Yasuhara N, Baba Y. Breakdown voltage enhancement for devices on thin silicon layer/silicon dioxide film [J]. IEEE Trans.Electron Devices, 1991, 38(7)∶ 1650-1654.

[4] Yasuhara N, Nakagawa A, Furukawa K. SOI device structures implementing 650 V high voltage output devices on VLSIs [C]. IDEM Tech. Dig., 1991, 141-144.

[5] Lu Q, Ratnam P, Salama C A T. High voltage siliconon-insulator(SOI)MOSFETs [C]. Power Semiconductor Devices and ICs, 1991, 6-39.

[6] Valeri S J, Robinson A L, Erskine J C. A silicon-on-insulator circuit for high- temperature, high-voltage applications[C]. Proc. IEEE International SOI Conference, 1991,60-61.

[7] 黄如,张兴,等. SOI CMOS技术及其应用[M]. 北京:科学出版社,2005, 372.

[8] Shengdong Zhang, Johnny K O Sin. Numerical Modeling of Linear Doping Profiles for High-Voltage Thin-Film SOI devices[J]. IEEE Transactions on electron devices,1999,46(5)∶ 1036-1041.