一种基于FPGA的真随机数发生芯片设计

2013-11-27余菲,赵杰

余 菲,赵 杰

(深圳职业技术学院 电子与通信工程学院,广东 深圳 518055)

随着电子信息技术的发展,随机数发生芯片或电路在集成电路领域的应用越来越广泛[1].随机数按照发生机理的不同,分为伪随机数和真随机数2种[2],其中伪随机数是按照一些算法,结合随机种子发生的一系列难以发现规律的数字;而真随机数是利用一些物理学效应,发生的没有数学规律的一系列数字.根据目前的信息技术发展现状,伪随机数越来越难以应对“不可预测性”的要求,所以真随机数的发生和应用变得越来越重要[3].因而,真随机数发生芯片或集成电路芯片上真随机数发生电路成为了研究热点.FPGA技术作为进年来发展较快的一种技术,内部集成了各种逻辑门等电路结构,可以方便地实现多种电路进而完成芯片设计,利用FPGA芯片资源,构建随机数发生电路是一种很好的实现真随机数发生芯片的方案[4].

真随机数的发生必须依赖物理过程,在电路中真随机数的发生也必须依赖电路中具有随机特性的一些物理过程,利用电路中的结构,典型的片上真随机数的发生方法有3类[5-6],包括直接放大法、振荡采样法和离散时间混沌法.由于FPGA芯片内部的资源为数字电路结构以及少量和数字电路直接相关的模拟电路单元结构,因此在PFGA无法利用直接放大法发生随机数.目前利用FPGA构建片上真随机数发生器典型的随机源主要有2种:一种是利用FPGA的逻辑门构建高速数字电路振荡器;另一种是利用模拟PLL(锁相环)电路发生的数字时钟信号上面的抖动构建随机量.对比这2种方法,前者的方法较为简单,但是对芯片电路性能要求很高,电路功耗很大,芯片寿命很短.而基于模拟PLL(锁相环)电路的方法[7],一般结构复杂,设计难度高,由于锁相环的随机Jitter具备一定的规律性,所以随机性不理想.

1 基于FPGA的真随机数发生芯片设计

1.1 随机数发生芯片系统设计

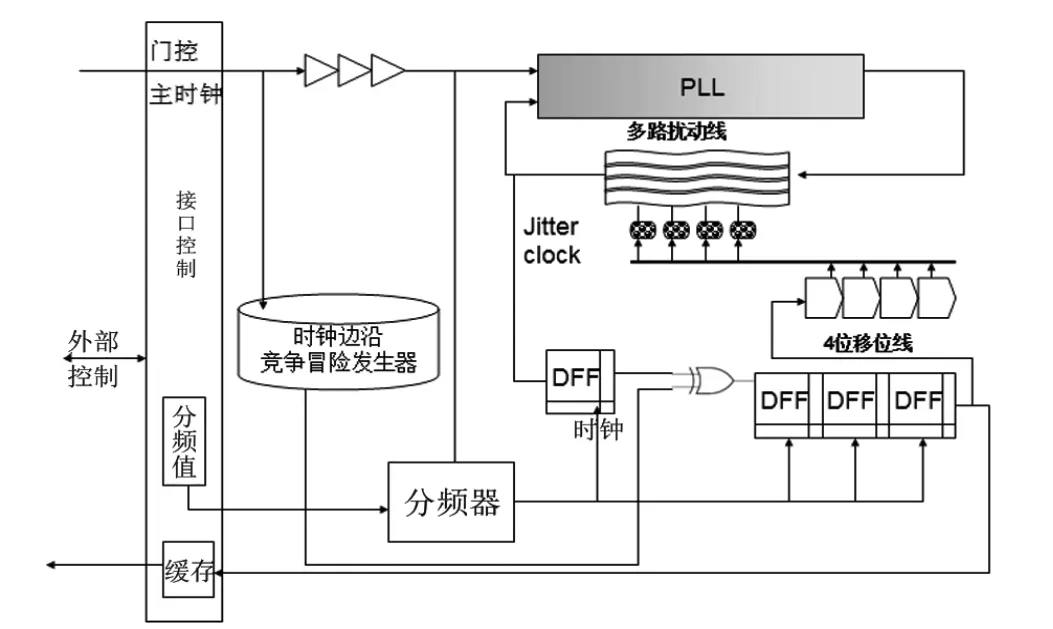

考虑到基于 PLL的随机数产生芯片的产生效果比较好,结合FPGA数字电路中的另外一种离散时间混沌法,基于组合逻辑竞争冒险产生随机数办法,本文设计的FPGA的随机数发生芯片的系统结构如图1所示,主要由接口控制模块、PLL锁相环回路模块、竞争冒险发生器模块3个部分组成.其中接口模块负责和外部电路通信,给芯片提供系统时钟,分频器数值和处理随机数序列的发送;系统主时钟是门控时钟,由外部控制器决定是否产生随机数序列.

系统时钟经过一个延迟线后送入 PLL作为参考时钟,PLL的输出时钟本身就具有一定的随机Jitter,在本文所述的芯片电路中,PLL的输出又被送入一个多路扰动线,而多路扰动线是由前面产生的随机数序列进行控制扰动的大小,这样相当于产生了一个随机的扰动.经过随机扰动的信号被送入锁相环的“反馈信号”端,这样锁相环就很难完成锁定,导致Jitter加大,随机性大大变强.利用系统时钟进行分频,使用分频时钟对锁相环输出的含有很大Jitter,而且经过随机扰动的高速时钟进行采样,采样的结果具有良好随机性的数据.

利用系统时钟,采用特殊的时钟边沿竞争冒险发生器结构,能在系统时钟的边沿时刻构建具有大量的毛刺信号,利用这种信号和前面锁相环产生的随机数进行异或门的逻辑,其结果将是形成一个在时钟边沿时刻具有大量毛刺的随机数信号.再利用三级 D触发器消除前面可能出现的亚稳态,就会得到良好的随机数序列.最后把这列随机数序列送入扰动线控制器做随机扰动控制,同时接口控制器模块进行处理并输出给芯片外部.

1.2 竞争冒险发生器设计

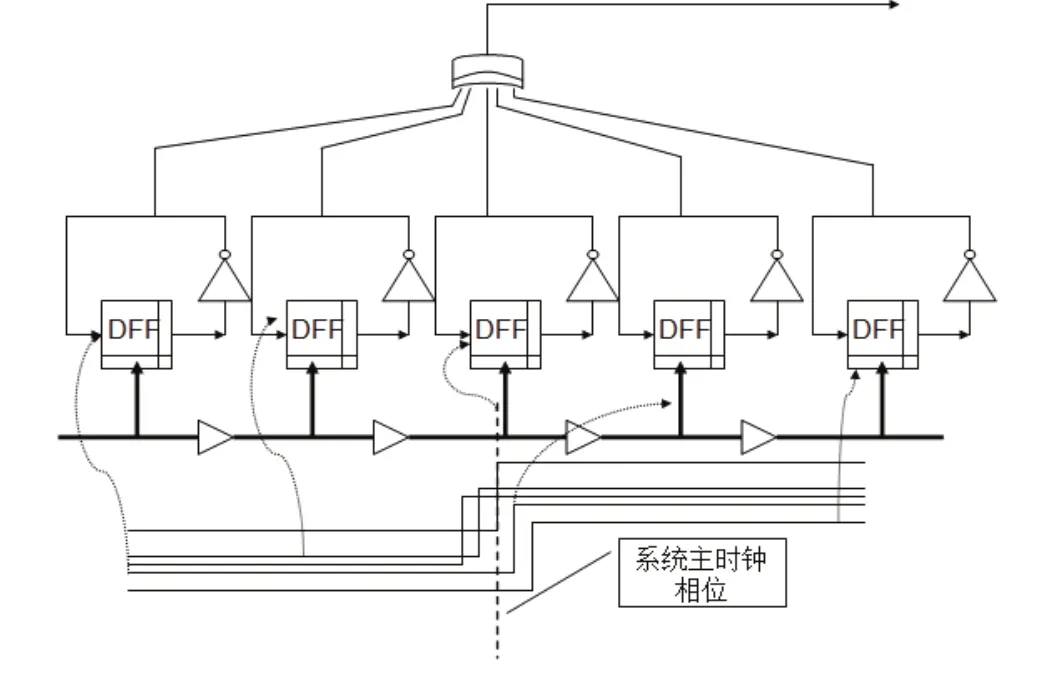

组合逻辑的竞争冒险是由于组合逻辑门电路的输入变化不同步造成的,一般地组合逻辑竞争冒险并不具备任何随机性,这些组合逻辑的竞争冒险会带来输出的毛刺,而这些毛刺是有一定规律的.但是,如果组合逻辑竞争冒险产生的毛刺发生在D触发器数据端,并且发生在D触发器的采样边沿,那么采样的结果就具备一定的随机性了.本文设计的时钟边沿竞争冒险发生器如图2所示,该竞争冒险发生器采样最难以消除冒险的异或门逻辑作为最终的组合逻辑电路,利用5个自翻转的D触发器作为组合逻辑的输入.通常地,D触发器的初始值是一个上电时候的随机量,所以,该电路产生随机数的种子是随机的.要想在系统时钟的边沿造成组合逻辑的冒险毛刺,需要让5个D触发器在时钟边沿附近跳变.我们设计了一个时钟延迟线,利用延迟线,让中间的D触发器的时钟和系统时钟的相位一致,前2个D触发器的时钟相位依次超前一点,而后面2个D触发器又依次落后系统时钟相位一点.这样产生的组合逻辑输入信号,均在系统时钟跳变的边沿进行变化,这样输出信号在系统时钟边沿产生大量的小毛刺.

1.3 多路扰动线设计

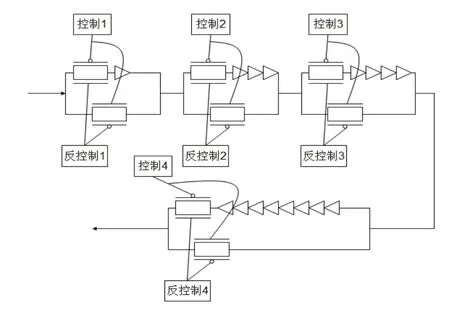

多路扰动线是增加PLL相位Jitter的有效办法,加上随数控制的多路扰动器对电路的扰动完全不可预测,大大加强了Jitter的随机效果.多路扰动线如图3所示.

图1 随机数发生芯片系统结构

图2 时钟边沿竞争冒险发声器结构

图3 多路扰动器结构图

在多路扰动器线当中,一共有4个控制位.每个控制位可以控制选择一条延迟线或者是一条导线进行扰动,利用FPGA中的CMOS传输门来实现两路选择的效果.4个控制位的延迟线按照2n作为延迟的权值,第一个延迟线延迟为1个时间单位,第二个延迟线的延迟为2个时间单位,第三个延迟线的延迟为4个时间单位,第四个延迟线的延迟为8个时间单位.这样,随着4个控制位的数据不同,整条延迟线可以排列组合出0~15个时间单位的延迟效果,对PLL的反馈进行随机的扰动.

1.4 接口模块设计

接口模块是整个芯片和外部连接的桥梁,负责对系统主时钟进行门控处理,接受外部控制信号,对输出数字进行组装等工作,其结构如图4所示.

在接口模块电路中有2组寄存器,一个寄存器叫做“门控时钟控制”寄存器,代表是否启动随机数发生器的标志.如果该标志位为高电平,代表着将外部时钟送入随机数发生器芯片;如果该标志位为低电平,则表示截断整个时钟,随机数发生芯片停止工作.另外一个寄存器存储着分频计数器的数值,用来作分频电路分频的数值标准.这2个寄存器都在外部“写指令”控制信号下工作.此外,接口电路一个很重要的作用是对单个的随机数进行拼接,按照8位一组的要求进行输出.因为,在该模块中设计了一个8位移位寄存器,配合这个寄存器,有一个8位的计数器,每当写满了8个寄存器后,产生一个“写出数”的控制信号.

图4 接口模块电路结构

2 真随机数发生芯片的仿真与效果分析

2.1 PLL随机效果的仿真

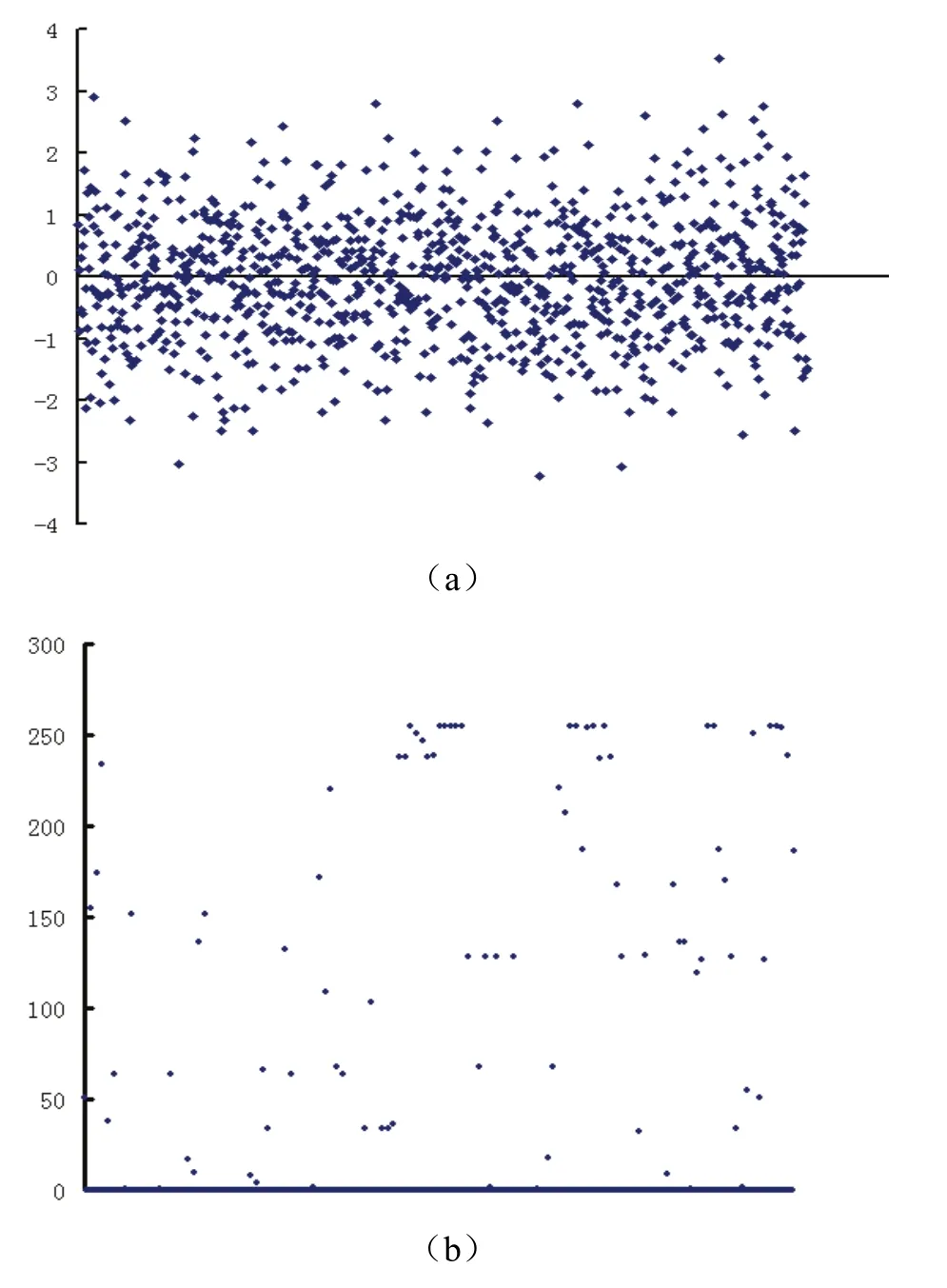

为了验证PLL的随机性效果,本文利用Matlab进行了仿真,首现利用Matlab产生1000个满足高斯分布的随机数,用来仿真 PLL的 Jitter.该组随机数分布如图5a所示,其中高斯分布的随机Jitter的取值范围是0~4之间,纵坐标表示随机值,横坐标表示随机点的序号.

按照一般地锁相环电路规律,Jitter的平均值应该为 5%~10%,假定 FPGA芯片中能达到的 Jitter为 5%,据此我们设计的随机扰动线的扰动时间设为5%~10%.给Jitter增加了随机扰动之后,再使用DFF对数据进行采样,然后得到取值范围为0到255的8位随机数.最后,产生的随机数如图5b所示,纵坐标代表8位随机数的数值,横坐标代表随机数的序号.可见这些点的随机性良好,而且概率分布是平均分布,不再是高斯分布.

图5 高斯分布随机Jitter(a)和产生随机数的效果(b)

2.2 竞争冒险发生器的效果分析

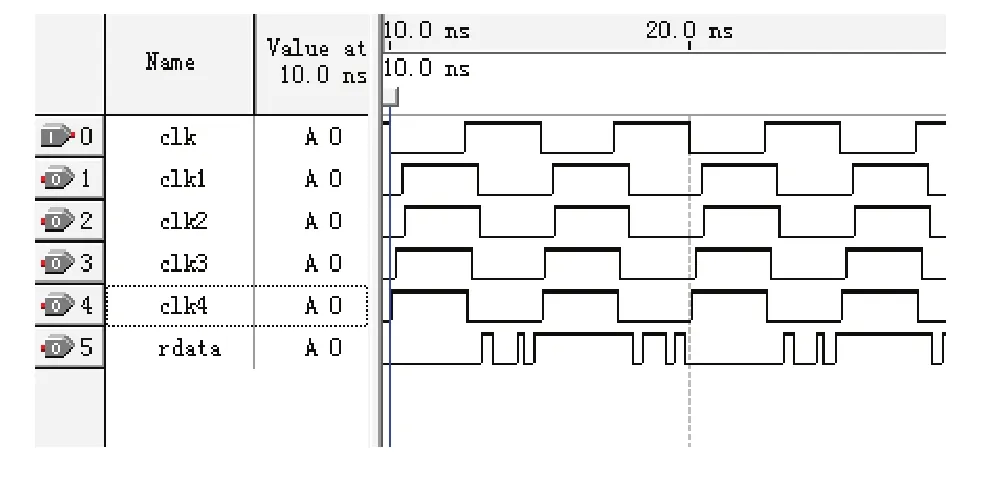

利用Quartus II 可以对FPGA内部的电路用Verilog语言进行建模,并能对其效果进行仿真.利用Verilog对竞争冒险发生器仿真的波形如图6所示.由图6可见,在时钟的边沿附近,组合逻辑竞争冒险发生器的输出“rdata”产生了大量的毛刺,这些毛刺在后面利用D触发器采样的时候会产生不确定的采样效果,达到增强最终随机性的目的.

图6 竞争冒险波形仿真

3 结 论

利用 FPGA实现了一个随机数放大芯片的设计,利用FPGA实现该电路具有方便快捷的好处.经过理论分析和1000个随机数点的仿真,证明本文所述的真随机数发生器具有极其良好的随机性,而且随机数按照平均概率分布.利用Quartus II工具的仿真证明了组合逻辑竞争冒险器有着良好的加强随机性的能力.而利用PLL和门控时钟技术可以有效地降低系统的功耗和稳定性,增加芯片的寿命.本文所述的可变频随机数产生系统可以根据外部系统的要求改变随机数产生的速度,使设计的真随机数发生芯片具有较好的性能和应用价值.

[1] 杜学峰,武杰.基于FPGA的任意分布高速伪随机数发生器[J].中国科学技术大学学报,2003,36(9):990-994.

[2] 张润捷.一种基于 FPGA实现的真随机数发生器[J].中国集成电路,2008,114(11):52-55.

[3] 王莱,刘松强.真随机数发生器的设计和实现[J].核电子学与探测技术,1998,18(6):452-455.

[4] 祝爱民,石春和,董良东,等.基于FPGA 高斯白噪声发生器的设计与实现[J].火力与指挥控制,2009,34(7):119-121.

[5] Craig S,Petrie J,Alvin C. A noise-based IC random number generator for applications in cryptography[J].IEEE Transaction on Circuits and Systems, 2000,47(5):234-236.

[6] 霍文捷,刘政林,陈毅成,等.一种基于 FPGA 的真随机数生成器的设计[J].华中科技大学学报(自然科学版),2009,37(1):73-76.

[7] 周干民,杨盛光,蒋召宇,等. 一种基于锁相环的真随机数发生器[J]. 电子与信息学报,2007,27(7):1152-1156.