数字系统的现代软件设计

2013-11-01左智成

左智成

(中原文化艺术学院,郑州450002)

数字系统的硬件设计目前有两种方法,即传统系统硬件设计和现代系统软件设计.电子工程师因其使用设计方法的不同,被划分为硬件工程师和软件工程师.他们专心于自己的设计事业,很少从事跨界工作,尤其软件从业人员更是如此.随着微电子技术的迅猛发展,特别是计算机技术的日新月异和硬件描述语言(Hardware Description Language,HDL)的开发和使用,这种传统的、难以逾越的沟界被打破,电子工程师无论是硬件设计人员还是软件从业者都已经开始使用HDL语言设计趋于合理、符合生产要求的数字设备.而且,使用HDL语言设计数字系统与传统方法设计相比,优势极为突出,可降低设计难度,在设计的每一步都可进行仿真,能及早发现问题,缩短开发周期,且文件资料归档方便,可节省大量的人力物力资源,它是硬件设计领域的一次变革,对系统硬件的设计将产生巨大的影响[1].

1 数字系统硬件的传统设计方法

在未开发计算机辅助设计系统的年代,电子工程师均采用传统的设计方法设计数字系统[2].这种数字系统的设计方法是在“人工”的基础上形成的,具有以下几个主要特征:

1.1 自底向上的设计方法

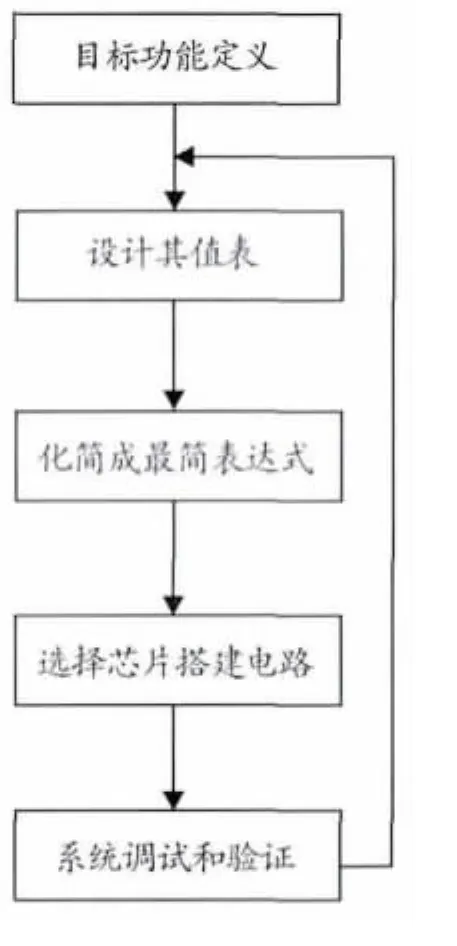

自底向上的硬件电路设计方法的主要步骤是:当给定生成目标后,设计真值表,使用卡诺图或逻辑代数化简成最简表达式,然后采用“搭积木”的方法选择功能固定的标准芯片实现生成,最后调试和验证并修改相关设计.上述设计方法也称自下向上的设计方法,它充分体现在各功能模块的电路设计中,其设计流程如图1所示.

1.2 通用逻辑元器件是构成系统的主要部件

在传统的硬件电路设计方法中,设计者总是根据系统的实际需要,力求选择市场上能买到的逻辑元器件来搭建所要求的逻辑电路,从而实现系统的硬件设计.对于由微处理器及相应硬件组成的系统中,部分系统的硬件功能可以用软件来实现,这在某种程度上简化了系统硬件电路的设计,但是这种选择通用元器件构成数字系统的模式并未改变.

图1 传统设计流程

1.3 在系统设计硬件搭建的后期进行仿真和调试

仿真和调试在传统的数字系统设计方法中,通常是在完成系统硬件搭建以后才能进行,这是因为进行仿真和调试的工具一般为系统仿真器、逻辑分析仪和示波器等.它们只有在数字系统硬件构成后才能使用.因此,在设计过程中潜伏存在的问题只能在后期被发现,这就对系统设计人员提出了更高的要求,一旦出现失误,系统设计将存在较大缺陷,那么极有可能推倒进行重新设计,使得设计周期大为延长[3].

1.4 电路原理图是设计的主要文件

在使用传统的硬件设计方法进行数字系统设计并调试完结后,得到的硬件设计文件主要是由若干张电路原理图集合形成的文件.在这些集合文件中详细说明了各逻辑部件的名称及相互间信号的依赖关系,是用户今后使用和维护系统的依据.对于较为简单的小系统,这种电路原理图只要几张、几十张至几百张即可,但如果系统庞大,硬件结构相对复杂,那么这种原理图文件可能有几千张、几万张乃至几十万张,这就给原理图文件的归档、阅读、修改和使用带来了极大的困难,对系统的使用和维护带来了极大的不便.

2 现代的系统软件设计方法

随着微电子技术的迅猛发展,大规模、超大规模专用集成电路(ASIC、Application Specific Integrated Circuit)的研制和使用,各ASIC制造厂商为了提高研、发、产效益,缩减研发周期及增强研发成果的继承性,均开发了适于各自目的的系统设计软件,即HDL语言.现时使用最广泛的是美国国防部研发的VHDL(Very High Speed Integrated Circuit,HDL)和Verilog公司的Verilog硬件描述语言[4].利用HDL语言设计数字系统有以下几个特征:

2.1 自顶向下的模块化设计方法

自顶向下的模块化设计方法,就是从系统的总体功能要求出发,先进行整体规划,然后确定设计方案,自顶向下逐步将设计指标分解到各模块,再进行模块和细节设计,最后实现数字系统的总体设计.这种设计方法将数字系统的设计自顶向下分成三步进行.

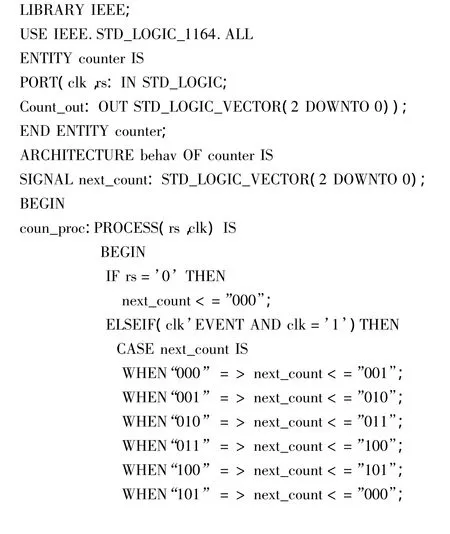

第一步是行为描述(顶部描述).它是对整个数字系统顶部功能的描述,建立系统的数学模型.通过对系统顶部功能的数学模型描述、仿真来发现设计中早期存在的功能不完善、行为描述不准确的问题.这一阶段主要考虑数字系统的整体结构及工作过程是否达到系统总体功能的预设要求,不考虑行为描述实际的操作和算法实现.下面以六进制计数器为例说明以行为方式描述的工作特性.

以上VHDL语言程序勾画出了六进制计数器的输入、输出引脚和内部计数过程的计数状态变化时序及关系.这实际上是计数器工作状态的描述.当该程序仿真通过以后,说明六进制计数器模型是正确的.

第二步是寄存器传输(Register Transfer Level,RTL)描述,也称数据流描述.第一步顶部描述建立系统结构的数学模型因其程序抽象度高,难以直接映射到数字系统内部的具体逻辑部件结构,不便用硬件来实现.因此必须将数字模型方式描述的VHDL程序转化为数据流方式描述的VHDL程序.只有这样,才能求得系统的逻辑表达式,再进行下一步的综合.下面仍以六进制计数器为例,说明行为方式描述转化为RTL方式描述.

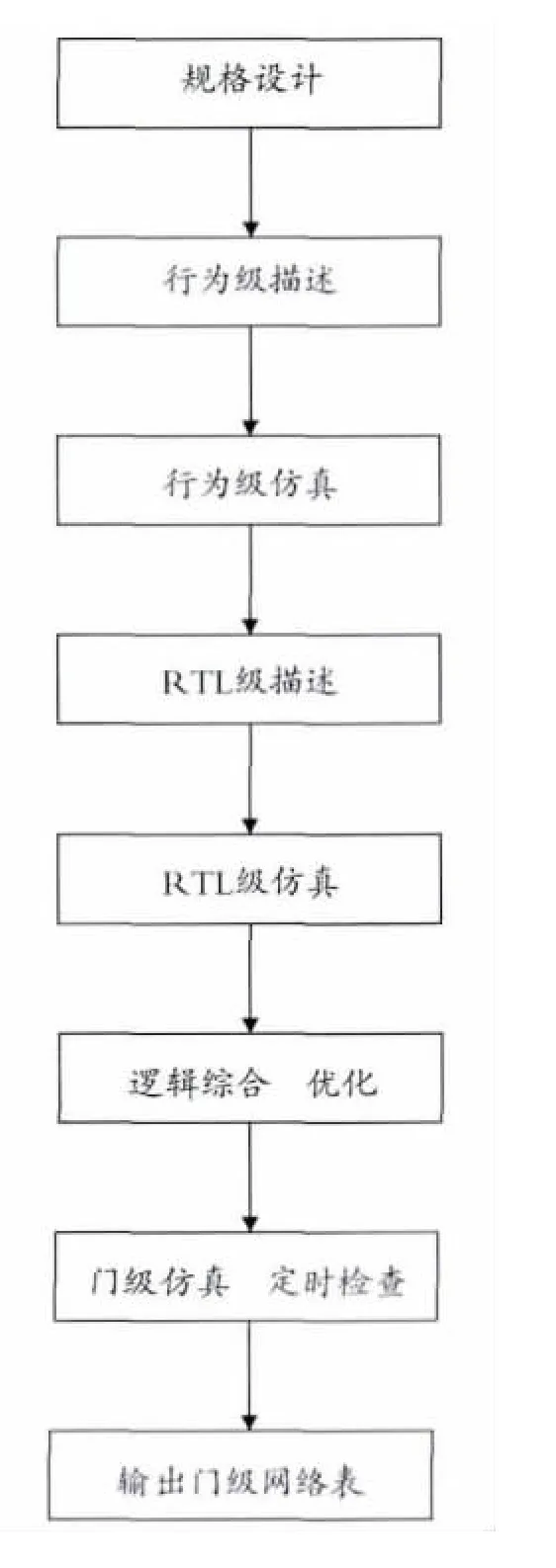

图2 自顶向下设计流程

在以上的RTL描述方式中,JK触发器、D触发器、与门和或非门都可以在库WORK.NEW.ALL中直接调用,且构造体直接描述了它们之间的连接关系.与行为方式描述相比,RTL描述更接近于实际电路的描述.

在数据流描述的源程序编写完成后,用仿真软件对该方式描述的源程序进行仿真.若仿真结果正确,就可进行第三步的逻辑综合.

第三步逻辑综合.逻辑综合的目的是用逻辑综合工具将数据流描述的程序转换成门级网络表,即用基本逻辑部件表示的文件.若需要,可进一步将逻辑综合的结果以逻辑原理图方式输出.这个逻辑原理图就相当于用传统方法设计的硬件电路,根据系统功能体系要求画出系统的全部逻辑电路原理图.以门级网络表为基础,对逻辑综合结果再次在门级电路上进行仿真,测试信号依存关系和定时关系.若都正常,那么数字系统的硬件设计就此成功完结.若这三步的某一步发现问题则都可随时返回上一步,查看源程序,寻找和修改出现相应错误的模块、进程或结构,然后继续下一步.

逻辑综合结束后,在最终完成硬件设计时,有两种选择:第一种是采用自动布线程序将逻辑综合的结果转换成相应的ASIC芯片的制造工艺,做出ASIC芯片;第二种是将结果转化成CPLD(复杂可编程逻辑器件)或FPGA(现场可编程门阵列)的编码点,而后写入对应芯片,完成数字系统设计.整个设计过程如图2所示.

2.2 系统设计合理化、体积微型化

如前所述,众多ASIC芯片制造商提供的软件均可支持或兼容HDL语言,所以,电子工程师在设计数字系统的硬件电路时,可根据硬件系统的需求,自行设计ASIC芯片或可编程逻辑器件.这终将会使数字系统的硬件电路趋于合理,体积大为缩小,走向微型化.

2.3 全过程仿真

从自顶向下的三步设计过程可以看出,仿真始终贯穿在系统硬件设计的各环节之中,即行为(顶部数学模型)仿真、数据流(RTL)仿真和门级(门电路原理)仿真.这就使在系统设计各个阶段存在的潜伏问题能被及时发现和更正.较之传统自底向上设计的后期仿真,自顶向下的三步设计最大限度地缩减了系统的设计周期,节省了大量的人力、物力资源.

2.4 系统的设计周期大为缩减

在传统硬件电路的设计方法中,电子工程师必须在设计前求得电路的逻辑表达式或真值表(或状态表),这是相当繁杂和困难的过程,尤其是在硬件系统较为复杂时更是如此.而用现代软件的设计方法设计硬件电路时,设计者无需得到逻辑表达式或真值表.例如六进制计数器,只要知道六进制计数器的6个计数状态就行了,而无需写出相关电路的逻辑表达式.这使硬件电路的设计愈来愈便利,难度也大为降低,缩短了硬件系统的设计周期,提高了设计效率.据有关资料统计,就此一项可使系统的设计周期缩短大约1/3 ~1/2[5].

2.5 HDL的源程序是设计的归档文件

如1.4所述,在传统硬件电路的设计中,电路原理图是最后得到的主要文件,而利用现代软件设计硬件电路时,得到的设计文件是HDL编写的源程序,需要时就可转换成电路原理图.用源程序作归档文件有以下优点:(1)资料量小,便于纸质保存.(2)继承性好.在设计任何硬件电路时,可利用现有文件中的进程和过程等程序.(3)可阅读性强.阅读理解源程序要比理解电路原理图容易一些.在源程序中能容易找出某部分电路的逻辑关系和工作原理.

3 结语

数字系统硬件设计的两种方法目前在实际工作中都有使用.传统的硬件电路设计方法已经沿袭使用了几十年,是广大电子设计者所熟悉和掌握的一种方法.但是,随着计算机技术日新月异、微电子技术的迅速发展,传统的设计方法已无法跟进现代技术的发展.一种崭新、采用现代软件语言设计的硬件电路方法正在蓬勃发展,它的出现使硬件电路设计的难度大为降低,设计周期大为缩短,节省了大量的人力物力,对硬件电路的设计产生了革命性的变化.

[1]侯伯亨,刘凯,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].第3版.西安:西安电子科技大学出版社,2009.

[2]文汉云,刘鹏,胡杰.数字逻辑与数字系统设计[M].北京:清华大学出版社,2012.

[3]谭会生,昌凡.EDA技术及应用[M].西安:西安电子科技大学出版社,2009.

[4]王金明.数字系统设计与Verilog HDL[M].第4版.北京:电子工业出版社,2011.

[5]朱志平.基于VHDL的交通管理器设计[J].渭南师范学院学报,2012,27(6):24-28.