高速串行通道的信号完整性问题分析

2013-10-27高晓宇杨龙剑

高晓宇, 杨龙剑

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

随着应用对于数据传输带宽和速率需求的不断增长,高速串行接口技术已替代传统并行接口技术成为高速数据传输的主流。PCI Express、SATA、Hyper Transport、InfiniBand、HDMI等众多高速串行接口标准被制订出来,广泛应用于通信、计算机、网络、消费电子等众多领域。如在计算机中,PCI Express已替代PCI在系统总线的主流位置,而SATA则替代 PATA在磁盘互连接口的主流位置。并且,高速串行接口的传输速率处于不断攀升之中。PCI Express 1.0在 2002年推出 1.0版规范时,速率为2.5 Gb/s。四年后,PCI Express 2.0升至5.0 Gb/s。2010年 PCI Express 3.0发布,速率再跃升至 8.0 Gb/s。数据信号的传输以如此高的速率运行,带来一系列信号完整性问题。这些问题在传统并行接口主导的时代因为信号速率较低而很少影响到数据的正确传输。而在高速串行接口互连设计中,理解互连通道的信号完整性问题并采取应对解决措施,将是设计成败的关键。

1 高速串行通道

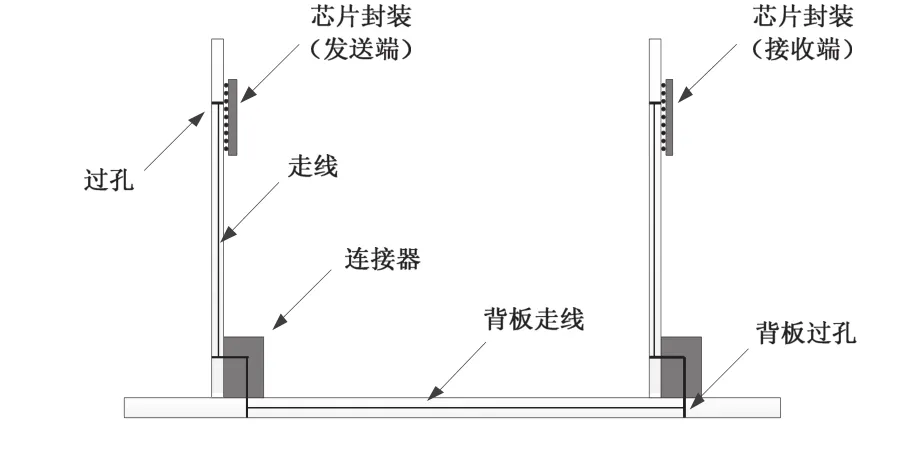

“通道”是指信号从发送端到接收端所经过的整个互连路径。如图1所示,在一个背板互连系统,高速串行信号的传输将经过芯片封装、印制板走线(传输线)、过孔、连接器、背板走线(传输线)等,它们共同组成高速串行通道[1]。

图1 背板互连系统的高速串行通道

2 损耗

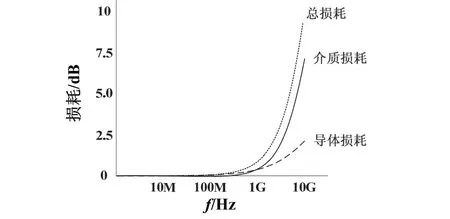

铜材质的互连部件,如传输线、芯片封装内部铜走线、连接器引针等,都会对信号的传输产生损耗。损耗的产生根源主要是两种:导体损耗和介质损耗[2]。

导体损耗是指由于铜导体自身固有的电阻而导致的信号能量损失。信号流经传输路径,而路径各部分(走线、过孔、引脚等)并非理想的导体,具有电阻,其实质就如同负载,必然分去一部分信号幅度,导致接收端的信号幅度减小。从这个基本原理的角度来看,导体损耗似乎只跟导体的几何尺寸有关。然而事实上,由于趋肤效应的存在,高速串行信号的高频率特性是导体损耗的主要成因。直流和低频率信号(MHz以内)沿着导体传输时,电流是均匀分布于导体内部的,而在高频率的情况下,尤其是1 GHz以上时,在越贴近导体表面的地方,电流分布越密,越贴近导体内部中心的地方,电流分布越少。这称为趋肤效应。频率越高,趋肤效应越明显。因为运载电流的导体成分减少,趋肤效应在效果上等同于电阻增大,将带来更大的导体损耗。

介质损耗是指信号在介质中的能量损失。传输线由信号路径、返回路径及两者之间的介质组成。理想情况下,认为介质是彻底绝缘的,电阻为无穷大,外加信号电压时没有电流流过,因此不会消耗能量。但实际上,现实世界中的任何介质材料都是有电阻率的。信号传输时在介质两端形成的电压将产生电流流过介质,造成能量损耗。介质损耗也是随着频率的上升而增加。

图2是对一段20 cm长、8 mil宽PCB走线的损耗测量结果。可以看到,频率超过1 GHz后,导体损耗和介质损耗大大增加。

数字信号是宽频带信号,其频谱分布与信号的上升时间(上升沿的爬升时间)有很大关系。信号比特速率在10 Mb/s、100 Mb/s这样的量级水平时,上升时间一般在 1 ns以上,信号中的高频分量(1 GHz以上)在整个频谱中占的比重很低,即便损耗严重,也不影响信号波形的基础框架。所以,低速信号的损耗对波形影响有限,可以忽略。而高速串行信号是快速跳变的信号,其上升时间通常在100 ps以内,含有大量高频成分。信号经过一定距离的传输后,高频成分的损耗将远大于低频成分,信号波形可能发生严重畸变。

图2 传输线导体损耗、介质损耗与频率的关系

图3是一个5 Gb/s的高速串行信号经过不同长度的传输线后在接收端观察的眼图。10 cm传输线的眼图状况很好。随着传输线长度增至 20 cm、40 cm,损耗导致的信号衰减越来越严重,眼图的“眼高”越来越小。在传输线长度80 cm时,信号衰减相当厉害,“眼高”仅为16 mV,这根本无法满足接收端识别信号状态的门限条件,接收必然出错。

图3 不同长度的传输线对高速串行信号的衰减情况

3 反射

反射自来就是影响信号完整性的关键因素。即便是在33 Mb/s、50 Mb/s、100 Mb/s这样较低速率等级的互连系统中,反射问题也足以导致信号接收失常。所以,与损耗不同,反射问题在并行接口技术主导的时代就已得到了充分重视,是信号完整性分析和设计的重要内容。

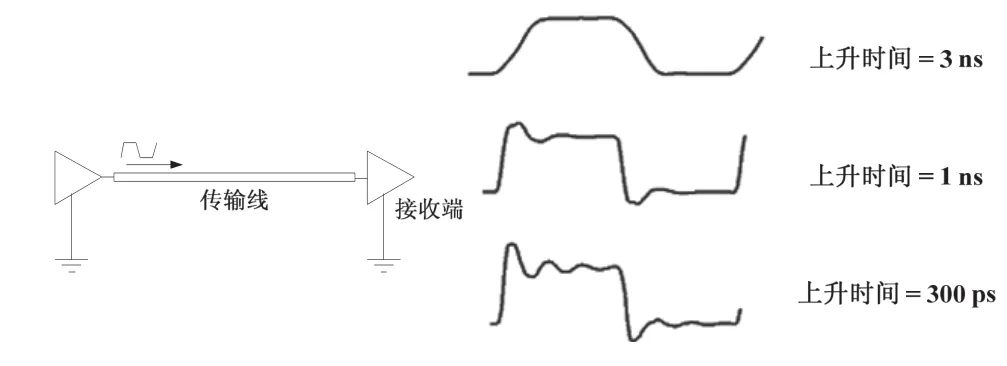

高速串行接口工作速率高达1 Gb/s以上,无疑,反射的可能危害性远比在并行互连接口中更大。但同样需要指出的是,信号的上升时间才是更本质的因素,而非信号的比特速率。图4是对比特速率相同而上升时间不同的三个信号经过同一段传输线后在接收端的仿真波形比较。可以看到,上升时间越快,反射导致的波形“振荡”越严重。

图4 不同上升时间的接收端反射波形

反射发生的根源在于信号传输通道的阻抗不连续[3]。发送端、引脚、走线不均、过孔、连接器、接收端,凡是阻抗发生改变的地方,都是通道上的阻抗不连续点,信号流经时便发生反射,造成波形失真。传统上,板级互连系统主要采用两种手段抑制反射:①均匀传输线;②端接匹配。均匀传输线采用精确的印制板走线阻抗设计,确保走线的阻抗连续无改变,消除在走线上发生的反射。端接匹配则是通过端接使信号发送端或接收端的阻抗与传输线相匹配,消除在通道两端发生的反射。

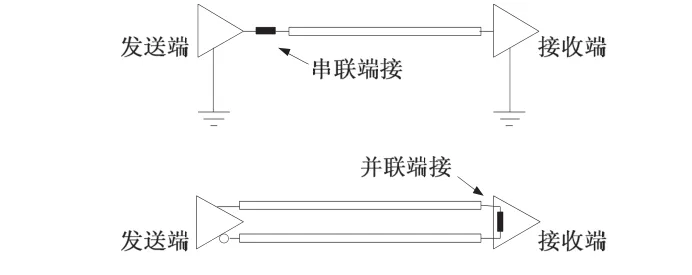

高速串行互连设计仍需要这两个手段来消除反射。但是,在设计实践中的侧重点却有所变化。在端接匹配的运用方面,并行接口互连设计大多在发送端进行串联端接,这种端接方式并不消除信号在到达接收端后产生的第一次反射,而是消除反射信号回到发送端后的第二次反射。这样,波形总是叠加了第一次反射的影响。虽然从设计的期望来讲,反射应当消除得越早越好,但在并行互连的设计实践中,串联端接所达到的反射抑制效果已经足够。而在高速串行互连设计中,信号的上升时间达到100 ps以内,反射的危害大大增加,尽早消除第一次反射非常必要。所以,高速串行互连系统最有效的端接匹配方式是在接收端进行并联端接,如图 5所示。事实上,目前大多数高速串行接口集成电路芯片已将这个接收端并联端接电阻集成于内部,板级电路设计通常已不必再考虑端接。

图5 串联端接和并联端接

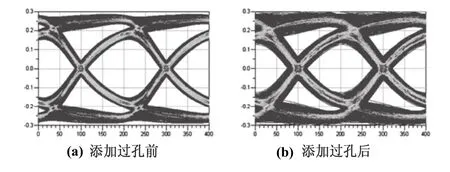

在“均匀传输线”方面,高速串行互连设计所遇到的挑战也比并行互连大得多。因为信号上升时间非常快,在过去可以被忽略的一些细微环节现在也可能导致信号接收的失常,设计必须从整个通道的层面综合考虑,减少累积反射影响。比如,在Mb/s速率级别的并行互连通道的设计中,走线时布下的一、两个过孔属于阻抗不连续点,但它对整个信号完整性的影响是比较细微的,很难成为最终导致信号接收失败的根源因素。而在高速串行通道中,一、两个过孔带来的反射效应也是可观的。图6是某高速串行通道的传输线上添加两个过孔前后的接收端眼图仿真对比。可以看到,增加两个过孔后,“眼纹”更加杂乱不清,“眼高”降低,抖动也明显增加,这些都是反射增加所导致的后果。

图6 过孔带来的反射效应对眼图的改变

4 串扰

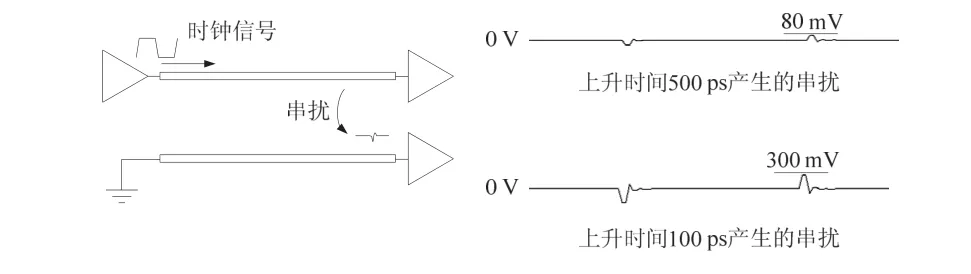

由于电磁场的作用,在一个通道上传输的信号会部分地耦合到邻近的其他通道上,从而改变其他通道上正在传输信号的波形,这是串扰发生的根本原因。在Mb/s速率级别的并行互连系统中,串扰是一个被热烈议论的信号完整性问题,但在设计实践中,很少遇到完全因为串扰而导致的信号接收失败。这是一个同损耗类似的因素,它对信号的危害程度在高速串行互连系统中变得严重起来。其根源仍在于上升时间。比较周期相同但上升时间不同的两个时钟信号在同样的传输线系统中串扰到同一个相邻信号通道引起的波形改变,如图7所示。可以看到,上升时间为500 ps的时钟信号在相邻通道上产生的串扰幅度仅为80 mV,而上升时间提高到100 ps后,串扰幅度大增至300 mV。

图7 不同上升时间的串扰对比

5 新的分析方法

高速串行接口使用串行器/解串器(SerDes,Serializer/Deserializer)进行信号收发,并且大多采用8B/10B编码技术进行线路编码[4-5],完全不同于传统并行接口的传输机制。这种差异使得对高速串行通道的信号完整性分析需要采用不同于传统并行设计的新方法。

(1)眼图分析

眼图是对高速串行信号按“位”连续捕获并叠加波形所形成的测量结果,是高速串行信号波形最直观的反映。评判眼图是否合格的最直接的方法就是使用眼图模板。每一种高速串行接口标准(PCI Express、SATA、Hyper Transport、InfiniBand、HDMI等)都会在其规范中发布眼图模板,该模板规定了正确接收数据所需要的信号眼图规格,包括信号能够出现的区域和不能出现的区域。将实测的信号眼图与标准眼图模板相比较,信号是否合格便一目了然。

(2)抖动分析

抖动是指信号在时域上的跳变位置相对于其理想位置的偏差。在高速串行互连系统中,损耗、反射、串扰等各种因素都会造成信号的抖动。由于高速串行信号采用接收端时钟恢复的传输机制,抑制抖动对于信号的正确接收至关重要。通过对抖动进行分析,可以掌握抖动背后的根源因素,便能对症下药,在高速串行通道的设计中进行改进。

(3)码间干扰(ISI)

高速串行信号是一位一位地进行发送的,如果由于传输通道的限制,导致信号位的波形“拖尾”、“展宽”等超越了一位的宽度,进入到相邻位甚至附近其他位的区域,从而对其他位的状态造成影响,这便是码间干扰现象[6]。对ISI进行评估是分析高速串行信号完整性的一个重要手段。

6 结语

高速串行接口技术的应用给高速串行通道的设计带来了全新的挑战。由于信号的上升时间变得越来越快,损耗、反射、串扰等导致的信号畸变越来越严重。只有深入理解各个根源因素造成信号畸变的原理,并清楚它们在低频与高频时表现的不同程度,才能正确把握高速串行通道设计的关键要点。

[1]张昌骏.高速串行设计的强大工具——眼图医生[J].电子测试,2009(06):78-83.

[2]BOGATIN E.信号完整性分析[M].李玉山,李丽平译.北京:电子工业出版社,2005:201.

[3]张华.高速互连系统的信号完整性研究[D].福建:东南大学,2005:18.

[4]刘智,宁红英,王普昌.一种新的 8B/10B编码电路设计[J].通信技术,2009,42(07):60-61,84.

[5]李玉伟,潘明海.8B/10B编码对高速传输的影响分析[J].信息安全与通信保密,2011(03):41-43.

[6]伍建辉.无线通信系统的码间干扰抑制方法研究[J].通信技术,2007,40(12) :123-125.