基于FPGA的八通道高速ADC的时序设计*

2013-09-28徐立升徐根倩马正欣宋早迪蒋秀波周冬冬秦智超

徐立升,徐根倩,马正欣,宋早迪,蒋秀波,周冬冬,秦智超

(北方信息控制集团有限公司车载信息系统研发部,南京210000)

1 引言

随着电子技术的发展,军用无线数传设备向着小型化、低功耗化的方向发展。无线数传设备需要在面积有限的印刷电路板上实现多路采样的需求,采用多通道高速ADC可以满足设备微型化的要求[1]。Analog Device公司的AD9252集成了八路模数转换,输出采用高速串行DDR(Double Data Rate)方式,Xilinx公司高端 FPGA中集成了片同步模块[2],利用这一模块可以满足串并转换的时序要求,正确地恢复出并行数据。但是低端的FPGA中无此模块,考虑到成本问题,系统采用兼容低端FPGA设计方法,利用FPGA内部的寄存器来实现串并转换,通过内部时钟管理模块DCM(Digital Clock Management)、位置约束等来满足时序要求。

AD9252是一款八通道,14 b的模数转换器,最高采样率为50 Msample/s;内部集成了采样保持电路,输出采用高速串行DDR方式,输出端包含一个输出数据时钟(DCO)用于捕获数据和一个帧使能信号(FCO)表示新的数据位的开始;接收端通过串并转换,恢复并行数据。

2 设计方案

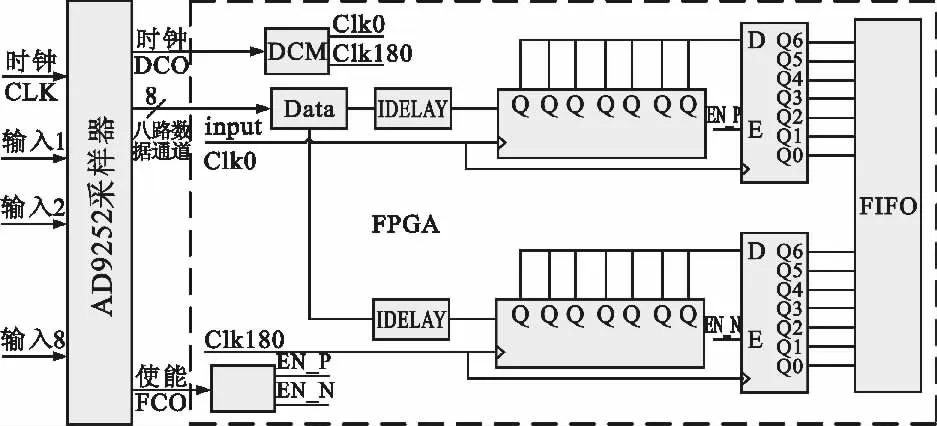

AD9252高速串行数据转换成并行数据是通过FPGA内部寄存器来实现。帧使能信号FCO生成上下沿使能信号,通过多个寄存器来寄存串行数据,下一个帧使能信号FCO到来之前,取走并行数据,完成串并转换,具体实现如图1所示。

图1 FPGA解串的示意图Fig.1 Deserializer based on FPGA

图2 FPGA内部全局时钟网络示意图Fig.2 Global clock network of FPGA

采样时钟为40 MHz的系统,输出时钟DCO为40×14/2=280 MHz,串行输出采用DDR方式,数据率为 280×2=560 Mb/s,数据的时间窗口仅为1.79 ns,除去数据上升沿、下降沿时间和抖动时间,数据的有效窗口长度变得更小。采用FPGA内部寄存器完成串并转换时,寄存器之间的布线延迟时间与数据有效窗口时间相当,要实现系统稳定的工作,必须满足数据的建立保持时间的要求。FPGA内部的时钟资源、时序约束以及位置约束为此实现提供了基础。

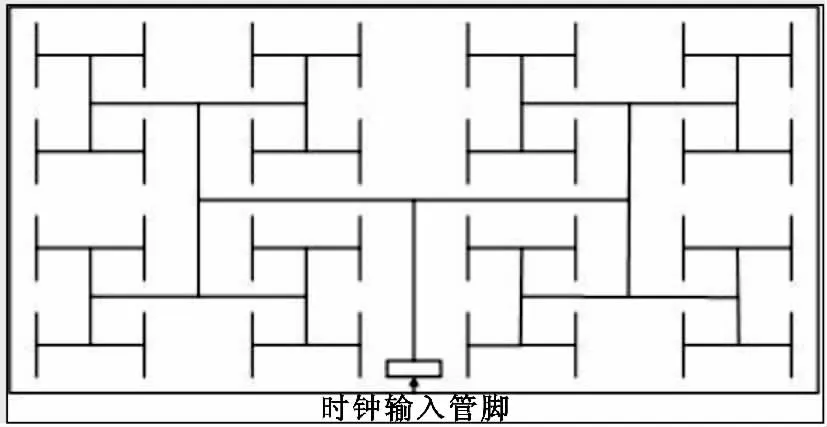

图2显示了FPGA内部全局时钟资源为一树形结构,保证了全局时钟到达逻辑单元的布线长度相同。时钟接入全局时钟资源通过全局缓冲器来实现[3],如下所示:

BUFG CLKG(.I(clk0_p),.O(clk0))

BUFG CLKG(.I(clk180_n),.O(clk180))

FPGA内部布线前的全局时钟与触发器的关系可通过FPGA开发工具Planahead查看,全局时钟连接到触发器的关系如图3所示。

图3 布局布线前全局时钟网络图Fig.3 Gobal glock network of pre-map

3 时序设计

FPGA内部时序设计通过时钟管理模块DCM、位置约束和延迟单元IDELAY来实现。

3.1 DCM的时钟设计

AD9252输出280 MHz时钟通过FPGA全局输入引脚进入FPGA内部的DCM,产生两个相差180°的时钟,分别用来寄存上下沿数据。DCM除了倍频和分频时钟功能外,还能补偿时钟进入FPGA到DCM布线延迟和时钟经过全局网络到达触发器的延迟,保持时钟与数据原来的时序关系。

为了保证时钟到达各个触发器的延迟相同,DCM产生的两个时钟接入FPGA内部的全局时钟网络,全局时钟网络是一种全局布线资源,保证时钟信号到达各个目标逻辑单元的延迟基本相同。FPGA内部全局时钟资源网络如图2所示。

FPGA内部高速时钟必须加入周期约束来保证时钟布线满足时序要求,约束语句如下所示:

TIMESPECclk_p=PERIOD"clk0"280 MHz HIGH 50%

TIMESPECclk_n=PERIOD"clk180"280 MHz HIGH 50%

约束语句保证了全局时钟周期为280 MHz,占空比为50%,高电平有效。

FPGA内部布局布线后,通过FPGA editor工具查看全局时钟布线资源,如图4所示。

3.2 位置约束

设计时加入位置约束,将串并转换的触发器放在FPGA内部同一物理区域,缩短输入数据与触发器之间的布线长度,减小布线延迟时间。图4显示通过位置约束,触发器被约束在FPGA内部同一位置区域,并且靠近ADC输入引脚。

3.3 时序调整模块IDELAY

串并转换时,FPGA内部寄存器必须在数据稳定时间内寄存数据,才能正确恢复并行数据。AD9252输出的数据与时钟的时序关系经过布线的延迟后,不能满足建立保持时间的要求,需要重新调整。通过FPGA内部集成的IDELAY来实现时序微调整[3]。

IDELAY是FPGA内部集成的可编程绝对延迟单元。IDELAY具有64个tap的可调延迟单元,每个tap延迟时间为78 ps,可以实现5.0 ns的延迟。时序设计时改变tap值,来调整数据和时钟的时序关系。IDELAY模块需要一个参考时钟才能正常工作。

4 时序分析

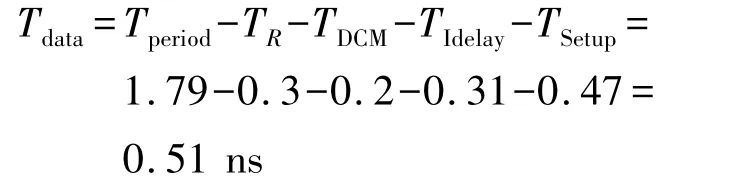

采样时实现在数据眼图中心采样极为重要,对于560 Mb/s数据速率,数据周期 Tperiod=1.79 ns,实际传输过程中很多因素会减小数据有效时间宽度。数据时间宽度分析对设计具有指导作用。

ADC输入时钟抖动值为0.34 ps,相对于数据周期,此抖动时间可以忽略。数据的上升沿和下降沿的典型值TR=0.3 ns,时钟经过FPGA的DCM引入的抖动值TDCMJ=0.2 ns,IDELAY模块的参考时钟通过DCM倍频后提供,参考时钟引入抖动为TIdelayJ=0.31 ns,FPGA内部触发器的建立时间 TSetup=0.47 ns(数据要先于时钟0.47 ns达到稳定)。数据的有效窗口宽度为

5 测试

高速接口的FPGA程序是在Xilinx ISE12.4编译环境下实现的,仿真采用ISE自带的仿真工具ISim12.3,功能验证和时序验证通过 Chipscope Pro12.3捕获波形实现。

5.1 功能测试

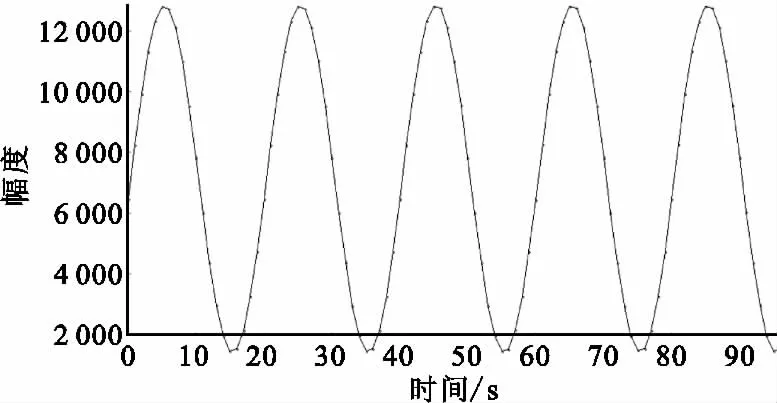

功能测试时采用信号发生器产生一定频率的正弦波接入ADC的输入端,后端通过FPGA的在线逻辑分析仪Chipscope来分析采集的数据信号,如图5所示。

图5 正弦信号的采样波形Fig.5 Sampled waveform of sine

图5 中重建的信号波形和频率与信号产生器的相同,验证了串并转换时序设计的正确性。

5.2 时序测试

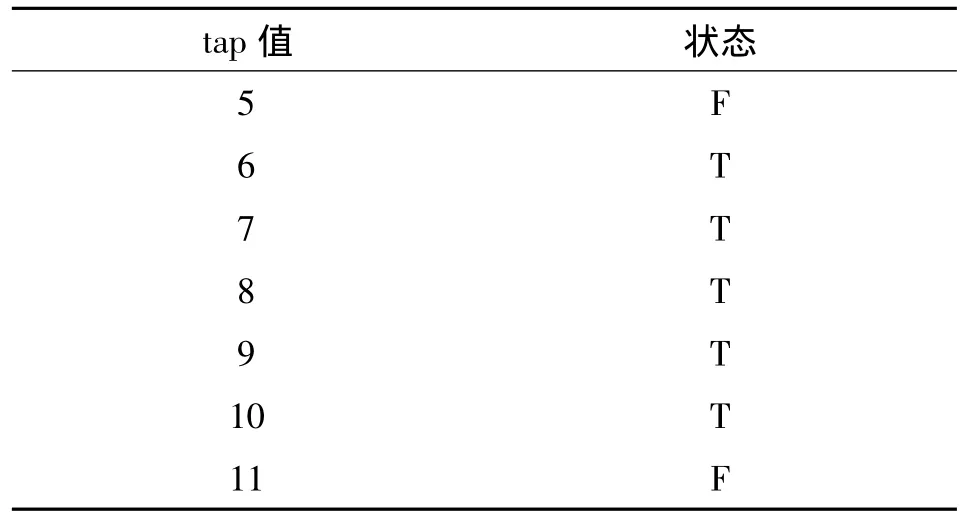

时序分析主要测试IDELAY模块中多少个tap值可以使系统稳定工作,计算出数据眼图宽度。测试结果见表1。

表1 一路ADC的tap值测试结果Table1 The result of tap

从测试结果可以看出数据眼图宽度为5 taps,时间宽度为

眼图测试宽度与分析的眼图宽度相差0.12 ns,时序分析时并未考虑到PCB布线和FPGA内部布线的抖动时间,此外IDELAY模块中每个tap都会引入相应的抖动时间,这些都会减小数据眼图宽度。

6 结论

本文综合利用FPGA内部时序约束工具和FPGA内部的组成单元——寄存器实现了高速串行数

据的正确解串,避免了高端FPGA内部集成的片同步模块在低端FPGA中无法实现的问题;同时,克服了片同步模块要求解串通道的信号线需要布局在FPGA相邻区域的限制,提高了系统设计的灵活性,降低了系统设计的成本。测试结果表明,该高速接口可以稳定工作。此外,此系统还可以应用在其他高密度集成系统中,提高了系统的复用性。

[1]刘进军.采用CPCI总线的通用高速数传接收机[J].电讯技术,2012,52(10):1644-1647.LIU Jin-jun.A general high-rate data transmission receiver base on CPCI bus[J].Telecommunication Engineering,2012,52(10):1644-1647.(in Chinese)

[2]李燕春.高速信号处理终端设备的设计[J].电讯技术,20011,51(8):66-69.LI Yan-chun.Design of a high speed signal processing terminal equipment[J].Telecommunication Engineering,20011,51(8):66-69.(in Chinese)

[3]马力科.一种高速全数字卫星信号模拟源平台[J].电讯技术,20013,53(3):318-322.MA Li-ke.A high-speed digital satellite signal simulator platform [J].Telecommunication Engineering,20013,53(3):318-322.(in Chinese)