AES密码算法的FPGA实现与仿真﹡

2013-09-17张慧霞赵建平李晓丽

张慧霞, 赵建平, 李晓丽, 路 娜

(曲阜师范大学 物理工程学院,山东 曲阜 273165)

0 引言

由于缺乏保密措施,使得电话窃听,密码泄露等事件不断发生,严重威胁到个人的隐私、军事、商业机密、地区和国家的信息安全。因此,AES(Advanced Encryption Standard)加密算法已成为信息安全领域研究的热点。AES算法是美国国家标准技术研究所(NIST)于 2001年宣布其成为取代DES的新一代数据高级加密标准[1]。该算法在实现方面具有设计简单、安全性高、速度快等优点,而且AES算法的128位的密钥比DES的56位密钥在破解所花费的时间上强1021倍[2]。如果加解密使用同样的密钥,安全性得不到保证。文中所采用不同的(相关的)加解密密钥,把加密密钥扩展模块的最后一轮子密钥作为解密密钥的初试密钥,这样可以加强通信安全性,保密性。

1 AES算法描述

AES是一个迭代型分组密码算法,分组长度为128 bit,有三种可选密钥长度分别是 128 bit,192 bit,256 bit。不同的密钥长度对应的迭代循环次数rN分别是10轮,12轮,14轮。由于其操作都是以字节为基础的,因此把中间变量和密钥都分成 16个字节。加密数据按照从上到下、从左到右构成4×4以字节为元素的状态矩阵(State)。加密过程是首先使待加密的明文与初始密钥异或(AddRoundKey),然后进行 10次圈迭代变换。每圈包括字节替换变换(SubBytes)、行移位变换(ShiftRows)、列混合变换(MixColumns)、轮密钥异或变换(AddAdd RoundKey)四步变换[3],最后一圈不含列混合操作。解密运算是与加密过程完全相反的逆运算。文中以数据长度和密钥长度均为128 bit为例进行讨论。

2 AES算法的实现

2.1 AES算法的整体设计

该设计的整体内部结构框图如图1所示,该结构由加密模块、解密模块、控制模块、FIFO组成。其中AES加密模块包括字节替换模块(SubBytes)、行移位模块(ShiftRows)、列混合模块(MixColumns)、轮密钥异或模块(AddRoundKey);解密模块包括逆字节替换模块(invSubBytes)、逆行移位模块(invShiftRows)、逆列混合模块(invMixColumns)、逆轮密钥异或模块(invAddRoundKey)。加密过程的数据流向为:首先明文数据通过数据总线写入16位入128位出的FIFO缓存;然后由控制模块启动AES加密模块进行一次加密运算;运算完成输出128 bit密文存入128位入16出的FIFO中。解密过程与其相同。

图1 整体内部结构框

2.2 加密模块和解密模块设计

2.2.1 字节替换和逆字节替换的实现

字节替换是AES密码中唯一的非线性变换。它将状态组的每一个字节非线性变换成另一个字节。此模块如果采用 GF(28)模乘求逆运算[4]实现,则逻辑延时较长,速度较慢。为加快速度,采用时延小、基于只读存储器(ROM)查找方式的S盒结构,即把输入的8bit的数据作为地址而相应的输出作为字节替换后的 8bit数据[5]。逆字节替换是字节替换的逆运算,采用逆S盒实现。字节替换的部分代码是:

case (a)

8’h00: o=8’h63;

8’h01: o=8’h7c;

......

8’hff: o=8’h16;

2.2.2 行移位模块与逆行移位模块的实现

把行移位的结果状态矩阵State的第一行不变,其余的三行依次循环左移一个字节、两个字节、三个字节,变换如式(1)所示。逆行移位模块是行移位的逆变换,即各行进行循环右移。

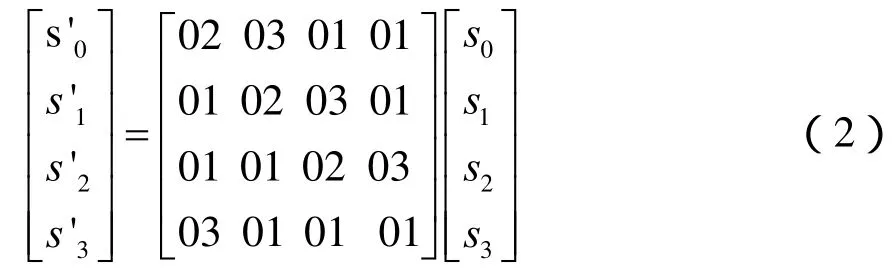

2.2.3 列混合变换与逆列混合变换的实现

列混合变换是利用矩阵乘法做位元变换。列混合变换将行移位的变换结果的状态列看作是有限域上的次数小于 4的多项式 s(x)[6]与多项式进行模x4+1相乘运算。令,用矩阵乘法表示(矩阵元素用十六进制表示)如式(2)所示

function [7:0] mult2;

input [7:0] s;

mult2={s[6],s[5],s[4],s[3]^s[7],s[2]^s[7],s[1],s[0]^s[7],s[7]}

2.2.4 加密与解密密钥扩展模块

密钥扩展作用是负责产生各轮操作所需要的子密钥,它控制着整个算法的效率。因为每一轮变换都要和相应密钥扩展生产的子密钥进行异或运算。加密运算采用的是内部扩展,即加密运算与加密密钥扩展运算是同步的,但是与解密不能同步,因为解密运算使用的初始密钥是加密密钥扩展模块生产的最后一轮子密钥。通过构造不同的加密密钥扩展算法与解密密钥扩展算法,使得采用不同初始密钥实现数据的加密和解密。

AES算法利用外部输入的初始密钥 key(KN 为密钥长度,以字为单位),通过密钥扩展模块得到轮密钥的位数是(分组长度)×(KN+1),即 128×(10+1)=1408位。它涉及到一下二个模块:

1)位置变换模块(rot_word ):把一个4字节的序列in[31:0]变换成{in[23:0],in[31:24]};

2)S盒变换(sub_word):对一个4字节序列进行字节替换。圈常数数组’00’,’00’)是固定的数组,其中 rconst[i]所用可能值是示 ) ’01’,’02’,’04’,’08’,’10’,’20’,’40’,’ 80’,’1b’,’36’,‘6c’(十六进制)。

加密子密钥生成过程:外部输入的密钥作为初始密钥,以后的子密钥就是字 w[i]等于其前一个字w[i-1]与前kN 个字 w[i-kN]进行“异或”,即 []w i=若i是KN 的倍数:w[i]=w[i-加密密钥扩展模块的部分代码是:

rot_word..rw(.i(key_in[31:0]), .out(rot_key));

sub_word sw (.in (rot_key), .out(subrot_key));

xor6_32q(.o(key_out[127:96]),.a({rconst[i],24'b0}),.b(subrot_key),.c(key_in[127:96]),.d(32'b0),.e(32'b0),.f(32'b0));

解密子密钥生成过程是:首先使初始密钥字序列进行异或,然后再进行位置变换、字节替换和异或运算。

解密密钥扩展模块的部分代码是:

assign {a,b,c,d} = key_in;

wire [31:0] w,x,y,z;

assign key_out = {w,x,y,z};

assign z = c ^ d;

assign y = b ^ c;

assign x = a ^ b;

wire [31:0] rot_key;

wire [31:0] subrot_key;

rot_word rw (.in (z), .out(rot_key));

sub_word..sw(.in(rot_key),

.out(subrot_key));

assignw=a ^ subrot_key ^ {rconst,24'b0}

3 AES算法的仿真

用Xilinx ISE Simulator分别对加密模块与解密模块进行功能仿真,加密模块功能仿真结果如图 2所示,其输入明文是dat_in[127:0]=128’h8e09e9d2ba 681af3d6d33313bcdb20d3,密钥是 key[127:0]=128’hfa32bb8cc3c825ad90c45d3ab6980c57,对应的输出密文是 dat_out[127:0]=128’h1468974803d64bcc89bcf 0ad7b28a454。

将加密后的结果进行解密,把加密输出的子密钥作为解密的初始密钥,解密模块功能仿真结果如图 3所示,输入密钥是:inv_key[127:0]=128’h3fdf0ed cabe54f56c60a5337984d34df。解密后的结果:dat_out=128’h8e09e9d2ba681af3d6d33313bcdb20d3,与输入的明文比较结果相同,验证成功。

图2 加密结果信号功能仿真

图3 解密结果信号功能仿真

4 结语

文中加密算法的实现采用赛灵思(Xilinx)公司的Spartan6系列的XC6SLX16芯片作为器件,在ISE 13.1软件平台下对AES算法verilog HDL代码进行编译、综合、仿真。在加密密钥与解密密钥不同,但相关的情况下,经过多次调试仿真后,验证该算法正确性。

[1] 何德彪,胡进,陈建华.基于 FPGA的高速 AES实现[J].华中科技大学学报,2010(02):101-103.

[2] 杨军,张伟平,赵嘎,等.面向 SOPC的 FPGA设计与应用[M].北京:科学出版社,2012:177-188.

[3] 严迎健,任方,付小兵,等.基于 NIOSII的语音加密传输系统设计[J].电子技术应用,2009(09):61-6.

[4] 宋军辉.基于选进加密标准(AES)算法的加密芯片设计[D].南京:南京理工大学,2004.

[5] 黄前山,季晓勇.基于低成本 FPGA的 AES密码算法设计[J].通信技术,2010,43(09):156-158.

[6] 高帅娜.基于 FPGA的数据加密设备的设计[D].大连:大连海事大学,2012.