弹光调制高速大容量存储系统

2013-09-11王耀利王志斌赵冬娥张敏娟黄艳飞

王耀利,王志斌,2,赵冬娥,2,张敏娟,黄艳飞,张 瑞

(1.中北大学 山西省光电信息与仪器工程技术研究中心,山西 太原030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原030051)

0 引 言

近年来,弹光调制傅里叶变换光谱仪 (PEM-FTS)在科研、环境和军事等方面得到了越来越广泛的应用。通常情况下,弹光调制傅里叶变换光谱仪具有高速,高灵敏度等特点,每秒可产生上万张干涉图,要求其采集数据不仅速度快而且数据量大,需要辅以高速大容量的存储器实现数据缓存。目前市场上使用的存储器有很多种,包括FLASH,SRAM,SDRAM以及SD卡,硬盘等等。其中,SRAM速度快,控制简单,适合小容量存储,但当缓存容量较大时,采用SRAM会造成成本高,功耗大,可靠性差的问题[1]。FLASH的存储容量也比较小,很难用到需大容量缓存的场合。与以上两种存储器相比,SDRAM (synchronous dynamic random access memory)传输速度可以达到100M以上,容量也可达到几十兆甚至几百兆,具有传输速率快,容量大等特点[2],可以在多个领域应用。可编程逻辑器件FPGA具有灵活、设计周期短,具有模块化和控制简单等特点,同时也可以满足弹光调制傅里叶变换光谱仪的要求。

本文根据弹光调制傅里叶变换光谱仪需高速大容量存储的要求,为使所研光谱仪速度快、结构紧凑并便于携带,并结合FPGA和SDRAM的特点,设计了一种基于FPGA控制的SDRAM存储方案,使其工作在突发页模式下,实现数据的高速存储管理。用Verilog HDL语言对控制器进行代码开发,在实验室自行设计的基于FPGA的存储控制卡上通过了硬件测试,实现了弹光调制干涉信号数据的海量缓存。

1 弹光调制干涉原理

弹光调制器是一种基于高性能弹光晶体 (如熔融石英、硒化锌等)弹光效应的调制器件,利用压电晶体 (如石英、压电陶瓷)在光学各向同性的物质上加以周期性变化的机械应力,使弹光晶体共振,形成应力驻波,由于弹光效应,弹光晶体出现周期性变化的双折射,因此光通过弹光调制器后其相位被调制[3]。被测光通过弹光调制器后,由探测器探测到的干涉信号并将其转化为电信号,调制后干涉信号为

式中:L——弹光调制后产生的最大光程差,σ——被测光波数,f——调制频率,I(σ)——被测光光谱。对干涉信号傅里叶变换便可获得被测光的光谱

式中:T——调制周期 (T=1/f)。

弹光调制的调制频率f为40~100KHz,光谱范围为454~18180cm-1,光谱分辨率最高为10cm-1,由此可以看出弹光调制器经相位调制后产生的干涉信号调制频率较高,每秒可产生上万张干涉图。根据弹光调制傅里叶变换光谱仪的要求和式 (1)可得干涉信号的频率最高可达100MHz左右,数据量大,这就为后续数据的采集和存储提出了高速大容量的要求。

2 SDRAM工作原理

2.1 SDRAM时序特点

SDRAM时序要求比较严格,只有上电逻辑和模式设置正确才能正常工作。而且在存储的时候必须首先激活相应的存储空间 (BANK),并给出相应的行列地址。同时,每隔一定的时间需进行刷新操作以保证数据不会丢失[4]。

SDRAM工作是以系统时钟CLK上升沿触发的,它包括如下几根信号线:行地址选通RAS、列地址选通CAS、读写使能 WE、时钟信号CKE/CLK、片选信号线CS。SDRAM的工作状态由 WE/RAS/CAS组合在时钟上升沿决定,同时地址线和BANK选择控制线锁定相应的地址[5]。

2.2 SDRAM工作状态分析

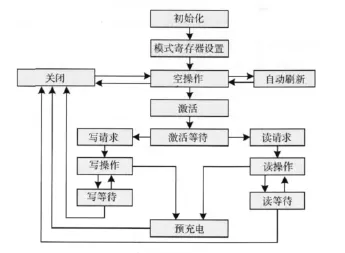

SDRAM正常工作之前,首先要进行初始化,依次为:200us输入稳定期,所有BANK预充电,8个刷新周期和模式寄存器设置 (MRS)[6]。设置完模式寄存器之后就开始进入正常工作状态,首先由写FIFO提供SDRAM写请求,并激活相应的BANK、行、列,数据开始写入SDRAM。与此同时,读FIFO提供SDRAM读请求,亦需激活相应的行、列,数据开始从SDRAM中读出到读FIFO。至此,完成了SDRAM读写操作。需要注意的是,SDRAM每读写完一行,需对其进行预充电操作,关闭当前读写完的一行,开启下一需要读写的一行。不操作时SDRAM处于 W_IDLE(空操作)状态;如果有读请求,写请求或者自刷新请求信号产生,则进入相应的状态,在这些不同的响应状态中需要协调好SDRAM的控制总线、地址总线及数据总线,从而保证稳定可靠地读/写SDRAM的数据。

SDRAM工作以状态机的形式实现。其工作原理[7]如图1所示。

图1 SDRAM工作流程

3 基于FPGA的SDRAM系统设计

3.1 时钟模块

SDRAM时序要求很高,故对时钟的要求也比较高,在通常的SDRAM读写设计实验中一般要用到两个时钟,一个是用于FPGA上的系统时钟,一个是加在SDRAM上的工作时钟。在本实验中,FPGA系统时钟为25MHz,而SDRAM工作时钟达到了100MHz,为了使产生的时钟能够更稳定的工作,实验采用了Xilinx ISE中内嵌的DCM时钟管理模块来实现。

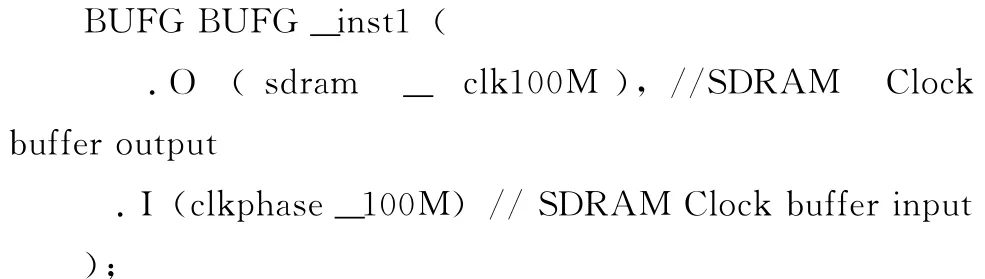

在本实验中,晶振提供的时钟频率为50MHz,要提供FPGA系统时钟的25MHz和SDRAM工作时钟的100 MHz,需要用到时钟分频和倍频,这些在DCM时钟管理模块中都可以实现。而问题的关键在于SDRAM时钟要求在100MHz的基础上相移相应的相位 (具体相移根据实际情况而定,以满足芯片的建立保持时间为准,本实验是有一个+2ns的相移),这就要用到DCM时钟模块的级联[8],即第一级DCM实现零相移的100MHz的时钟,第二级DCM在第一级的基础上实现带相移的100MHz的SDRAM工作时钟。在Xilinx ISE中要实现DCM的级联,需要相关的器件原语调用。BUFG是全局缓冲,它的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。BUFGCE是带有时钟使能端的全局缓冲。在两个DCM例化核之间添加以下原语:

其中CLK_100M_OUT是第一级DCM核中100MHz的时钟的输出,CLK100M为第二级DCM核中要实现带相移的100MHz的SDRAM工作时钟的输入。

为使产生的时钟输出达到无抖动延迟,在DCM的时钟输出之后添加BUFG原语:

其中clkphase_100M是第二级DCM核中带相移的100MHz的时钟的输出,sdram_clk100M为要接入的SDRAM工作时钟的输入。

3.2 FIFO模块

SDRAM存储用到FIFO模块,是因为外部数据与SDRAM控制器接收时的速率不匹配,实验中外部数据与SDRAM控制器接收时的速率不匹配,外部数据产生速率是FPGA系统时钟 (25MHz),而SDRAM数据接收速率为100MHz;同样的,把SDRAM中存储的数据通过串口传输到上位机时,也会有一个速率匹配的问题,所以在SDRAM存储系统设计中用到了FIFO模块,其中有两个FIFO,一个写FIFO,一个读FIFO。

由于以上不同步原因的存在,以及提高访问率,降低功耗[9],在这里用到的是异步FIFO。FIFO模块中有wr_clk和rd_clk,wr_data_count和rd_data_count,其中wr_data_count与wr_clk同步,rd_data_count与rd_clk同步。写FIFO中,数据从外部写入,时钟与外部系统时钟同步,即25M;而数据从FIFO读出写入SDRAM时,又与SDRAM工作时钟同步,即100M。读FIFO正好相反,数据写入读FIFO时钟为100M,数据读出读FIFO为25M。

程序中SDRAM的读写请求与FIFO中的数据量息息相关,根据数据有效程度同步产生SDRAM的读写请求。FIFO中一个写计数器,一个读计数器,经过分析,写FIFO中应该使用读计数器,读FIFO中应该使用写计数器。原因如下。

在写FIFO工作时,数据写入一个的频率是25M,在此时间内,数据可以读出4个。根据assign sdram_wr_req= ((wrf_free>=9'd8)& ~syswr_done);

当写FIFO中数据量大于等于8个的时候就会向SDRAM发出写入的请求,而此时如果用时钟是25M的写计数器时,就会出现一种错误,即当FIFO中的数据读出不到4个时,FIFO中的计数器显示的还是8个,但是其数据量其实已经变成7,6或5个了,本来当FIFO中数据小于8个时,SDRAM写请求就应该取消了,但是这样的话就把SDRAM写请求的时间延长了,造成了SDRAM写入错误。转而言之,如果用时钟频率是100M的读计数器时,就可以避免这个问题产生。读FIFO亦是如此,总而言之,应该用频率比较大的计数器,否则频率小的计数器赶不上数据增减的改变,容易出现错误。

3.3 SDRAM控制器模块

本实验中使用的SDRAM控制器主要有3个模块构成,即状态控制模块,命令生成模块以及数据通路模块[10]。

SDRAM状态控制模块,该模块完成了SDRAM工作前的初始化过程以及模式寄存器的设置,确定了SDRAM工作模式;读写及自刷新操作状态机实现了对SDRAM工作状态的控制。在该状态机中实现了SDRAM各工作状态的转换。突发读写[11]过程是主状态机的重要一环,负责将数据写入和读出SDRAM按照何种方式来进行,本实验采用的是突发全页读写,即激活一次行列地址可以读写256个数据。

SDRAM命令模块,该模块根据状态控制模块两个状态机中不同状态指示译为相应的命令,并结合相应的地址进入命令协调过程,对送入的命令进行仲裁。对命令设定优先级,遵循 “先到先执行原则”,正在执行的命令优先级最高,刷新命令次之,最后是其他命令,以减少访问冲突提高访问效率[12]。

控制信号包括:sdram_cke,sdram_cs_n,sdram_we_n,sdram_ras_n,sdram_cas_n;

地址总线信号:sdram_addr,12位地址线复用[13]。

SDRAM数据读/写模块,该模块根据状态转换模块的要求,通过双向数据线方向控制实现数据线上读写状态的转换,主要是要配合数据总线使wrfifo的读信号与数据总线占用同步,rdfifo的写信号与数据总线占用同步,使得在读写状态下数据以不同方向分别出现在数据总线上,这里需要参考工作状态机work_state_r的转换时序。

3.4 系统延迟

SDRAM在正式工作之前需要一定的时间对自身进行配置,这段时间里数据不允许写入到SDRAM中,如果强制写入会造成数据的丢失,在这段时间需要用到计数器延迟相应的时间等待SDRAM准备完毕。在SDRAM存储的整个工程中大量用到了计数器延迟的功能,准确的实现了SDRAM工作时序的要求。

4 设计仿真与实验

本设计采用的是三星公司12位的K4S641632N-LC60型号容量为64M的SDRAM芯片,以及Xilinx公司Spartan 3E系列的XC3S500E-4PQ208的FPGA芯片。实验用Verilog HDL语言在Xilinx ISE 12.4的开发环境中进行了设计输入和综合仿真。为了验证准确性,用 Modelsim 6.5进行了功能仿真,并用NI-5122采集卡在LABVIEW环境下对单块弹光调制器 (photoelastic modulator,PEM)产生的弹光调制干涉信号进行数据采集,将采到的数据存储到SDRAM中,然后将读出的数据用MATLAB进行数据处理,图形还原。其存储速度达到了100MHz。

4.1 SDRAM 初始化

初始化是一系列命令的集合,首先是发出NOP命令(空操作或命令禁止操作),200us时发出预充电命令,然后发八条刷新命令,最后发出LOAD MODEREGISTER(装载模式寄存器)命令,本实验中工作模式设置的是突发全页读写,突发传输方式为顺序传输,CAS延迟设置为3个时钟周期。如图2所示。

图2 SDRAM上电初始化仿真

4.2 写SDRAM数据导入

写入操作是BURST(突发)方式,BURST长度为一页。全页突发操作模式能够很好地发挥SDRAM高速读写的性能,当SDRAM工作在全页突发模式时,读写操作所访问的地址将在页内循环,直至收到突发停止命令或预充电命令。此设计采用了突发停止命令终止页模式 .在执行写入操作时,需要激活 (active)命令,写 (burst write)命令,地址触发等一系列操作。写命令被触发后,数据便以连续一页即256个数据出现在数据总线上。读完一页之后,通过一个突发停止操作关闭当前行,通过预充电命令(precharge)开启下一需要被写入的行。自动刷新 (autorefresh)命令周期性的刷新SDRAM,保证内部数据不丢失。如图3所示。

图3 SDRAM写操作仿真

4.3 存储前后弹光调制干涉信号对比

原始数据是用NI公司的PXI-5122采集卡对弹光调制干涉信号进行采集,采集的弹光调制干涉信号如图4所示。经过SDRAM写入和读出后,通过RS232串口在上位机上进行显示,然后将得到的数据经MATLAB信号还原,得到的数据中出错率在3%以内,误差范围较小,基本可以实现原始数据复原。结果如图5所示。

图4 NI-5122采集波形

5 结束语

图5 MATLAB还原波形

本文基于Xilinx公司的Spantan-3E系列的FPGA芯片对弹光调制傅里叶变换光谱仪的高速数据存储系统进行了设计和软件验证,进而选用三星公司的K4S641632N型号的SDRAM在硬件上实现了该系统数据的存储,有效的解决了弹光调制傅里叶变换光谱仪高速,数据量大,需要缓存的问题。本实验中SDRAM工作在突发页操作模式下,数据读写速度达到了100MHz,存储速度相较既有的存储器使用上有了较大的提高,发挥了SDRAM存储速度快、容量大的优点,满足了系统的实际要求。同时在系统中采用了模块化的设计思想,适用于图像采集,信号处理等许多方面,提高了系统设计的灵活性、简化了二次开发。为后期采用更高性能的SDRAM数据存储提供了良好的基础;但在调试过程中还存在一定的误差,还需要进一步完善。

[1]LI Jin,JIN Longxu,LI Guoning,et al.Application of SDRAM to the large field of view TDICCD space camera[J].Journal of Electronics &Information Technology,2012,34 (5):1246-1251(in Chinese).[李进,金龙旭,李国宁,等.SDRAM在大视场TDICCD空间相机中的应用 [J].电子与信息学报,2012,34 (5):1246-1251.]

[2]LI Jun.Design of SDRAM controller and signal test[J].J of Wuhan Uni of Sci & Tech (Natural Science Edition),2006,27(3):596-598 (in Chinese).[黎俊.SDRAM 控制器设计及信号测试 [J].武汉科技大学学报 (自然科学版),2006,29(6):596-598.]

[3]JING Ning,WANG Zhibin,ZHANG Jilong,et al.Fast spectrum recovery of nonlinear optical path difference interferogram in photoelastic modulator [J].Laser Technology,2012,36(2):271-274 (in Chinese).[景宁,王志斌,张记龙,等.弹光调制非线性光程差干涉信号的快速反演 [J].激光技术,2012,36 (2):271-274.]

[4]SONG Yiming,XIE Yu,LI Chunmao.Design of SDRAM controller based on FPGA [J].Application Research of Computers,2003,29 (9):10-13 (in Chinese). [宋一鸣,谢煜,李春茂.基于FPGA的SDRAM控制器设计 [J].计算机应用,2003,29(9):10-13.]

[5]LU Genfeng.Embedded multi-cpu hardware design and implementation of video surveillance system [D].Chengdu:Southwest Jiaotong University,2009:1-69 (in Chinese).[陆艮峰.嵌入式多CPU视频监控系统硬件设计与实现 [D].成都:西南交通大学,2009:1-69.]

[6]WANG Qian,DING Tiefu.Realization of SDRAM controller in high-speed image storing system [J].Chinese Journal of Liquid Crystals and Displays,2006,21 (1):48-52 (in Chinese).[王骞,丁铁夫.高速图像存储系统中SDRAM控制器的实现[J].液晶与显示,2006,21 (1):48-52.]

[7]CHEN Yingsen,NING Weiming,ZENG Anjun.Design of SDRAM controller based on FPGA [J].Research on Telecommunication Technology,2008 (1):24-29 (in Chinese).[陈英森,宁韦铭,曾安军.基于FPGA的SDRAM控制器设计[J].电信技术研究,2008 (1):24-29.]

[8]LI Yunzhi,LI Liping,YANG Heng.Application of LVDS difference interface based on FPGA [J].Design and Development of IC,2008,33 (12):1138-1142 (in Chinese). [李云志,李立萍,杨恒.基于FPGA的LVDS高速差分板间接口应用 [J].集成电路设计与开发,2008,33 (12):1138-1142.]

[9]ZHAO Chuanmeng,GAO Yan,ZHANG Rong.A simple design and implementation of SDRAM controller[J].Computer &Digital Engineering,2010,38 (8):197-200 (in Chinese).[赵传猛,高岩,张蓉.一种简单的SDRAM控制器实现 [J].计算机与数字工程,2010,38 (8):197-200.]

[10]HOU Honglu,ZHANG Wenfang.Design scheme of SDRAM controller based on FPGA [J].Ordnance Industry Automation,2012,31 (2):57-61 (in Chinese).[侯宏录,张文芳.基于FPGA的SDRAM控制器设计方案 [J].兵工自动化,2012,31 (2):57-61.]

[11]Hansoo Kim,In Cheol.High-performance and low-power memory-interface architechture for video processing applications[J].IEEE Transaction on Circuits and Systems for Video Technology,2001,11 (11):2011.

[12]Benny Akesson,Kees Goossens,Markus Ringhofer.A predictable SDRAM memory controller [C]//CODES+ISSS.NY,USA:ACM,2007.

[13]K4S641632N-LC60data sheet [M].Samsung.