图像信号并行长线传输的实现

2013-08-13甄国涌李辉景

甄国涌,杜 志,李辉景,郑 佳

(中北大学电子测试技术国家重点实验室,山西 太原 030051)

在某视频图像的采集存储系统中,采编器将接收到的视频数据编帧后送至存储器进行存储,通过测试台将数据读回上位机后还原为图像,从而对试验过程中的状态进行分析。在现场测试时,测试台通过长线与采编器相连,由于测试环境干扰较多,传输线距离较长,使得信号在长线中传输时容易受到影响而导致数据错误,数据还原为图像后就会产生失真,从而无法得到一些重要信息,因此保证信号在长线中的可靠传输尤为重要。本文针对长线传输中的问题,从硬件电路和时序两方面进行设计,实现了图像信号在并行长线中的稳定传输。

1 硬件电路设计

1.1 并行长线传输原理

并行长线将测试台和采编器相连,主要实现上位机命令的发送及存储器数据的回读,其传输原理框图如图1所示。上位机软件发送命令经过USB传输到测试台主控卡,经过测试台主控卡FPGA控制发出后再通过50 m长线传输到采编器主控卡,然后采编器与存储器按照控制逻辑执行命令。当上位机发出读数请求命令后,存储器中数据由采编器控制,经过长线传输到测试台,然后测试台控制其读回上位机。

图1 并行长线传输原理框图

1.2 接口电路设计

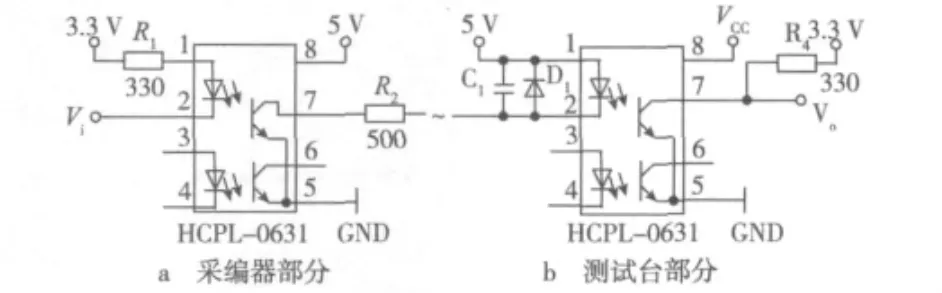

图2所示为并行长线传输的接口电路,对于长线数据Ldata和长线读时钟Lclk,其传输方向由采编器到测试台。

图2 并行长线传输接口电路

由于长线距离较长,因此在发送端和接收端之间存在地电位差,引起地环路电流,从而形成差模干扰。通过采用光电隔离技术[1],将发送端和接收端的电气连接断开,提高了长线传输模块的抗干扰能力。同时,在长线两端均采用光电隔离,使得长线“浮地”[2],减少了因两设备间多点接地而造成的共模干扰。

在接口电路设计中,由于长线分布电容的影响[3],输出端光耦上拉电阻R4的选择成为电路设计的关键。如果选择的上拉电阻阻值不合理,长线分布电容与光耦上拉电阻的充电现象就会使得信号波形在上升沿时发生严重畸变,对于长线读时钟和数据而言,这种畸变会引起较多的误码现象。图3为上拉电阻分别在3.3 kΩ和330 Ω时的时钟和数据波形。图3a是上拉电阻R4为3.3 kΩ时长线读时钟和数据的对应波形图,由于时间常数t=RC,使得电路充电时间过长,从而导致上升过程中爬坡时间太长,很大程度上引起数据误码率的增加。经过调试,上拉电阻为330 Ω时,长线读时钟和数据波形得到很大改善,能够保证数据可靠、正确地传输,其波形图如图3b所示。

图3 不同上拉电阻下的长线读时钟和数据波形图

1.3 传输线的反射干扰

50 m传输线由于穿舱需要被分为A,B,C,D共4段,其中B,C两段传输线长度不能改变,分别为5 m和30 m,A,D的长度在保证总传输线长度不变的情况下可调。4段之间用J14A-26和YF6-57系列接插件进行连接,其连接方式如图4所示。

图4 长线电缆连接示意图

在试验过程中,当A段传输线长度为1 m,D段传输线长度为13.4 m时,按图4连接好长线进行数据传输,在接收端接收到的长线读时钟和数据的波形如图5a所示。从图中可以看出,时钟和数据均发生严重畸变,读回的数据经上位机软件分析后发现严重丢数。而当A段传输线长度为13.4 m,D段传输线长度为1 m时,数据传输正常,其波形如图5b所示。

经过分析发现,当信号在图4长线电缆中进行传输时,由于其传输路径分为4段,而每一段传输线均有相应的瞬态阻抗,当信号传输到两段传输线的接插件连接处时,由于瞬态阻抗发生变化,从而引起信号在阻抗不连续点处的反射。反射的强弱程度可以通过反射系数的大小来表示,将反射系数定义为

图5 长线不同连接方式下的波形

式中:K为反射系数;Z1为输入阻抗;Z2为输出阻抗。当Z1<Z2时,称其为欠阻尼状态,而当Z1>Z2时,称其为过阻尼状态[4]。在工程设计中,由于传输线瞬态阻抗影响,完全使Z1=Z2,即临界阻尼状态很难满足,因此最常用的方式是设计为轻微的过阻尼状态。对图4的连接方式进行反射建模分析,其反射模型如图6所示。

图6 传输线反射模型

当按照A=1 m,B=5 m,C=30 m,D=13.4 m 进行连接时,各段传输线的瞬态阻抗关系为Za<Zb<Zd<Zc。根据式(1),AB反射面和BC反射面的反射系数较大且为正,而CD反射面的反射系数较小且为负。此时,AB和BC反射面均为欠阻尼状态,1 m传输线和13.4 m传输线使得反射面的反射增强,对信号传输影响较大,因此造成图5a的波形畸变。将1 m传输线和13.4 m传输线对换连接后,传输线阻抗匹配使得反射减弱。

2 长线传输时序的抗干扰设计

2.1 长线传输时序设计

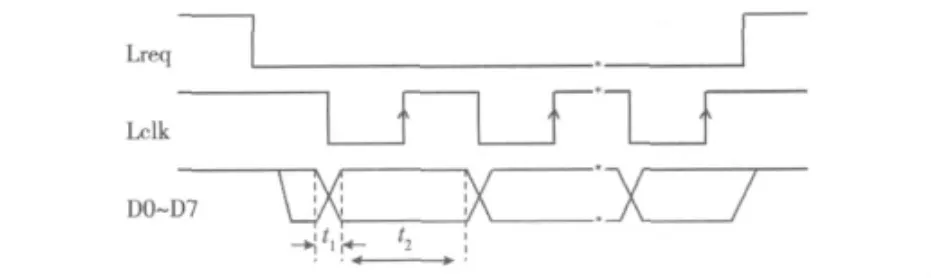

图7为长线传输时序示意图,图中Lreq为长线读数请求,Lclk为长线读时钟,D0~D7为8位并行数据,在数据位中,数据在t1时间段进行转换,在t2时间达到稳定。

图7 长线传输时序

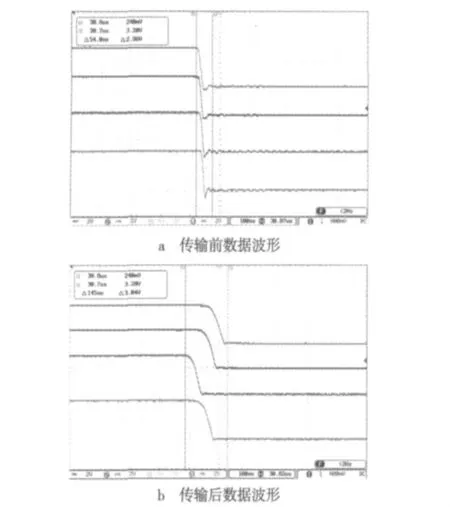

在实际传输过程中,8位数据经长线传输后,使得数据不稳定时间增加,对应图7中t1时间段变长,t2时间段变短。图8为对长线传输前后的4位数据D0~D4进行测量的波形,图8a为传输前的4位数据波形,从图中能够看出,4位数据几乎同步变换,其不稳定时间长度为54 ns。而从图8b中经长线传输后的数据波形能够看出,数据位变换不同步,使得数据不稳定时间长度增加到145 ns。本设计的系统时钟由40 MHz晶振提供,其周期T=1/(40 MHz)=25 ns,图8b数据不稳定,周期个数为145/25≈6个,而读数是在长线读时钟的上升沿进行的,为了保证数据传输的正确,只有增加长线读时钟周期,使得数据稳定时间增长,才能保证数据的正确。因此,长线传输时序的设计关键是对长线读时钟进行调试,达到传输速度和传输距离的最大匹配。

图8 长线传输前后的数据不稳定时间(截图)

2.2 读时钟消抖

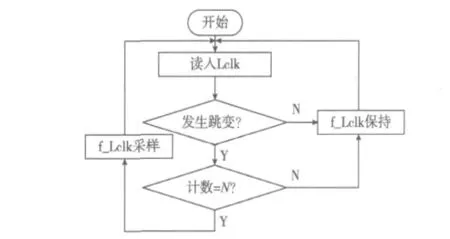

为了提高读时钟的抗干扰能力,长线读时钟的消抖是必须的。本文采用延时比较法进行消抖,其基本原理为:在数字信号产生由1到0或者由0到1的跳变时,只有在其跳变电平保持连续的N个系统时钟时才对其进行采样,否则将该跳变作为抖动消除,保持原来电平不变。长线读时钟消抖流程如图9所示。

图9 长线读时钟消抖流程

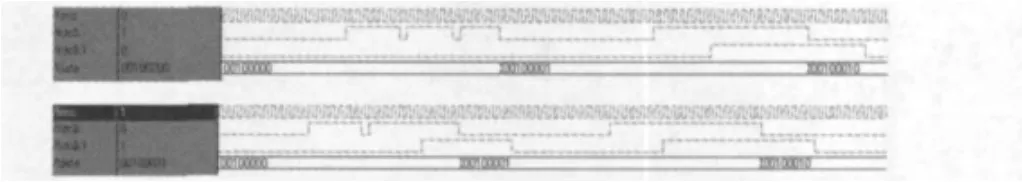

消抖使得波形产生延时,延时时间由为N个系统时钟,消抖计数N的值是影响消抖成败的关键,图10给出了消抖失败引起的两种数据错误的仿真时序。图中fosc为系统时钟,Lrdclk为消抖前的长线读时钟,Lrdclk为消抖后的长线读时钟,Ldata为长线数据。对于图10中上方仿真图,Lrdclk的高电平部分被两个抖动分为3部分,当最长的高电平持续时间低于消抖计数时间时,有效电平被作为抖动消除,消抖后时钟缺少一个上升沿,从而引起数据的丢失。对于图10所示仿真图,Lrdclk的高电平部分被抖动分为两部分,当两部分中较小的一部分的持续时间低于消抖计数时间时,该部分被作为抖动消除,抖动的上升沿被延时到数据的不稳定时间区域,在该区域取数就会产生数据的误码。因此,消抖计数个数必须调试后确定,在本设计中,N的值为6时达到消抖效果。

图10 消抖失败引起的两种数据错误(截图)

3 实验验证

并行长线传输技术接口电路简单、工作稳定,能够满足测试距离和测试速度的要求。本文介绍的并行长线传输速度快,抗干扰能力强,在电磁设备较多的试验环境中,成功保证了4 Gbyte图像数据在1 Mbit/s的传输速度下稳定传输。长线读时钟与系统时钟的波形如图11所示。图11中,在40 MHz晶振提供的系统时钟周期下,每40个系统时钟周期产生1个长线读时钟,因此长线读时钟的频率为1 MHz,而图像数据的读取是在每个长线读时钟的上升沿进行的,因此图像数据的传输速度为1 Mbit/s。

图11 40 MHz系统时钟与长线读时钟对应波形图(截图)

[1]宋晓明,陈方斌,刘鑫.光电耦合器在并口长线传输中的应用[J].电子设计工程,2009,17(5):124-126.

[2]徐瑛,叶璐.实现数据长线传输的方法[J].煤矿自动化,2000(1):13-14.

[3]李永敏,罗麟经,林燕珊.提高长线传输数字波形质量的技术措施[J]. 南京航空航天大学学报,1998,30(1):106-109.

[4]彭元杰,何怡刚等.传输线中信号反射的研究[J].现代电子技术,2007(21):179-184.