基于FPGA的MIMU信号处理技术研究

2013-08-10高挺挺王明明

高挺挺,王明明,潘 辉

(中国空空导弹研究院 河南 洛阳 471009)

由微加速度计和微陀螺仪构成的微型惯性测量组合MIMU(micro inertial measurement unit)是微机电系统的一个重要分支,是国际上近年来发展起来的新技术,是一种依靠自身设备的自主式惯性测量组合,它具有数据更新率高、短期精度和稳定性好等特点,加之其具有体积小、重量轻等优点,在姿态测控、武器制导和其他军事及民用领域具有广阔的应用前景[1-3]。由于MIMU惯性器件具有传统惯性器件不具备的优点,极有可能成为未来航空航天系统的主要惯导器件,美国、日本和俄罗斯等国均已在这方面开展器件和应用研究,国内清华大学和北京大学较早开展MIMU的研究,“十一五”期间已研制出高精度MIMU样件。

MIMU具有其他器件不可比拟的优越性但是现有MIMU的接口形式和数据传输协议与目前激光陀螺和光纤陀螺不一致,无法直接应用系统中去,MIMU在使用和测试上存在一定困难。本文的目的是通过MIMU信号处理电路,使MIMU的信号输出格式与目前应用系统和地面测试系统相兼容,为MIMU的应用验证研究提供条件,为高精度微型惯性测量组合的应用提供技术支持。

1 设计要求

1.1 MIMU接口形式

拟使用的MIMU采用标准RS422接口,波特率为230.4 kbps,通讯格式为:1个起始位,8个数据位,1个停止位,无奇偶校验位。产品正常工作时,一帧数据有31个字节,包含有帧头、数据长度、帧ID、加速度计数据、陀螺数据、帧计数、校验和等内容。MIMU的数据格式如表1所示。

表1 MIMU帧数据格式Tab.1 Format of MIMU data in one frame

1.2 激光或光纤陀螺

目前IMU通常采用激光或光纤陀螺,其输出为脉冲频率调制方式,通过专用接口组件送到应用系统进行处理或送到性能测试系统进行测试。

因此,MIMU不能直接应用到目前的系统上进行试用和验证,要先进行匹配性设计,设计信号处理电路,其功能是:对MIMU信号进行转换,将标准RS422输出转化为目前IMU频率调制的TTL脉冲输出形式,使MIMU的接口与应用系统和测试系统的接口相匹配,从而实现MIMU的应用验证研究。

1.3 技术要求

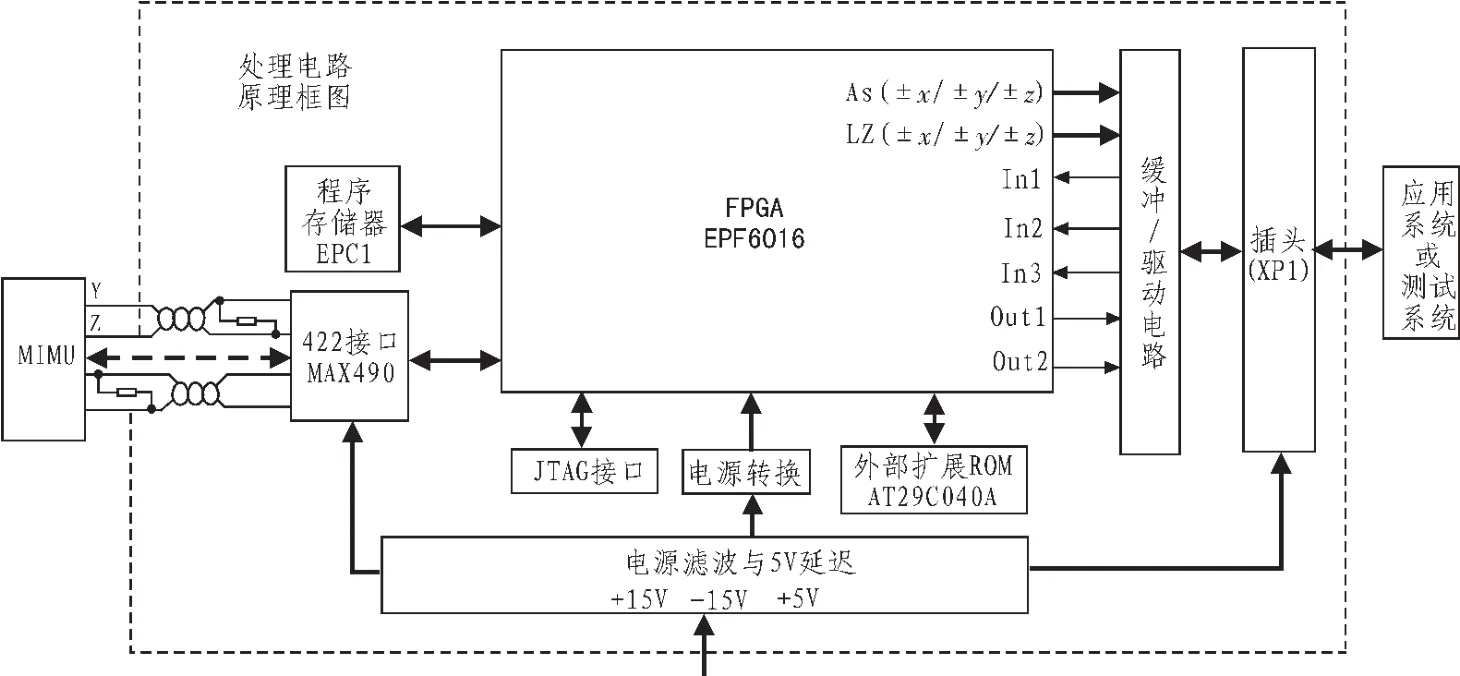

基于FPGA的MIMU信号处理电路的系统框图如图1所示。

从上图中可以看出,信号处理电路要同时满足MIMU和激光或光纤陀螺的接口指标要求,不间断的接收MIMU发送的陀螺和加速度计信息,在硬件平台的基础上完成MIMU数据接收、处理和发送,然后提供足够精度的惯性测量数据。

信号处理电路的主要技术指标有:

图1 系统总体结构图Fig.1 System architecture overview

1)实时接收MIMU发送的RS422格式数据,可识别帧类型,并进行校验。

2)从信号线上分别输出相应的计数脉冲信号,脉冲个数按照当前的有效MIMU数据计算得出。

2 硬件设计方案

2.1 主处理器的选择

根据信号处理电路的技术要求,处理电路完成信号处理与转换功能没有复杂的数学运算,本设计中FPGA选用Altera公司的EPF6016芯片作为主处理器。该芯片具有丰富的硬件资源,能够真正实现多模块并行工作,具有低成本、低功耗、小体积等突出优点[4],在5 V供电电压下,该芯片能够提供大于100 mA的I/O驱动能力,能够高速、准确地完成MIMU输出信号的接收、处理以及飞控舱信号的输出和驱动。

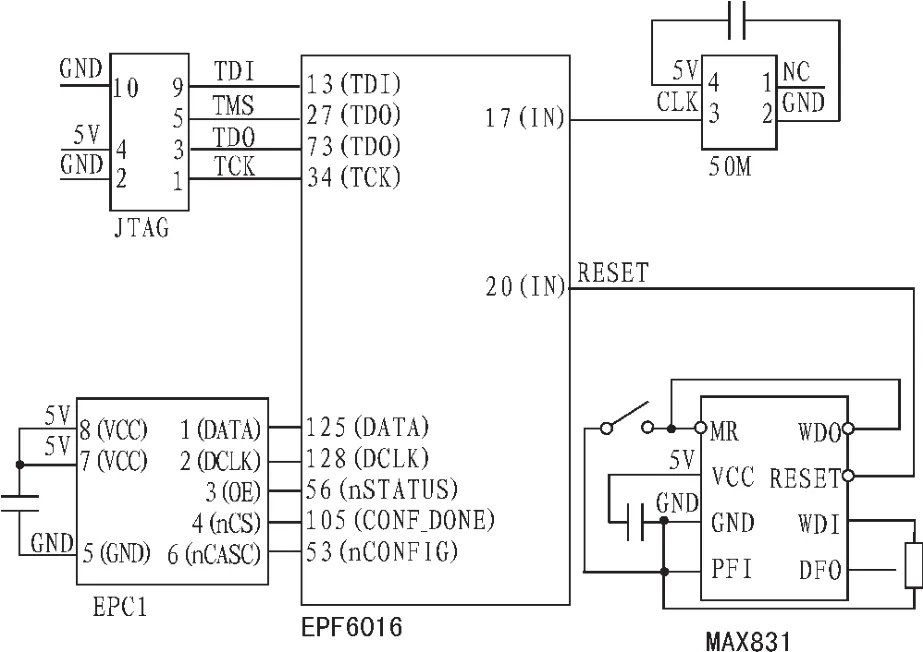

2.2 FPGA最小系统

FPGA最小系统是FPGA系统工作所需的基本电路,主要包括电源电路、时钟电路、复位电路、JTAG电路以及配置芯片电路等。FPGA最小系统电路图如图2所示。

EPF6016采用被动串行(PS)配置方式。MSEL1、MSEL0是EPF6016选择配置方式的引脚,外围电路中均接地,选择PS 方式[5]。

配置芯片是一种能产生配置时序的ROM,分为一次编程型和可擦除型两种[6]。本设计采用Altera公司的EPC1系列配置芯片,在程序最终测试成功后,写入该芯片中。FPGA在上电后,会自动从配置芯片中读出配置数据,存入SRAM中。

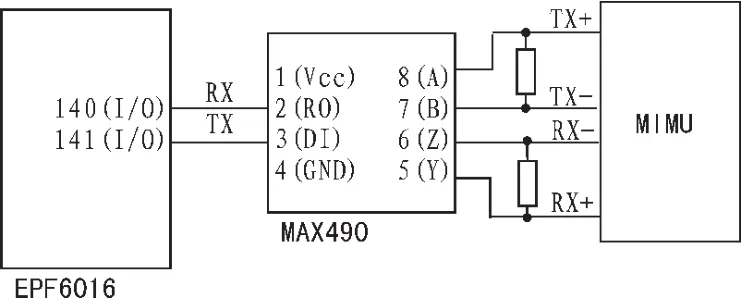

2.3 MIMU接口电路

MIMU接口电路主要包括供电电路部分和数据通信电路部分,采用31针的微矩形航空接头。MIMU所需的供电电压为±15 V和5 V,由外部电源提供供电。MIMU的数据通信接口采用标准的RS422异步串行口,波特率为230 400 bps,接口电路如图3所示,主要是在MIMU接口与FPGA主处理器之间通过1个RS422收发器,将差分信号转化为TTL电平信号。本设计中采用MAX490芯片进行差分信号转换,可实现全双工数据通信,快捷方便。

图2 FPGA最小系统电路图Fig.2 The minimal circuit of FPGA

图3 MIMU通信接口电路图Fig.3 The interface between MIMU and FPGA

2.4 信号输出电路

信号输出电路主要是提供足够的驱动能力,输出应用系统或测试系统所需的惯性单元接口信号。由于FPGA芯片EPF6016的I/O管脚能够提高不小于100 mA的驱动能力,本设计直接用FPGA芯片的I/O管脚进行驱动,不再考虑增加驱动能力。

3 软件设计方案

根据系统功能需求,软件实现分成3部分:第一部分实现对MIMU发送RS422数据的接收与实时处理;第二部分实现向应用系统或测试系统实时发送带有加速度角速度信息的脉冲数据;第三部分实现系统功能自检。

信号处理电路软件是用Verilog HDL语言编写的FPGA程序,主要包括顶层模块、时钟模块、UART发收机模块、数据接收和转换模块以及信号输出模块等5个模块,其原理框图如图4所示。

图4 FPGA内部逻辑图Fig.4 FPGA logic diagram

3.1 顶层及时钟模块

顶层模块主要功能是确定FPGA的输入输出,实现输入输出管脚以及内部各个模块彼此之间的连接和信号、数据的传输。

时钟模块主要是为信号输出模块提供500 ns基础时钟、角速度信号输出所需的同步信号Out1以及加速度信号输出所需的计时信号。其中500 ns时钟是对50 MHz系统时钟进行分频获得,Out1信号则是以外部输入的信号In1为基准,而计时信号则是对外部输入的信号In3计数产生的,以500 ns时钟为例,流程图如图5所示。

图5 时钟模块流程图Fig.5 Flow chart of the clock module

3.2 UART收发机模块

UART收发机模块的功能是实现对标准的异步串行数据读取,主要包括起始位检测、同步时钟产生、波特率计数以及数据读取等4个部分。

根据异步串行数据的标准,在空闲状态下,数据线上为高电平,当有数据来临时,首先会把数据线拉低,这一位即是起始位。起始位检测即是根据这一特性,在空闲状态下检测数据线的下降沿,并把标志寄存器置1,在其它状态下则把标志寄存器置0。

波特率计数是在50 MHz系统时钟的基础上分频,循环计数,产生所需的波特率。与时钟模块中计数不同的是,它只在起始位标志为1时或者数据状态不为IDLE时才循环计数,其它状态下计数寄存器都为0,不进行计数。同步时钟则是在计数寄存器中的数值为分频因数1/2的这一时钟周期内为高电平,其余都为低电平。

数据读取部分采用状态机的模式编写,包括了idle、shift、stop 3个状态,这3个状态的操作都是在rxdclk为1的条件下执行。当处于idle状态下,程序对接收完毕标志datardy以及移位寄存器q进行清零,同时对数据线rxd电平进行判断,如果是低电平,则进入shift状态,否则还停留在idle状态。shift状态中,数据位数计数器bit_cont每次加1,移位寄存器右移一位,并把数据线上当前的一位数据放置于移位寄存器的最高位。当bit_cont等于7时,跳出shift状态,进入stop状态。stop状态中,检测的停止位时,把移位寄存器q中数据赋予输出寄存器data,并置接收完毕标志datardy为1。数据读取部分的流程图如图6所示。

图6 UART模块流程图Fig.6 Flow chart of the UART module

3.3 数据接收及转换模块

数据接收及转换模块包括两个部分:一是对MIMU发出的31字节数据进行接收、校验等;二是将MIMU的角速度、加速度数据转换成相应的脉冲数。

数据接收部分则根据MIMU的通信协议,首先对数据帧头进行检测,当前两个字节数据是帧头数据时,则进行下面的操作,不是帧头数据时则放弃该数据,重新检测数据帧头。检测到数据帧头后,则对接下来的28个字节数据进行接收、存储,以及计算它们的累加和。然后接收最后一个字节数据,并与前面28字节数据的累加和比较,相等则把标志寄存器置为1,表明该帧数据接收完毕,不相等则说明这一帧数据中出现有误码,须舍去该帧数据。

数据转换部分则是对上面接收的加速度、角速度值按前面介绍的增量当量和刷新时间转换成各个通道的脉冲数。在这里考虑到角速度和加速度的量程以及精度等因数,把MIMU输出的每个通道数据的高八位以及低十二位舍去,取其中十二位作为有效数据计算。首先,提取最高位数值,作为符号标志。当符号标志为1时,表明该数值为负数,取原数据的反码作为其数值的绝对值;当符号标志为0时,表明该数值为正数,原数据即为其数值的绝对值。然后分别计算角速度和加速度的输出脉冲数,并赋值予输出接口,其中对于角速度脉冲数,当符号标志为1时,计算出的脉冲数赋予负通道,正通道赋值0;当符号标志为0时,计算出的脉冲数则赋予正通道,负通道赋值0。

3.4 信号输出模块

信号输出模块包括角速度信号输出和加速度信号输出两个部分。

角速度通道输出的脉冲为负脉冲,以固定频率输出脉冲,直到所需脉冲个数输出完毕为止。另外,在Out1信号为高电平时,输出正通道,在Out1信号为低电平时,输出负通道。

加速度通道输出的脉冲为正脉冲,在计时信号开始后,以固定频率输出脉冲,即检测到一个In3信号,输出一个脉冲,直至所需脉冲个数输出完毕为止。加速度通道符号标志为1时,负通道输出脉冲,正通道输出低电平;符号标志为0时,正通道输出脉冲,负通道输出低电平。

4 结 论

本文所设计的信号处理电路充分考虑了MIMU所使用的RS422协议及帧格式要求,针对现有应用系统或测试系统所使用的特殊数据传输格式进行设计,实现了RS422数据信息向脉冲调制频率信号的转变。

通过对MIMU信号协议转换技术的研究,实现了多标准协议相互转换,通过MIMU信号协议转换电路,可使MIMU的信号输出格式与激光或光纤陀螺电气属性兼容进行相互转换;设计了详细的系统自检功能,可在系统调试中迅速并准确定位故障位置,减少系统调试时间与工作量,缩短了系统研制进程;在MIMU信号处理平台的设计过程中采取增加系统冗余度的设计方法,由于MIMU的信号刷新速率低,可在保证系统功能的前提下调高系统的可靠性。

MIMU信号协议处理技术研究的成功开展,可不需对现有系统进行任何修改,直接应用国内最先进的MIMU,为未来小型化、智能化的迫切需求,为开展精确制导武器专用MEMS器件设计、制造、封装、测试等基础工艺研究以及基于MEMS器件的新型机载制导武器系统应用基础研究提供技术基础。

[1]马芮,孔星炜.MIMU在机载制导武器中的应用[J].飞航导弹,2008(6):45-50.MA Rui,KONG Xing-wen.The use of MIMU in airborne guided weapons[J].Winged Missiles Journal,2008(6):45-50.

[2]富立,时光煜.基于FPGA的组合导航系统专用接口板设计[J].中国惯性技术学报,2008,16(3):330-333.FU Li,SHI Guang-yu.Design of special interface board of integrated navigation system based on FPGA[J].Journal of Chinese Inertial Technology,2008,16(3):330-333.

[3]马云峰.基于MIMU/GPS的组合导航计算机设计[J].计算机测量与控制,2009,17(3):549-551.MA Yun-feng.Design of MIMU/GPS Navigation Computer[J].Computer Measurement&Comtrol,2009,17(3):549-551.

[4]肖敏.PWM控制的FPGA实现[J].绵阳师范学院学报,2009,28(5):35-38.XIAO Min.FPGA implementation of the PWM control[J].Journal of Mianyang Normal University,2009,28(5):35-38.

[5]杨扬,叶芃,李力,等.基于FPGA的UART设计与实现[J].电子测量技术,2011,34(7):80-82.YANG Yang,YE Peng,LI Li,et al. Design and implementation of UART based on FPGA[J].Electronic MeasurementTechnology,2011,34(7):80-82.

[6]陈兴文,刘燕.基于FPGA实现步进电机脉冲信号控制器设计[J].机械设计与制造,2006(2):86-87.CHEN Xing-wen,LIU Yan.The design of impulse signal controller in stepper motor based on FPGA[J].Machinery Design&Manufacture,2006(2):86-87.