一种多类型传统接口的IP化方案*

2013-08-10胡赞军

胡赞军

(中国船舶重工集团公司第七二二研究所 武汉 430205)

1 引言

在传统通信领域,各设备采用的接口种类、形式多样,存在接口标准不统一、对接过程繁琐、操作维护不方便等问题,IP接口因带宽高、兼容性好、接口简洁等优点已成为业务接口发展的趋势。而因改造投资成本、技术实现难度等方面的客观原因,一些设备暂时只能通过其它专用设备实现接口IP化的改造。目前此类IP化的专用设备存在接口类型单一、接口数量偏少的问题。因各传统业务带宽基本上小于8M,将多个接口业务并入一个IP接口(100M)成为一种可能,本方案便是基于此思路实现的。方案集成了RS232/422/485、V.35、A 口、K 口、E1等多种类型的业务接口,将各接口统一转化为n×64Kbps同步串行接口(简称同步串口,下同),然后由FPGA实现16路同步串口至1路MII接口的转换。与此类方案采用传统的E1电路仿真、反向复用等方式不同,本方案支持的业务颗粒度更小(16K~8M),具有一定的创新性。同时方案实现简洁、紧凑,可在高度为1U的标准机架安装环境下提供较多的业务接口,采用模块化设计后,业务槽位可实现兼容互换,能根据应用需求,灵活配置接口模块,提供最多16个传统非IP业务接口的接入。

2 方案实现

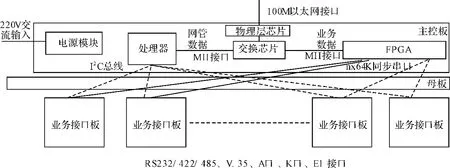

方案实现框图如图1,对外提供220V交流输入、100M以太网、传统业务三种接口。从功能角度而言,方案可分为主控板、业务接口板、母板三大部分。

图1 系统实现框图

主控板由电源、处理器、交换芯片、物理层芯片、FPGA等模块组成,完成集中供电、网管代理、软件配置、二层交换、以太网物理层处理、同步串口数据IP封装及解封装等功能。系统采用集中供电方式,电源模块将外部输入交流220V转换为3.3V、5V电压,提供给主控板、业务接口板各级模块使用。处理器完成网管代理的功能,对FPGA等模块进行配置及状态监测。同时基于实现成本、接口信号数量的考虑,由主控板处理器通过I2C总线完成对接口板的管理,主控板采用专用芯片实现并行访问接口转多个I2C接口(主模式)的功能,接口板采用FPGA/EPLD逻辑芯片实现I2C接口(从模式)的功能[1]。交换芯片完成以太网二层交换功能,实现业务数据和网管数据的融合与分离。

业务接口板完成 RS232/422/485、V.35、E1、A 口、K口等传统非IP接口与同步串口的转换。

母板实现主控板与业务接口板之间的各类信号的连接。

母板位于最底部,主控板、接口板分别安装于母板上,两者处于同一平面,各印制板均采用2.0mm设计。接口板中的A、K接口还需安装对应的接口转换扣板(正面高7mm、板厚2.0mm、背面高8.2mm)。整套板件可安装于1U高度的结构空间内,此种分层设计架构,在确保系统可靠性的同时,有效地利用了空间,可提供更多的业务接口。

本方案的网络管理功能基于Web Sever方式实现,处理器内部的以太网模块对应唯一、特定的IP地址(默认设置为192.168.2.1)。网管计算机通过外部交换网络、主控板100M业务与网管共享端口实现与主控板处理器的信息交互,而主控板处理器通过I2C接口与接口板各模块进行联络。在网管计算机中打开IE浏览器,输入网管IP地址即可进入管理、配置界面。

传统业务接口的IP化处理是本方案的关键点,下文将着重对此进行描述。

2.1 传统业务接口与同步串口的转换

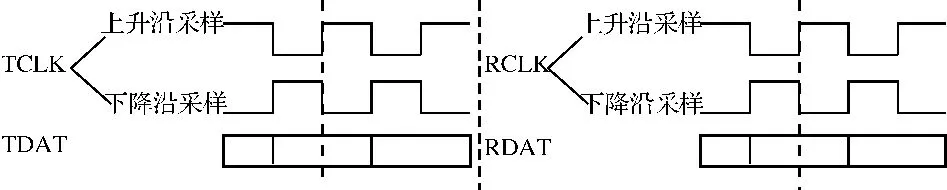

同步串口由发时钟TCLK、发数据TDAT、收时钟RCLK、收数据RDAT双向四种信号组成,如图2,TCLK、RCLK时钟占空比为50%,频率均为n×64KHz,时钟采样沿可通过软件配置。

图2 同步串口时序

各传统业务接口与同步串口的转换实现如下:

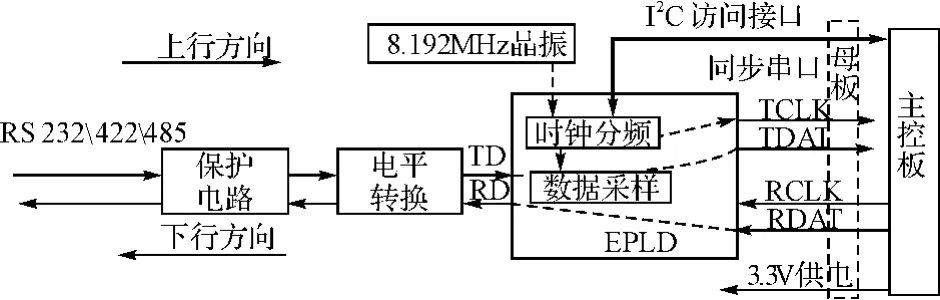

1)异步数据接口

异步数据接口为RS232\422\485电平接口。如图3所示,异步数据经过过流及过压保护电路、串口电平与LVTTL转换、EPLD后实现到同步串口的转换。EPLD处理时,上行方向将本地8.192MHz时钟进行分频(分频参数由主控板通过I2C接口进行设置),分频后的时钟输出至TCLK时钟,同时对异步数据接口输入的数据TD进行采样,并输出至TDAT;下行方向RDAT数据直接输出至异步数据接口的RD。

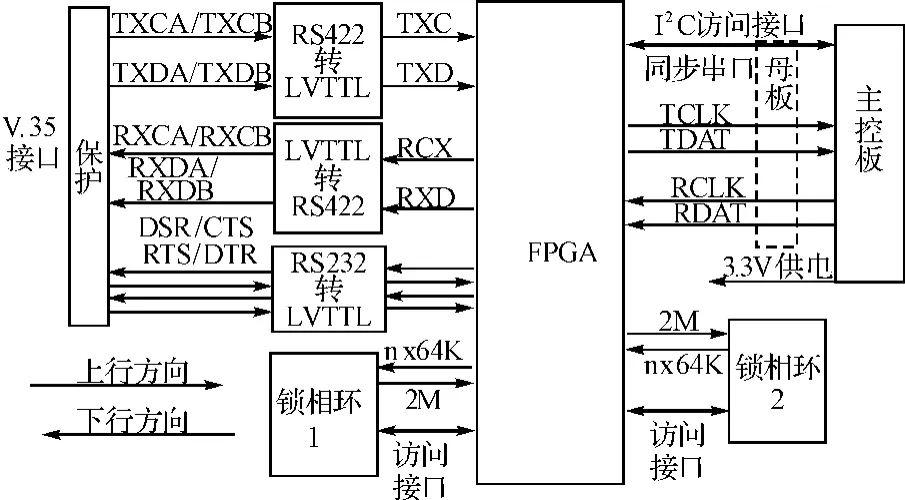

2)V.35接口

图3 异步数据接口转换实现原理图

如图4所示,V.35接口为同步接口,时钟TXDA/B、RXDA/B及数据信号 TXCA/B、RXCA/B为 RS422电平,流控制信号CTS/DSR/RTS/DTR为 RS232电平[2]速率为64Kbps整数倍、且不大于1920Kbps(方案限制)。V.35接口数据经过过流及过压保护电路、接口电平与LVTTL转换、FPGA数据缓存、成帧与解帧后实现与同步串口的转换。FPGA处理时,上行方向TXC通过锁相环1(倍频参数由主控板通过I2C接口进行设置)倍频产生TCLK(频率固定为2.048MHz),TCLK、TXC时钟分别作为逻辑内双口RAM的读和写时钟,数据信号进入RAM缓存后,与经过TCLK采样的流控信号合并成带同步字节的2.048Mbps PCM串行码流,其中时隙0为同步字0x55,时隙1比特0~4为CTS信号、比特5~8为DSR信号,时隙2~31为数据;下行方向RCLK(主控板提供、频率固定为2.048MHz)通过锁相环2(分频参数由主控板通过I2C接口进行设置)分频产生RXC,RCLK、RXC时钟分别作为逻辑内双口RAM的写和读时钟,根据同步字节(每隔125μs、连续三次收到0x55,确定一帧的起始位置)对2.048Mbps PCM串行码流进行解帧,从对应时隙分离出数据和流控信号(根据CTS信号产生RTS信号、DSR信号产生DTR信号)。

图4 V.35接口转换实现原理图

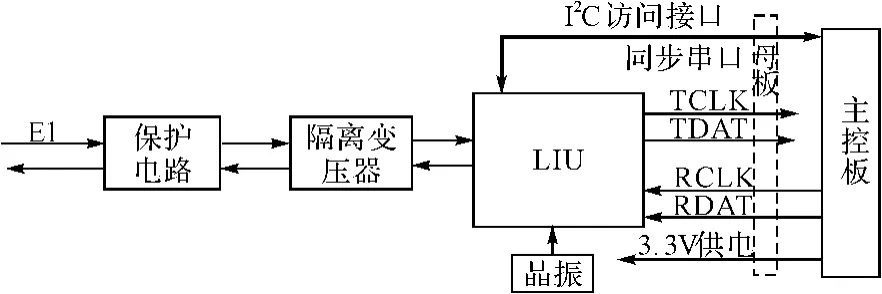

3)E1接口

E1接口为含双向差分数据线的时分复用接口,速率为2.048Mbps,支持75Ω与120Ω两种阻抗。如图5所示,E1数据经过过流及过压保护电路、隔离变压器、LIU后实现到同步串口的转换。隔离变压器用于隔离接口、滤除干扰、改善信号传输质量。LIU需外接2.048MHz晶振,完成HDB3码编解码、信号去抖、时钟恢复等功能,提供NRZ接口可与同步串口(n=32)直接对接[3]主控板通过I2C接口完成对LIU的配置。

4)A接口、K接口

A接口为包含双向差分时钟、数据信号的同步接口,K接口为收发合并的两线接口。两种接口由成熟专用模块实现与同步串口的转换,实现过程较简单,本文不再赘述。

图5 E1接口转换实现原理图

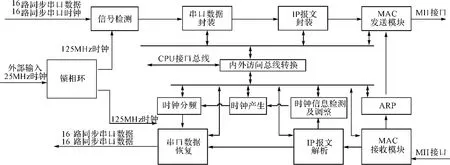

2.2 同步串口与MII接口的转换

同步串口数据在主控板的FPGA内实现IP封装及解封装,FPGA可完成16路速率可配置的同步串口与1路100M速率MII接口的转换。MII接口是IEEE-802.3定义的以太网行业标准,它包含收发方向的4位数据线、时钟、控制等一共16根信号线。

FPGA选用XILINX公司SPARTEN6系列的XC6SLX45-3FGG484I芯片。该型芯片采用45nm工艺、高性能1.2V内核电压、兼容3.3V~1.2VI/O标准和协议、集成数据最高速率达800Mb/s的DDR3等存储控制器模块,芯片资源丰富含43661个逻辑单元、6822个Slice、54576个触发器、401Kb分布式RAM、最大2088Kb Block RAM模块、最大296个I/O管脚,可满足本设计的要求[4]。

逻辑设计实现框图如图6所示。

图6 逻辑实现框图

外部输入的高精度25MHz时钟经过锁相环后产生125MHz时钟用于信号检测、串口数据封装及解封装、IP报文封装及解封装等处理。16路同步串口时钟、数据进入信号检测模块,125MHz时钟检测同步串口时钟沿的变化,无该时钟时产生信号丢失告警。串口数据封装时,由分别对应同步串口的16个子模块根据处理器配置的串口速率和报文封装长度完成串口数据封装,并向IP报文封装模块发起发送请求。每个子模块检测输入的串口时钟沿 ,用配置的时钟沿(上沿或下沿)将串口数据锁存,同时对时钟沿计数,计数包括三个部分,分别为位计数器(0~7)、字节计数器(0~封包长度)、封包计数器(0~3)。位计数器在每个时钟沿加1,字节计数器在位计数器为7时加1,封包计数器在字节计数器计满配置的包长时加1。这三个计数器作为写地址将串口数据写进数据存储RAM,每个通道最多存储四个数据包。与此同时每完成一个数据包的存储时,就向报文发送请求FIFO中压入该通道对应的相应信息(时间戳,存储页面等),FIFO非空时就向IP报文封装模块发起发送请求。

IP报文封装采用IPV4版本协议进行同步串口数据的封装,将数据填入用户使用的静荷区(为了减少封装时延,净荷长度限制在22比特~512比特之间),将32位的同步时间戳信息填入IP头中。分时仲裁前一级16个串口通道的发送请求,一旦仲裁接受某通道的请求,则进入状态机,待该通道全部完成,才能开始新一次的仲裁。在连续两个报文封装之间为确保封装正确,需设置一定的时间间隔。完成IP封装的报文存储到RAM中,同时将相应报文信息压入FIFO中,FIFO的非空指示作为请求信号向MAC发送模块发起发送报文请求。

MAC发送模块响应前一级模块的发送请求,完成ARP发送请求、MAC报文的封装及数据发送。该模块同样通过状态机来实现各个IP包的数据发送。

MAC接收、IP报文解析、串口数据恢复是上述过程的逆过程,本文不再赘述。

ARP模块需要完成ARP请求报文的产生和ARP应答报文识别、根据ARP请求报文中的目的IP或ARP应答报文的源IP查找本地通道号并更新ARP地址表。

时钟信息检测及调整主要实现两大功能;一是对收到的MAC接收模块送来的时间戳信息进行滤波,去除网络抖动对时戳的影响,根据滤波后的时戳拟合远端的串口时钟曲线。二是定时比较远端的串口时钟曲线和本地串口发送时钟曲线的差异,用差异结果控制本地的串口时钟分频电路,以达到本地时钟曲线和远端时钟曲线一致的目的。

时钟产生模块依照时钟调整信息完成8.192MHz时钟的恢复产生。最终由时钟分频模块依照各通道串口速率配置完成已恢复的8.192MHz时钟到相应速率的分频。

上述处理过程中的RAM实现对数据的缓存。缓存容量的大小需适中,偏小容易造成误码、丢包,偏大则将引入过大时延,一些对适时性要求较高的业务将受到严重影响。本方案将传统业务接口统一转换为同步串口,在根据业务实际情况通过网管平台设定n值后,逻辑设计根据该值自动默认设定适当大小的缓存容量,同时也可提供配置接口由人工调整该缓存容量,以达到时延与误码指标的平衡。

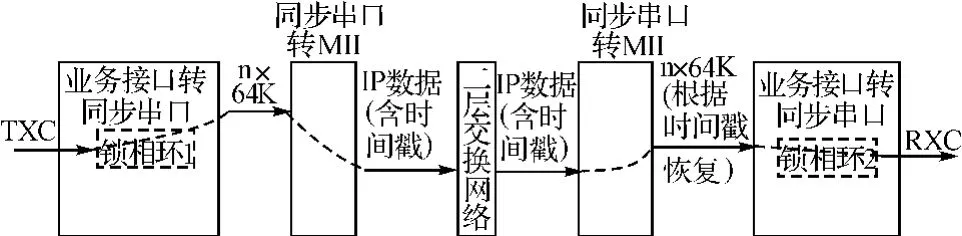

3 业务透传实现流程

各传统业务接口实现IP化后可通过二层交换网络实现各业务的透明传输,该流程的实现包含两层含义,即数据本身的点对点传输及业务接口时钟的同步。

数据透传实现如图7所示,每个同步串口转 MII模块对应唯一的MAC地址,每个业务接口对应单独的IP地址(IP地址即为端口标识,不能与处理器对应的网络管理IP重复)。先由网管计算机配置好每个业务接口的IP地址(源IP地址)、目的IP地址,当两个接口之间需通信时,源端口侧的同步串口转MII模块先在本地ARP地址表中查询有无目的IP地址与MAC地址的对应关系,若无,则需通过发送ARP请求报文获取目的端口的MAC地址,同时存入本地ARP地址表,然后在进行以太网包的封装时填入目的MAC地址、目的IP地址,二层交换网络解析收到以太网包,判断目的MAC地址,将数据转发至相应的同步串口转MII模块,再由该模块进一步解析以太网包中的目的IP地址,分离出同步串口数据至目的端接口。

图8 同步接口时钟同步的实现

V.35、K口等业务接口要求实现时钟同步,本方案采用自适应同步法实现该功能[5],如图8所示,发送接口时钟TXC通过锁相环1产生n×64K时钟(K口接口时钟频率即为n×64K,不需经过该环节,V.35接口时钟需升至2.048MHz,锁相环2过程相反),同步串口转MII模块根据此时钟信号在数据的IP封装时中增加时间戳信息,经过二层交换网络,数据到达目的端同步串口转MII模块,该模块根据时间戳信息恢复出n×64K时钟,锁相环2根据该时钟产生RXC,经过接口转换后产生最终的业务接口输出时钟。终端输出时钟与源端输入时钟在频率、相位上存在一定的锁定关系。

4 其它说明

硬件总体设计、逻辑实现是本方案的重点,此外方案还包含简单的软件设计工作,主要用来实现LIU的初始化、同步串口速率的设定、IP及MAC地址的设置、网络管理等常规功能,本文不再另行描述。

本方案已经过实际测试,各项功能、性能满足应用需求,以E1接口点对点业务为例,24小时无误码,最小传输时延为4ms,输出抖动指标可达到SDH承载的E1接口同类级别。

为提高方案的安全性、隔离性,原则上根据业务类型划分IP段,不同的业务处于不同的网段。

5 结语

本方案具有良好的扩展性,可根据应用需求,在原有设计的基础上,于传统业务接口侧增加两线音频(电话)、ISDN、X.21等接口。本方案推广前景广阔,在军民用领域如专用通信指挥车、船舶、地铁及轻轨、企业专网等多业务接口IP化方面可得到广泛应用。

[1]何立民.I2C总线应用系统设计[M].北京:航空航天大学出版社,1995,2:5-240.

[2]胡世祥,段双泉,尚学琨,等.数据通信技术[M].北京:国防工业出版社,2001,1:157-158.

[3]P5009/CP5008/CP5004datasheet,2007:29.http://www.chiphomer.com.

[4]linx,Inc.Spartan-6Family Overview,2011:1-2.http://www.xilinx.com.

[5]唐剑峰,徐荣.PTN—IP化分组传送[M].北京:北京邮电大学出版社,2009,10:196-199.

[6]张炜,沈德刚.基于FPGA的PCI总线接口设计与实现[J].计算机与数字工程,2009(5).

[7]麻志鹏,沈小林.PCI总线接口的FPGA设计与实现[J].计算机与数字工程,2011(2).