基于ARM的DSP与FPGA动态配置方案的设计与实现*

2013-08-10吴冬梅何管清

吴冬梅 何管清 邱 昊

(1.海军司令部四部 北京 100841)(2.解放军61541部队 北京 100094)(3.海军工程大学电子工程学院 武汉 430033)

1 引言

近年来,随着数字信号处理器(DSP)和现场可编程门阵列(FPGA)等信号处理器件性能的不断提高,通信系统向小型化高速化方向迅速发展。DSP适合完成结构较复杂的信号处理算法和控制任务,FPGA适于完成高实时性、大运算量的信号处理任务[1]。DSP+FPGA系统使两者优势互补,既能满足灵活的上层信号处理算法又兼顾了底层信号处理的速度。

DSP与FPGA的配置数据存储在片内SRAM单元中,这种存储单元是易失的,系统掉电后数据不会被保存。因此上电后需要对芯片进行配置。传统的外部ROM配置方式将配置数据存储在专用的存储器中,上电后系统自动加载。这种配置方式结构简单,操作方便,不需要额外的软件开销,但需要配备专用的程序存储器件,增加了成本,同时也制约了系统的灵活性。

在某通信系统设计中,使用ARM对DSP和FPGA进行动态加载。ARM选用了三星公司的S3C6410;FPGA选用了ALTERA公司StratixII系列的EP2SGX30D;DSP选用了TI公司的TMS320C6416。下面对系统实现进行说明。

2 FPGA配置方案

ALTERA公司的FPGA芯片主要配置方式[2]有主动串行(Active serial,AS)模式、被动串行(Passive Serial,PS)模式、快速被动并行(Fast passive parallel,FPP)模式和远程配置方式等。芯片上的 MSEL[3:0]管脚决定了具体配置方案。在AS配置模式,FPGA通过专用的串行配置芯片加载程序。在被动配置模式下,微处理器、专用加载芯片或电缆线都可以作为配置数据发送方。由于管脚数目限制本设计不考虑并行模式。本文中ARM通过PS模式配置FPGA。

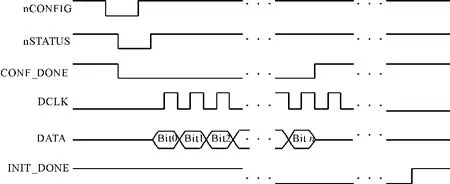

图1 被动串行配置时序

PS配置过程主要分三个阶段:复位,引导配置,初始化。配置时序如图1所示。

复位阶段。系统上电后,FPGA进入复位状态,复位信号释放前,nSTATUS与CONF_DONE信号拉低,所有输入输出引脚处于三态状态。

配置阶段。微处理器将nCONFIG拉高,使其产生一个上升沿,结束复位状态。nSTATUS信号由上拉电阻拉高,芯片进入配置模式。微处理器向FPGA提供时钟和配置数据,数据在时钟上升沿锁存。在配置过程中,片选信号nCS为低。

初始化阶段。FPGA正确接收所有配置数据后,CONF_DONE信号被上拉电阻拉高,此时表明配置过程完成,芯片进入初始化阶段。如果在配置过程中发生错误,nSTATUS变为低电平,CONF_DONE保持为低。

3 DSP配置方案

接收到复位信号后,DSP芯片被初始化为预先设定的复位状态。复位信号释放后,处理器按照硬件配置方式进行启动。DSP启动方式有:主机启动、ROM启动和不启动[3]。本设计中 ARM 通过主机接口(Host-Port Interface,HPI)加载DSP。

3.1 主机接口

主机可以通过HPI接口直接访问DSP内存空间。该接口为并行接口,C64x芯片主机接口数据宽度有16位和32位两种模式,分别称为HPI16与HPI32。HPI接口通过EDMA控制器与内存空间连接,因此主机访问DSP内存空间时不需要DSP的CPU直接参与。主机通过操作3种HPI寄存器实现对DSP内存访问,分别是控制寄存器(HPIC)、地址寄存器(HPIA)、数据寄存器(HPID)。

3.2 主机加载流程

当DSP硬件配置为主机加载模式并且PCI使能禁止时,主机可以通过HPI对DSP进行加载。DSP复位后,CPU处于停转状态,器件的其他部分则被释放。将所有必要数据写到DSP内存后,需要给DSP一个内部硬件中断以唤醒CPU。当DSP从地址0开始运行后要将该中断清除,否则后续主机中断不能被正确接收。HPI加载流程[4]如图2所示。

图2 HPI启动流程

HPI16加载软件流程可总结为:

2)初始化寄存器HPIC。

3)向DSP传送配置数据。主要通过操作HPIC,HPIA和HPID三个寄存器来实现。当前操作的寄存器通

4)将配置数据按顺序写到DSP内存,然后将HPIC中DSPINT位置1。

4 系统设计与实现

图3 系统硬件连接图

ARM的通用输入输出脚作为FPGA加载的控制信号。PS模式用到的信号线只需五根,设计中将FPGA这些信号线连接至 ARM 的通用I/O管脚,其中nCONFIG、DCLK、DATA设置为输出,用于配置FPGA;nSTATUS和CONF_DONE设置为输入,用于检测配置状态。理论上配置时钟越高加载速度越快,但配置时钟过高使控制信号建立保持以及数据锁存时间难以把握。EP2SGX30D配置时钟允许的最高频率为100MHz,本系统所采用的配置时钟为5MHz。

系统的硬件连接如图3所示。本设计中ARM的地址线AMR_A[4∶1]复用为HPI接口的控制信号。控制信号

5 结语

本系统设计的动态加载方案使主机可以根据用户需要灵活切换不同的软件波形,在一个通用硬件平台上实现功能模块化、软件化。同时,该方案也为后续软件升级提供了便利,具有较高的使用价值。

[1]汉泽西,孙燕妮.DSP+FPGA技术[J].电子技术,2007,2(4):18-20.

[2]Altera Corporation.Stratix II Device Handbook[EB/OL].(2001-10-09)[2011-04-09].http://www.altera.com.

[3]Texas Instruments Incorporated.TMS320C6414,TMS320C6415,TMS320-C6416Fixed-point Digital Signal Processors[EB/OL].(2006-01-10)[2011-06-19].http://www.ti.com.

[4]Texas Instruments.Implementing the TMS320C6201/C6701/C6211HPI Boot Process [EB/OL].(2002-12-22)[2011-11-01].http://www.ti.com.

[5]熊康碧,张伟.DSP+FPGA系统中FPGA的动态重构设计[J].计算机与数字工程,2010,38(10):190-192.

[6]胡修林,席向涛,张蕴玉.嵌入式系统中FPGA的被动串行配置方式[J].单片机与嵌入式系统应用,2004,40(3):22-26.

[7]陈曦,沈佐峰.一种可靠的FPGA动态配置方法及实现[J].通信技术,2012,3(45):105-107.

[8]尹涛,潘丽辉,袁行船.网络环境下ARM对DSP系统软件加载的设计和实现[J].舰船电子工程,2007,27(5):138-139.

[9]吴海燕,张晓玲.一种基于TMS320C6000系列芯片的多DSP程序动态加载方案[J].电子元器件应用,2008,10(12):12-14.

[10]张力,夏勇,陈志勇.基于TMS3206416DSP/BIOS的FLASH引导方式的实现[J].舰船电子工程,2008,28(2):77-79.

[11]熊康碧,张伟.DSP+FPGA系统中FPGA的动态重构设计[J].计算机与数字工程,2010(10).

[12]刘静,黄康.TMS320C641X系列DSP引导方法研究[J].现代电子技术,2010,332(21):207-210.