高速多通道数据采集系统的时钟同步设计

2013-08-10邱桂芬朱拥建

邱桂芬,朱拥建

(上海微波设备研究所,上海201802)

0 引 言

随着雷达、通信技术的进步,信号朝着密集化、复杂化的方向发展,电磁环境日趋复杂,而且占用的频谱越来越宽。采用高速多通道数据采集系统对接收信号进行参数估计、测量已成为目前常用的技术手段之一。

与单通道高速数据采集相比,多通道高速数据采集的最大不同之处在于其时钟电路。单通道数据采集不存在同步的问题,而多通道数据采集则必须保证每个模数转换器(ADC)采样时钟的同步性,否则如果采样时钟的相位有偏差则最后反映到不同通道间的数据存在一定的相位误差。

1 系统需求

本系统要求能够对4路中心频率为400MHz、带宽为200MHz的中频信号进行同步采集,系统的采样频率为550MHz。通道间的相位一致性要求小于2°,幅度一致性要求小于0.5dB。

2 方案设计

时钟信号质量是决定采集系统性能的关键,也是高速多通道数据同步采集的难点,设计时需要精心考虑[1]。反映时钟质量的指标主要有2个:相位噪声和相位抖动。在高速、高分辨率的ADC电路中,采样时钟的微小抖动将大大降低ADC转换器的信噪比,使其有效位数减小,从而影响多路ADC的同步采集。

由于4路ADC采样时钟高达550MHz,为了实现4片ADC的同时采样,设计中对4路采样时钟的频率、相位、占空比、抖动等都有很高的要求。为了减小时钟相位的抖动和采样时钟的偏移,在时钟同步的设计上采取了一系列的措施[2]。

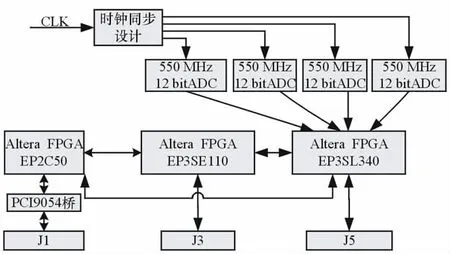

时钟同步电路原理框图如图1所示。时钟信号经单端转差分芯片后进入时钟分配芯片,再经4片可编程时钟延时芯片调整后作为4路ADC的采样时钟。

图1 时钟同步电路原理框图

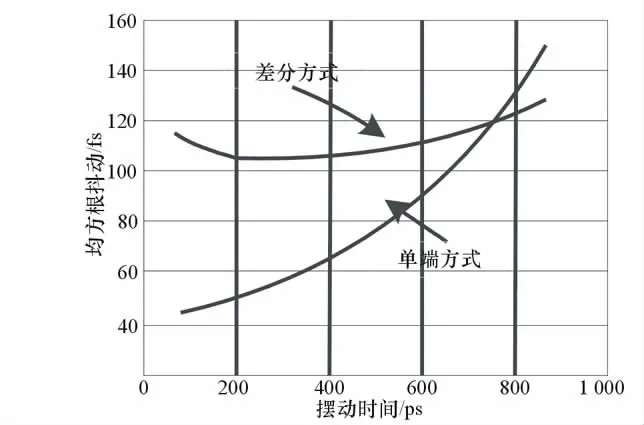

图2 差分馈入和单端馈入方式下的摆动时间与均方根抖动的关系

3 电路设计

3.1 单端转差分电路设计

ADC的时钟信号馈入方式一般有单端和差分2种,图2为2种馈入方式下摆动时间与均方根抖动的关系。

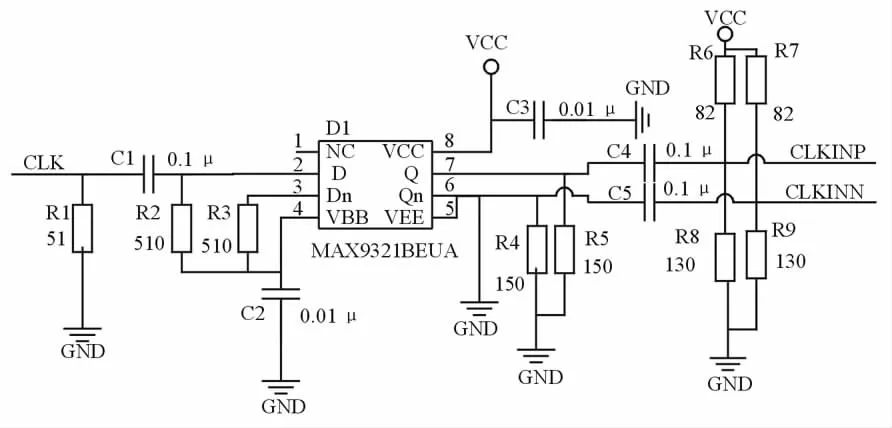

差分馈入方式的优点是可以提高时钟信号的转换速率,降低ADC的孔径抖动,从而提高ADC的信噪比,不过电路要复杂一些。为提高系统性能,ADC的采样时钟选用差分馈入方式,单端转差分芯片选用美信公司的MAX9321BEUA,外围电路图如图3所示。

图3 单端转差分电路图

设计中需要注意的是MAX9321BEUA的输出为低电压伪发射极耦合逻辑(LVPECL)电平,输出端一定要下拉1个电阻到地,否则没有输出。后续的电阻网络是电平匹配网络,可根据具体设计需要做相应的调整。

3.2 时钟分配电路设计

要实现4路ADC同时采样,每路ADC的时钟必须是由同一个时钟源产生,因此需要一个时钟分配芯片提供多个时钟副本。

在本设计中时钟分配芯片采用安森美公司的MC100EP111,这是一款低抖动的非锁相环结构的1:10信号扇出缓冲器,该芯片具有如下优点:

(1)2∶1差分输入选择器;

(2)附加抖动在0.5GHz内小于0.2ps;

为加大部门联合执法力度,广东省水利厅和广东省公安厅联合印发了《广东省水行政主管部门与公安机关执法协作规定》,初步形成了水利与公安联合执法机制,并在省政法委的领导下,积极参与行政执法与刑事司法衔接信息共享平台建设,作为成员单位录入了行政执法基础信息,按规定做好“两法衔接”工作。此外,广东省水利厅与广东省环保厅联合发文,在东江的惠州、东莞两市先行先试,逐步推动水利和环保建立联合执法机制,不断提高水政执法效能。

(3)器件的最高工作频率高于3GHz;

(4)典型的器件抖动85ps;

(5)通道间的歪斜小于20ps。

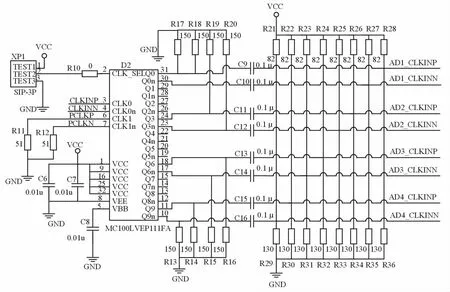

该电路连接方式如图4所示。CLKINP、CLKINN这一对时钟输入为外部时钟输入,PCLKP、PCLKN为晶振所产生的内部时钟输入,设计中通过调整(置高或置低)管脚CLK_SEL来选择内外时钟。

图4 时钟分配电路图

3.3 时钟延时电路

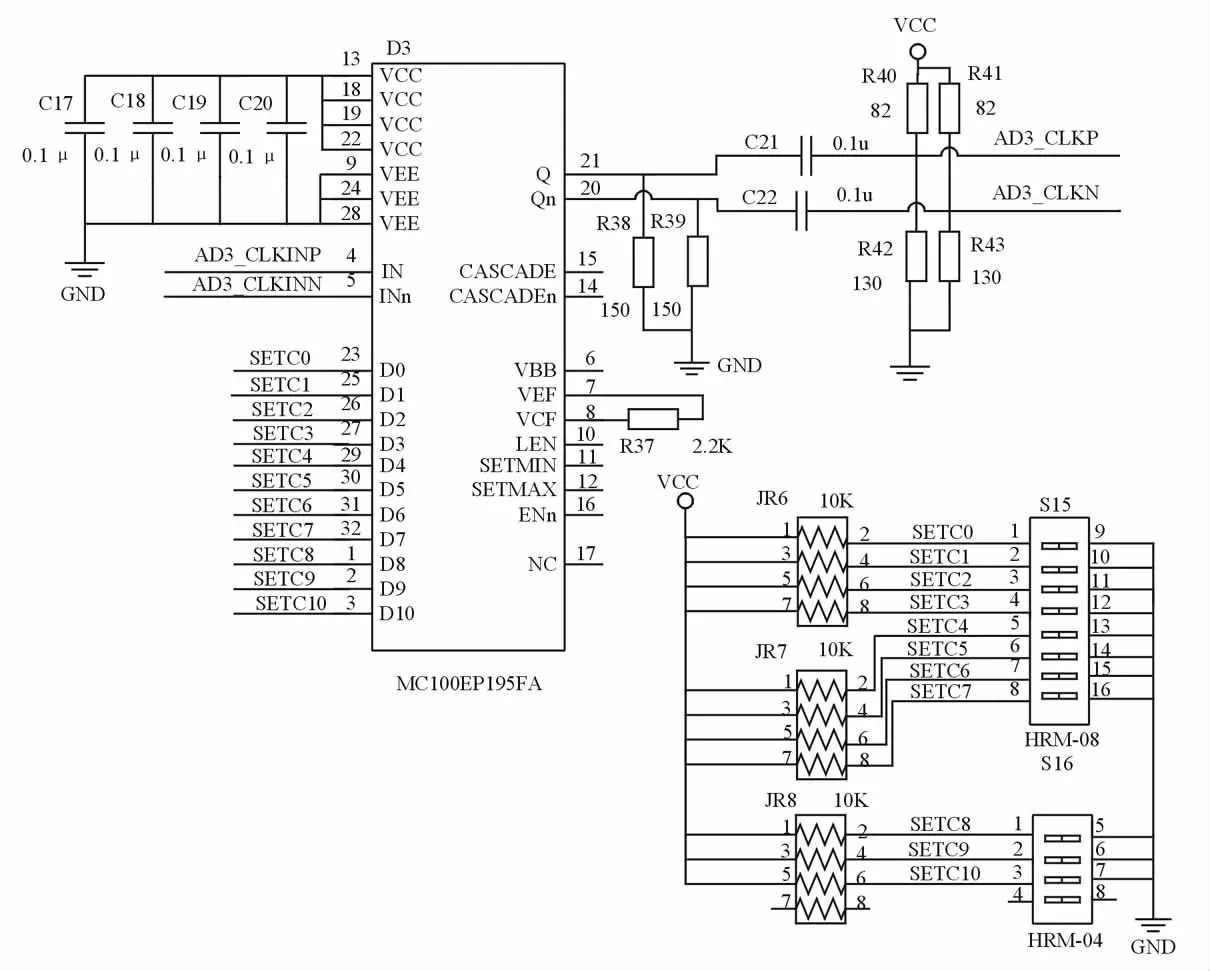

理想的时钟分配输出信号应该完全同相,但实际上由于时钟分配器件是一个非理想器件,因此其输出的时钟存在一定程度的歪斜和附加的时钟抖动[3]。为了校准器件、制板和焊接等因素引入的时钟误差,在时钟分配电路后加入了一级可编程时钟延时芯片[4]。在本设计中选用了安森美公司的MC100EP195,这是一款可编程延迟芯片(PDC),主要用于时钟去扭曲和延时调整。该款芯片有如下优点:

(1)2.0ns最坏情况延迟范围;

(2)10ps/Delay步进分辨率;

(4)1.0GHz的带宽。

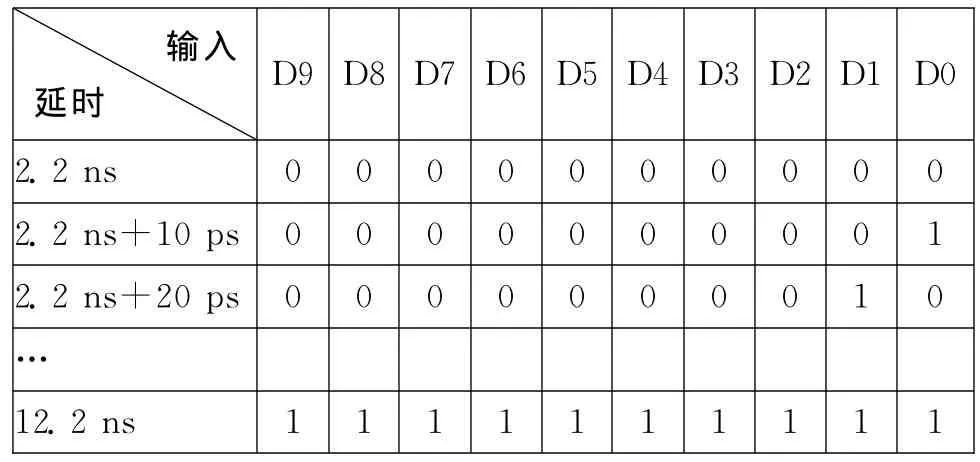

该电路连接方式如图5所示。可通过拨动开关S15和S16改变输入端D[10..0]的电平值,从而调整各路时钟的时延。输入端D[10..0]电平与延时量的对应关系如表1。

实际工作时通过拨动开关S15和S16调整芯片的输入端D[9..0]来实现。延时情况如表1所示。

表1 输入端D[9..0]电平与延时量对应关系表

4 布局布线

高速数据采集系统中的时钟同步电路对器件布局和布线有较高要求,在设计中应主要注意以下几方面:

(1)AD时钟线布局时不要太靠近其他高速数字源,否则会造成时钟线上的抖动,也不要布在其他模拟区,否则会增加其他模拟区上的噪声;

(2)时钟分配芯片的4路输出要等长设计,本设计中,其长度差不应超过76.2μm,经时钟延时芯片后进入ADC的4路时钟线长度差也不应超过76.2μm;

(3)时钟信号的布线要短而粗,进入ADC的时钟走线越短越好,应尽量将时钟源紧靠ADC,以保证同一时刻4路ADC芯片时钟输入端的相位关系,具体实现可通过走蛇形线来满足时钟一致性。

图5 时钟延时电路图

5 测试结果

本时钟同步电路在系统中的应用原理如图6。时钟信号经时钟同步电路后,分成4路分别作为4路ADC时钟输入,基于此设计可实现4路ADC的同步采集。经测试,4路通道间的幅度一致性优于0.5dB,相位一致性小于2°,满足系统使用要求。

图6 时钟同步电路应用原理图

6 结束语

本文所述的时钟同步电路已成功应用于工程项目中,并已通过技术鉴定与设计定型。目前高速多通道数据采集技术仍在不断发展中,在多通道同步方面,若能进一步降低时钟的抖动,通道间的一致性会更好。

[1]张雪萍,童子权,任丽军.高速采集系统中时钟的设计[J].国外电子测量技术,2006(9):25-9.

[2]童子权.1GHz高速数据采集时钟系统的设计[J].哈尔滨理工大学学报,2007(6):12-3.

[3]张福洪,杨小梅,栾慎吉.基于AD9516的宽带高动态数字中频系统采样时钟设计与应用[J].电子器件,2009(12):32-6.

[4]王和国,张玉静,刘书明.基于AD9516的高速四通道时间交叉采样时钟的设计[J].国外电子元器件,2008(6):7-9.