基于FPGA的16位CPU设计

2013-08-03马军爽

马军爽

(唐山学院 信息工程系,河北 唐山063000)

0 引言

随着我国信息化进程的不断推进,计算机技术还将对我国的生产力的发展产生日益深远的影响。 近年来我国在CPU 设计领域取得了一些重大突破,相继研制出龙芯系列、方舟系列高性能CPU,此外位于台湾的威盛电子也是较大的处理器生产商。 然而我国的CPU 设计及制造技术与国外相比还有很大差距, 我国信息产业中与CPU 相关的许多核心技术及产品仍然主要依赖进口,不仅经济上受制于人,而且信息系统的安全乃至国家安全也面临威胁。 FPGA 技术自20 世纪80年代中期出现至今,引起了电子设计技术的深刻变革,也成为现代电子设计技术的核心。 因此,基于FPGA 技术的CPU 设计具有较高的研究价值。

1 16 位CPU 的流水线结构设计

流水线(pipelining)是提高CPU 运行效率的关键技术。 和工业流水相似,流水线的核心思想是把多条指令的执行重叠起来。 在任何时候,CPU 同时处理多条指令,这些指令分处于不同的运行周期,使用不同的物理器件。

在流水线CPU 中, 每条指令的指令执行过程被分成若干个执行阶段。只有当每一个执行阶段都完成之后,一条指令才算执行完毕。在每一个指令执行阶段中,当一条指令在该阶段中完成执行之后,下一条指令将立即进入到该执行阶段开始执行。 当流水线处于饱和状态时,CPU 中将有与流水线级数相同数目的指令在同时执行, 本设计将流水线分为4 个阶段,每一个执行阶段的名称和功能如下∶

1)IF∶取指令阶段;

2)ID∶指令译码阶段;

3)EXE∶指令执行阶段;

4)PPR∶后处理阶段。

2 16 位CPU 主要模块设计

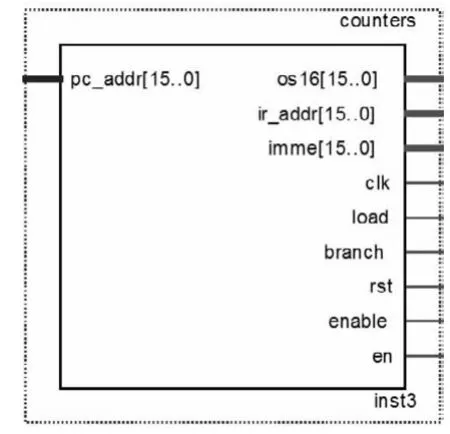

2.1 程序计数器模块的设计

程序计数器的模块结构如图1 所示, 其中pc_addr 为16 位数据输出端口,os16 为CPU 与操作系统的接口,enable 为其控制端,当enable 为高电平时os16 输入有效。ir_addr 和imme 分别为分支和跳转指令的指令运算所需要的16 位扩展加数输入端口。 en 为该模块的使能控制输入信号,load 和branch 分别为跳转和分支控制信号。 该模块的功能为∶ 在时钟作用下, 当跳转和分支控制指令为低电平时,pc_addr 地址加1。

2.2 指令寄存器模块的设计

此模块的结构图如2 所示, 其中data 为16 位数据输入端口,ena为该模块的使能信号端口,clk 和rst 分别为时钟和复位信号端口,instr 为16 位数据输出端口。

此模块的功能是在ena 信号为高电平的条件下将16 位输入指令数据送给16 位输出端口instr。

图1

图2

2.3 ALU 模块设计

此模块结构如图3 所示, 其中a 和b 为16 位操作数输入端口,aluop 为4 位的alu 操作码信号输入端口,shift 为4 位的偏移量信号输入端口,result 为16 位的结果输出端口。 此模块为CPU 的核心运算模块,其功能为在aluop 的控制下进行各种算数、逻辑及移位运算操作。ALU 操作码aluop 并不是指令中的操作码部分,而是经由指令译码模块产生的控制信号。

图3

2.4 指令译码模块的设计

此模块为CPU 的逻辑控制及调度中心, 它的功能是根据输入指令的类型及特点产生一系列的控制信号,协调其他模块正确滴完成指令的执行过程。

2.5 通用寄存器堆的设计

通用寄存器堆模块为CPU 的通用数据集散中心, 它既可以为指令的执行提供操作数,也可以存储运算处理的结果,还可以和主存进行数据交换。 此模块采用通用RAM 模块的设计思想,在普通的RAM基础上扩展相应的数据及地址输入输出端口实现了通用寄存器堆的功能。

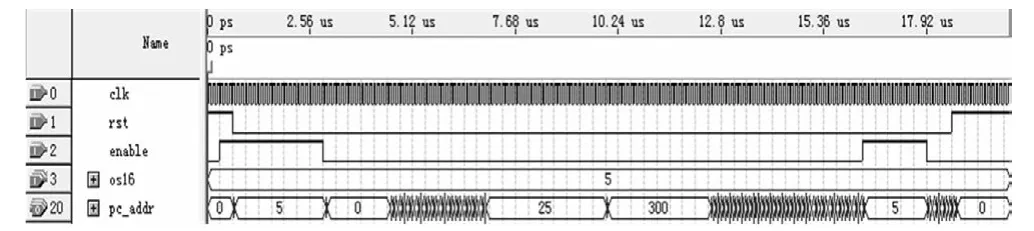

3 CPU 的结果测试

本设计采用的验证方式是设计相关的外围模块,通过实际运行测试程序来验证CPU 的方法。这种方法更具体更实际。图4 为本设计的16 位CPU 由os16 端口装入程序首地址的操作的时序仿真结果。

图4

通过仿真结果可以看出,本设计中的处理器功能正确,能实现定点加减法运算、逻辑运算、移位运算、数据传送、指令跳转等功能,控制逻辑及数据通路的时序匹配合理,运算速度快,精度高。

4 结论

本设计根据FPGA 技术的特点, 提出了一种基于FPGA 的16 位CPU 的设计方法。设计中采用了自顶向下、模块化的设计思想,将整个CPU 的设计分各个功能模块,利用VHDL 语言进行了各个功能模块的设计,最后采用原理图的方法将各个模块组合成一个完整的微处理器内核。 本设计对16 位的CPU 设计方法进行了探讨,研究了片上系统的设计方法和技术,为实现高性能的CPU 设计提供了研究基础,有较高的研究价值。

[1]朱子玉,李亚民.CPU 芯片逻辑设计技术[M].北京∶清华大学出版社,2005,01.

[2]张洪润,张亚凡.FPGA/CPLD 应用设计200 例[M].北京∶北京航空航天大学出版社,2009,01.

[3]王赋攀,毕国堂.一种基于FPGA 和软核CPU 的嵌入式系统设计方法[J].电脑知识与技术,2007,06.

[4]江先阳,沈绪榜,张天序.基于ARM 核的嵌入式CPU 内AHB 接口的实现[J].通信学报,2002,07.