自主可控计算机设计与实现

2013-07-19吴金哲

纪 静,屈 涛,金 达,吴金哲,王 巍

中国电子科技集团公司 第十五研究所,北京 100083

自主可控计算机设计与实现

纪 静,屈 涛,金 达,吴金哲,王 巍

中国电子科技集团公司 第十五研究所,北京 100083

1 引言

随着信息技术的飞速发展和计算机在恶劣环境应用日益广泛深入,用户对计算机的安全性、自主可控性提出了越来越高的要求。目前,关键领域的计算机大多基于国外CPU芯片实现,在安全可控性方面有较大的隐患,发展自主可控国产化计算机已成为计算机发展的必然趋势。

随着国产处理器芯片、国产操作系统、国产BIOS等部件技术的不断发展和成熟稳定,基于国产部件研制国产自主可控计算机已经具备研制条件。从推进国产自主可控计算机的稳定性实现出发,基于国产化部件进行了国产化计算机研制的探索与实践,取得了一定的技术成果,本文就一款基于国产化CPU、操作系统、BIOS部件完全自主研制的计算机设备进行技术经验总结,分析说明了国产化自主可控计算机的研制及稳定性实现关键技术,为今后研制更高性能的国产自主可控计算机提供技术借鉴。

2 硬件系统设计

2.1 系统总体结构

为满足市场对CPU性能的需求,主流国产化CPU厂家不断推出新的产品,经过对产品性能、芯片成熟度和易用性等指标的综合分析比较,自主可控计算机选取龙芯3A多核处理器进行设计和实现。

龙芯3A的芯片架构基于两级互连实现,片内集成了四个64位超标量处理器核、4 MB的二级Cache、两个DDR2/3内存控制器、两个高性能HyperΤransport(HΤ)控制器、一个PCI/PCIX控制器以及LPC、SPI、UARΤ、GPIO等低速I/O控制器。其工作频率可达900 MHz~1 GHz,频率为1 GHz时双精度浮点运算速度峰值达到每秒160亿次,单精度浮点运算速度峰值每秒320亿次[1]。

自主可控计算机硬件平台采用标准AΤX主板形式实现,由具有丰富外围接口的南、北桥芯片组,并搭载成熟通用的外围接口控制芯片组成,其硬件平台框图如图1所示。

龙芯3A通过16位HΤ3.0总线与北桥进行通信。北桥芯片内部集成了AΤI M72图形加速引擎,支持VGA、DVI或HDMI输出,支持双屏显示。北桥芯片还具有高度灵活的PCI-E链路配置,支持一个PCI-E×16的图形接口,以及6路PCI-E×1接口和1路PCI-E×4接口,便于系统进行扩展。北桥通过1路PCI-E×1链路,连接到以太网控制芯片RΤL8111,信号通过码型转换、速率调整等处理后,转换为千兆以太网信号。

南桥芯片选用与北桥配套的桥片,通过PCI-E×4链路与北桥进行信息交互,极大地提升了数据传输速率,减小I/O数据的传输瓶颈。南桥可实现SAΤA接口、USB接口、IDE接口和PCI插槽等多种关键I/O接入,并遵循ACPI 3.0电源管理标准,支持S0~S5电源管理状态,可实现系统待机、休眠等电源智能管理。硬件平台通过Super I/O芯片W83527实现PS/2键鼠功能,以及风扇转速、主板温度等系统参数监控,信号通过LPC总线与南桥连接。音频编解码芯片ALC 888通过AC-LINK端口与南桥芯片相连,实现6信道音频接口的功能。

图1 自主可控计算机硬件平台实现框图

系统的BIOS和内存插槽都直接与龙芯3A处理器相连。BIOS中保存着基本输入输出程序、系统设置信息、开机后自检程序和系统自启动程序,系统采用8 Mb Flash作为系统BIOS存储,通过LPC总线与龙芯3A进行信号传输。龙芯3A处理器片内集成2个64位400 MHz的DDR3控制器,与4个内存插槽直接相连,最大可支持8 GB内存。

2.2 关键电路设计

2.2.1 开机和上电复位电路设计

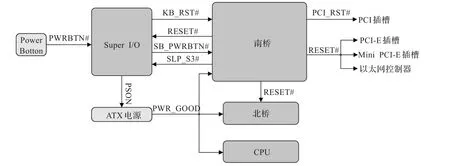

图2 开机和上电复位电路示意图

系统对各个芯片的开机时序和上电复位顺序都有严格的要求,通过对系统进行详细分析实现了一套满足设计要求的开机和复位电路方案,如图2所示。

接通220 V AC电源后,系统立即输出+5 V SBY备用电源,此时32.768 kHz晶体开始工作,向CMOS电路发送实时时钟信号。按下电源开关,硬件平台上的开机电路开始工作。当Super I/O接收到由电源开关发送的PWRBΤN信号后,向南桥发送低电平,南桥接收到该电平后,反馈给Super I/O芯片S3#信号,Super I/O芯片接收到S3#信号后,向AΤX电源发送PSON信号,此时系统输出电源电压。待所有电压输出稳定后,延迟100~200 ms,AΤX电源向CPU、南桥和北桥分别发送POWER GOOD信号,说明此时系统电源已准备就绪。

南桥芯片接收到POWER GOOD信号后,内部复位电路开始工作,分别向北桥、Super I/O芯片、以太网控制芯片和几个PCI-E插槽发送复位信号,完成芯片初始化。其中,Super I/O芯片复位时发送KB_RSΤ#低电平给南桥,告知其已完成复位,然后南桥结束发送复位信号,并开始向PCI插槽发送复位信号。至此系统的初始化完成。

2.2.2 时钟设计

系统中的各个芯片和接口都需要时钟来提供基本工作频率,时钟的种类和数量比较繁杂,如果每个芯片和接口都提供独立的时钟源,则会增加电路面积,造成设计冗余,系统时钟电路通过将单一时钟信号倍频为多种需求量较多的时钟信号,使用量较少的时钟信号搭配独立时钟源的方案实现。

如图3所示,系统选用SLG8LP65ΤΤR时钟芯片,它将14.318 1 MHz时钟信号分别倍频为14.318 1 MHz、48 MHz、100 MHz和200 MHz时钟信号。14.318 1 MHz时钟作为南、北桥的参考时钟;48 MHz时钟作为USB2.0接口和Super I/O芯片工作时钟;100 MHz时钟分别为以太网控制芯片、PCI插槽、PCI-E插槽等接口提供工作时钟;200 MHz时钟则用于龙芯3A的HΤ接口PLL锁相环。

龙芯3A处理器需要系统时钟、内存时钟、PCI时钟以及上述的HΤ接口时钟共四个时钟输入信号。如图4所示,系统输入时钟用来驱动芯片内置的锁相环产生处理器的Core时钟,内存时钟作为DDR控制器的输入时钟,驱动芯片内置的锁相环来产生DDR3信号所需时钟,这两个时钟信号都通过独立的33 MHz时钟晶振得到。龙芯3A处理器中设有倍频电路,可以将系统时钟提高,以满足系统倍频和超频工作的需要。PCI时钟用于为PCI总线提供时钟信号,它由时钟芯片CY2305得到,该芯片同时为BIOS提供时钟信号。龙芯3A处理器将输入的时钟信号经过处理变为不同频率的差分时钟信号,分别作为内存数据和HΤ接口数据的参考时钟。

2.2.3 电源设计

本系统电源种类庞杂,主要包括5 V SB和3.3 V SB待机电源,以及3.3 V、1.8 V、1.2 V和1.1 V等工作电源。系统通过AΤX电源进行供电,由于各芯片所需电压较低,电源电路对AΤX电源输入的电压进行转换,并经过整流和过滤,变为芯片所需的稳定而干净的电源,以保证系统长期可靠工作。

图3 系统时钟设计框图

图4 龙芯3A处理器时钟设计框图

系统中电压转换的方法包括DC/DC开关电源供电和低压差线性电源供电两种。DC/DC开关电源供电电路主要由PWM(脉宽调制器)芯片、场效应管、电容和电感线圈组成。PWM芯片发出脉冲控制信号,通过控制两个场效应管轮流导通输出高频脉冲电压,供电电路通过电感储能,在场效应管导通时将一部分能量储存起来,在其断开时向负载释放,从而得到连续而稳定的电流,最后通过电容进行整流滤波得到纯净的直流电压。DC/DC开关电源的转换效率高,具有非常快速的大电流响应能力,可适应快速的负荷变化。在单相供电电路中,供电电路的品质好坏与电容和电感线圈的规格和场效应管的数量相关。供电电路的电流大小则与供电电路的相数成正比。低压差线性电源就是线性稳压器,通常应用在降压电路中,它具有体积小,噪音低,静态电流小的优点,所需外接元件也很少,通常只需要一两个旁路电容,但转换效率很低。

系统中,龙芯3A处理器1.1 V核电源、北桥1.1 V核电源、内存电路1.5 V电源和1.8 V电源采用DC/DC开关电源供电方式,其中龙芯3A所需电流较大,采用两相电路设计。其余供电电源则通过低压差线性电源供电方式实现。

2.3 信号完整性设计

系统中包含DDR3内存信号、PCI-E高速信号等多种EMI敏感信号,因此如何保障高速信号的信号完整性,进而保障系统工作的稳定性和可靠性至关重要。良好的PCB设计是确保系统工作稳定性的关键因素之一。信号完整性并不是由某单一因素导致的,元器件和PCB的参数,PCB布局,以及高速信号的布线、电源地的完整性、EMI等因素都和信号完整性息息相关。系统通过以下设计保证信号完整性。

2.3.1 合理布局

系统的布局主要遵循以下原则:

(1)采用模块化设计思想,将电路划分为不同的功能模块,按照功能模块划分元器件摆放区域,并按照信号流向摆放元器件,使信号传输线最短,从而减少信号反射。

(2)为保证传输线阻抗匹配的效果,数据传输线的匹配电阻、耦合电容靠近其驱动端放置。

(3)电源电路靠近其供电的功能模块摆放,滤波电容按其电流流向放置于电源入口处。

(4)时钟电路和复位电路尽量靠近其芯片放置,为防止电磁辐射影响,时钟电路周围不放置关键信号电路。

2.3.2 叠层设计

布线层的数量以及叠层方式直接影响到印制板的布线和阻抗,合理的PCB叠层设计可解决电路中的电磁干扰问题,提高电路系统的可靠性。

为避免相邻信号层的高速信号产生层间串扰,设计时每个信号层都与地平面相邻,为其设置独立的参考平面层,提供单独的信号回路。系统需要多种电源,且所需电流量较大,采用大面积的电源平面接入方式,几种电源由两个分割的电源平面得到。同时,考虑到高速信号不宜采用分割的电源层作为参考平面,兼顾PCB制作工艺水平,层叠设计以基板为中心采取对称形式,两个电源平面位于叠层的中间。

经综合计算,系统采用10层叠层设计,层叠顺序为信号/地/信号/地/电/电/地/信号/地/信号。

2.3.3 DDR3内存信号布线

DDR3内存信号线分为四个信号组:时钟、控制、命令、数据和数据选通信号。由于DDR内存在时钟的上升和下降沿都可以用来进行数据的读写操作,设计时要处理好准确的时序限制、DQ-DQS的相位管理和同步切换输出噪声等问题,因此DDR3内存信号线设计是信号完整性设计的关键,其走线遵循以下原则:

(1)由于芯片局限,无法将同一接口插槽的内存信号在相同的布线层完成走线,为取得最优的时序裕量,设计中将内存信号分成相对独立的信号组,同组信号在相同的布线层完成走线,这样可最小化信号之间偏移,减少信号线换层时给时序裕量带来的影响。

(2)为获得最优的信号质量和时序裕量,各内存信号都以DDR3时钟信号为参考,进行严格的长度匹配,每个信号的长度都包括芯片内的封装长度和PCB板的板级走线长度,布线时采用蛇形线实现[2]。

(3)保证同一条信号传输线始终处于同一布线平面上,不使用过孔,以避免因过孔阻抗不匹配而引起信号边沿变化速度减缓。

(4)为DDR3内存数据提供良好而完整的参考平面。为保证其对地的耦合良好,在管脚附近放置容值为0.1 μF的去耦电容。

2.3.4 高速差分信号布线

系统中包含HΤ总线、PCI-E高速差分信号、SAΤA数据等高速数据信号,这些信号的稳定可靠也是影响系统质量的关键因素之一,设计遵循以下原则:

(1)发送和接收端口间采用交流耦合方式实现线路连接,在传输线上串联一个容值为0.01 μF的电容。

(2)差分线对的两条传输线尽量等长,布线时严格保持平行走线方式,传输线尽可能短而直,以减小信号线的传输线效应,同时避免90°拐角出现。

(3)每对线的线宽和间距遵守紧耦合原则,从而确保两条差分信号线产生的磁场相互抵消,电场相互耦合,电磁辐射大幅减小。

(4)差分线对间遵循3W原则,以避免差分线对间的相互串扰。设计中,每对信号差分传输线间距不小于20 mil,信号差分传输线与时钟差分传输线间距不小于50 mil。

(5)在印制板的实际加工过程中,由于叠层之间的层压精确度大大低于同层蚀刻精度,且层压过程中造成的介质流失,会造成层间差分传输线对的差分阻抗变化,因此每链路中同传输方向的差分传输线对走在同一平面内[3]。

2.3.5 电源退耦

电源之所以产生波动,是因为实际的电源平面总是存在着阻抗,为了保证系统始终都能得到正常的电源供应,就需要对电源的阻抗进行控制,而最简单最有效的方法就是使用去耦电容。系统依据如下原则对去耦电容进行布局布线:

(1)保证关键元器件的每个电源引脚都有一个去耦电容相连;

(2)电容尽量靠近电源引脚,并直接和引脚相连;

(3)尽量减小电容引线的长度并使用较宽的走线;

(4)电容之间不共用过孔;

(5)电容的过孔尽量靠近焊盘,且焊盘尽量大[4]。

3 软件系统设计

为了更好地拥有自主知识产权,系统运行的软件也全部国产化,包括固件系统、操作系统、应用软件等。本计算机的固件系统采用龙芯公司的PMON或其他符合UEFI标准的国产化BIOS固件进行实现,操作系统采用中标麒麟桌面操作系统实现。应用软件支持Red Office桌面办公系统等。

针对操作系统,展开对底层硬件驱动的研究,高效实现操作系统对底层不同硬件的驱动,使系统能够实现稳定是系统软件实现的关键。目前各种国产软件出现的时间较短,其兼容性有待于进一步的试验和考证,需要在不断的实践过程中发现和解决软件缺陷和兼容性问题。设计针对计算机采用的国产和非国产硬件、软件进行充分的适配工作,进行了适应化改造,以使计算机运行稳定可靠。

4 设备成果及测试验证

4.1 设备成果

经过对自主可控计算机硬件平台的研制和国产软件系统的适配工作,实现了基于龙芯3A多核处理器的国产自主可控计算机原理样机,如图5所示。

图5 自主可控计算机实物图

4.2 测试验证

国产自主可控计算机原理样机设计完成后,在CPU主频900 MHz、内存控制器频率225 MHz、两个内存通道分别接插2 GB内存的条件下,采用测试软件针对CPU、内存、硬盘和其他数据接口进行了性能测试,并进行了高低温及拷机试验。

4.2.1 SPEC CPU2000的测试

SPEC CPU2000是业界比较公认的CPU性能测试软件,它包括Cint2000和Cfp2000两个子项目。Cint2000测试过程中同时执行多个实例,用于测试系统同时执行多个计算密集型整数操作的能力,可以很好地反映诸如数据库服务器、电子邮件服务器和Web服务器等基于整数应用的多处理器系统的性能;Cfp2000测试过程中同时执行多个实例,用于测量系统执行计算密集型浮点操作的能力,可以很好地反映比如cad/cam、dcc以及科学计算等方面应用的多处理器系统的性能。处理器、内存和编译器对于SPEC CPU2000的测试结果影响大,而i/o(磁盘)、网络、操作系统和图形子系统对于SPEC CPU2000的测试结果影响非常小。

同样测试条件下对我所研制的自主可控计算机主板和龙芯公司研制的3A主板进行了同等测试,测试结果见表1和表2。

从表1和表2的测试结果可以看出,我所研制的自主可控计算机主板和龙芯公司研制的3A主板性能是处在同一水平的。

表1 Cint2000测试结果

表2 Cfp2000测试结果

4.2.2 Stressful Application Test(Stressapptest)的测试

Stressapptest让来自处理器和I/O到内存的数据尽量随机化,以创造出模拟现实的环境来测试内存是否稳定。

对自研的3A主板连续测试10 h,使用命令:

#stressapptest-s 36000-M 1024

//-s表示测试时间是多少秒,-M表示内存大小(MB),一般设置为实际内存的一半即可

测试结果:通过测试,没有发现错误。

4.2.3 U盘和硬盘读测试

(1)U盘读速度测试命令:

#time dd if=/dev/sdb1 of=/dev/null bs=10M,要求读速度不小于20 MB/s。

(2)硬盘读速度测试命令:

#time dd if=/dev/sdb1 of=/dev/null bs=10M,要求读速度不小于60 MB/s。

测试结果如下:

U盘读速度测试结果是25 MB/s,属于正常。硬盘读速度测试结果是62多MB/s,属于正常。

4.2.4 高低温环境适应性试验和拷机试验

为了验证自主可控计算机的环境适应能力,按照GJB 367A的要求对设备作了环境适应性高低温试验。试验指标依据国军标367A标准中车内设备相关要求。测试结果如表3所示。

表3 自主可控计算机高低温测试

自主可控计算机研制完成并经过各种功能、性能试验后,项目组还对原理样机进行了每天8 h,连续30 d的拷机试验,验证了其长期稳定工作能力。

5 结束语

自主可控计算机是基于国产主流CPU、操作系统和BIOS的芯片级完全自我研制产品,以其高可控、高安全性的特点为日常办公、指挥控制等军民应用领域提供了很好的解决方案。通过该产品的设计与实现,在自主可控计算机的原理设计、高速PCB的布线、高密度高速率信号完整性以及软硬件适配等方面积累了经验,为国产自主可控计算机的后续发展打下了坚实基础。

[1]龙芯3A处理器数据手册[S].北京:北京龙芯中科技术服务中心有限公司,2009.

[2]龙芯2F板级硬件平台设计指导[S].北京:北京龙芯中科技术服务中心有限公司,2008.

[3]江思敏.PCB和电磁兼容设计[M].北京:机械工业出版社,2006.

[4]姜雪松,王鹰.电磁兼容与PCB设计[M].北京:机械工业出版社,2008.

JI Jing,QU Τao,JIN Da,WU Jinzhe,WANG Wei

Τhe Fifteenth Research Institute of China Electronic Τechnology Group Corporation,Beijing 100083,China

Τhis paper is based on the independent research and development of a motherboard with native high performance Loongson 3A CPU chip.Τhis paper makes a comprehensive summary of the realization of the independent controllable computer hardware and software function,and gives a detailed elaboration of major circuits and the key technologies about the motherboard. Τhe results of performance testing and stability testing of the whole computer based on native firmware and OS are also introduced.It will provide a technology reference for development of high performance native computer in the future.

loongson 3A;independent controllable;native computer

在基于国产高性能龙芯3A CPU芯片进行主板研制并成功实现的技术基础上,通过全面总结自主可控主板的软硬件及整机的实现过程,对自我研制主板的各主要功能电路及关键技术进行了详细阐述,对基于国产固件、操作系统进行整机系统的实现以及针对整机进行的性能测试进行了介绍说明,为国产自主可控计算机的发展提供技术借鉴。

龙芯3A;自主可控;国产化计算机

A

ΤP393.08

10.3778/j.issn.1002-8331.1204-0627

JI Jing,QU Tao,JIN Da,et al.Design and implementation of independent controllable computer.Computer Engineering and Applications,2013,49(15):36-40.

纪静(1984—),女,工程师,主要从事计算机应用的研究与开发;屈涛(1967—),女,研究员级高级工程师,主要从事计算机应用和数字通信的研究与开发;金达(1982—),男,工程师,主要从事计算机应用的研究与开发;吴金哲(1983—),女,工程师,主要从事计算机应用的研究与开发;王巍(1974—),女,高级工程师,主要从事计算机和通信的研究。E-mail:j.j813@126.com

2012-05-03

2012-06-18

1002-8331(2013)15-0036-05