基于FPGA的远距离实时传输接口设计

2013-07-13吴志玲

王 栋,靳 鸿,吴志玲,刘 亮

(中北大学 教育部仪器科学与动态测试重点实验室,山西 太原 030051)

信息技术分为信息获取技术、信息传输技术、信息处理技术。雷达技术向高分频率、多级化、多频段等方向的发展,雷达信息获取量也随之增加,本文为满足对被测雷达信号的高容量、高速度、远距离、低功耗、高可靠性及高灵活性的数据存储及处理[1]。选用了LVDS接口,大容量的SDRAM和FPGA控制芯片。

1 系统总体设计方案

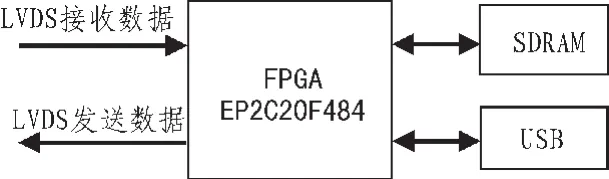

本存储测试系统是由 LVDS接口,FPGA,SDRAM,USB,上位机组成。采用LVDS接口进行雷达数据的发送与接收,用FPGA进行数据处理与存储,通过USB接口进行计算机与FPGA的连接。系统的总体原理图如图1所示。

图1 系统总体原理图Fig.1 Overall system diagram

系统的工作原理:系统的发送过程是用16位的并行LVDS和10位串行LVDS接口接收雷达获取的信号,采用FPGA进行数据处理与存储,最后通过USB接口数据上传到计算机实现数据分析与实验。系统的接收过程是计算机将控制命令及数据通过USB接口,将数据实时的存储到SDRAM中,然后根据SDRAM控制器的命令将数据送给串行或并行LVDS接口。

2 LVDS接口设计

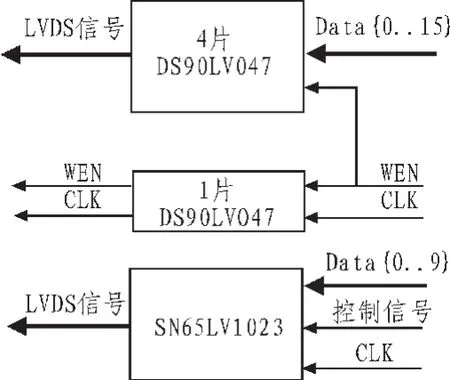

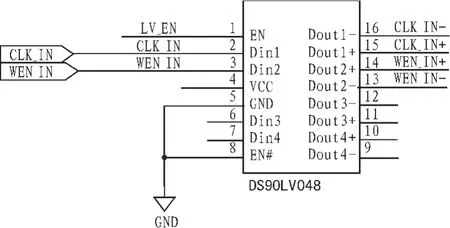

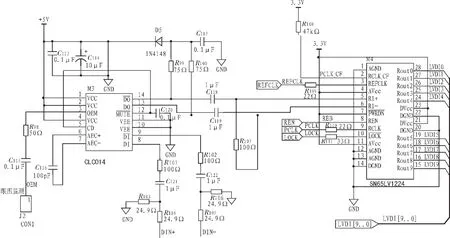

LVDS即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。具有数据率高、功耗低、端接匹配很容易、可靠性高、成本低等优点[2],可使用铜质PCB连线传输或平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中的应用越来越广泛。图2为LVDS接口设计部分。

图2 LVDS发送模块Fig.2 LVDS send module

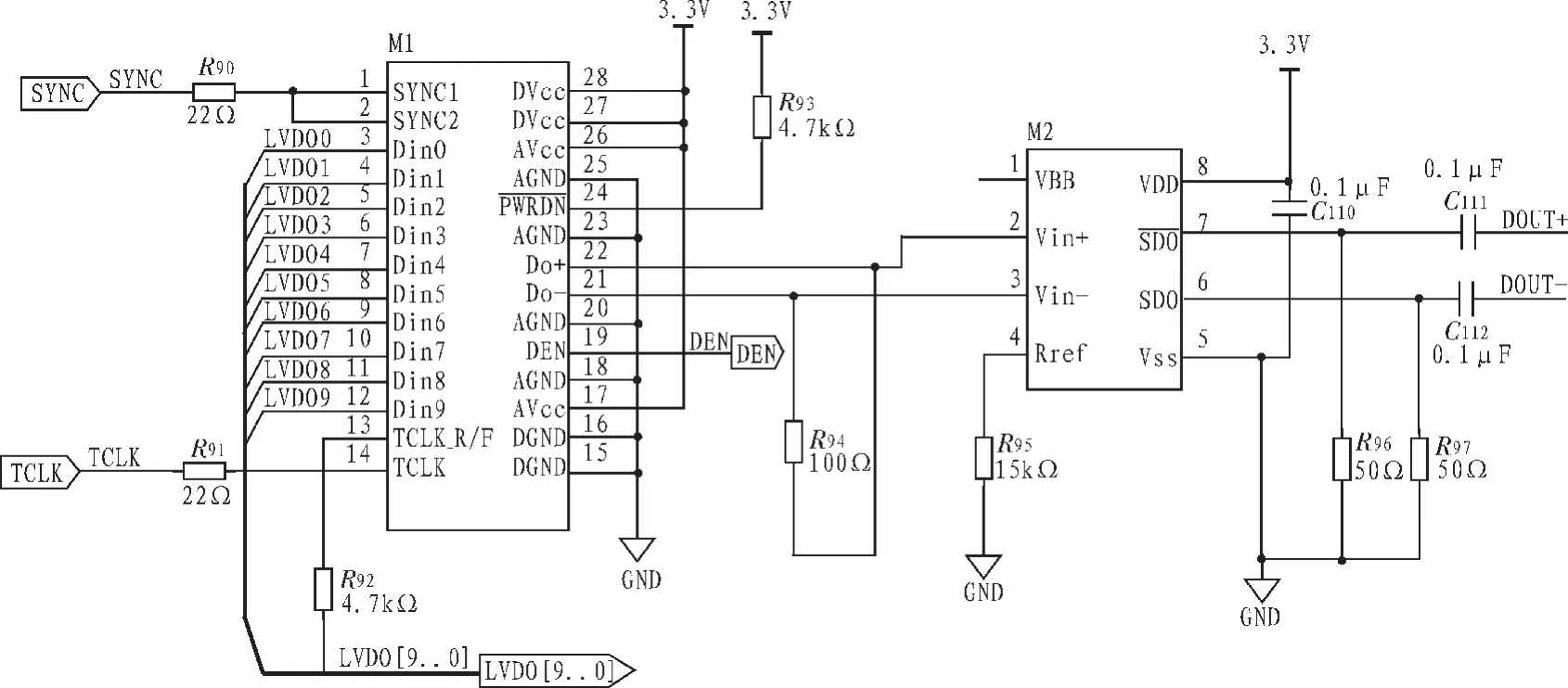

图3 LVDS串口发送的连接图Fig.3 Send the LVDS serial connection diagram

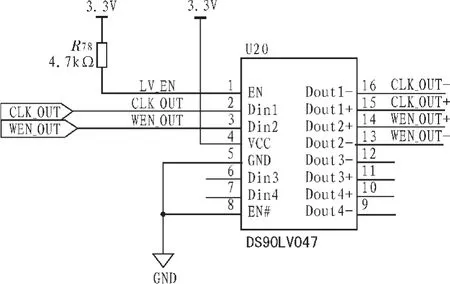

图4 LVDS并行发送的连接图Fig.4 Sends LVDS parallel connection diagram

图6 LVDS并口接收模块Fig.6 LVDS parallel receiver module

图6中串行接口:是选用SN65LV1023发送串行数据,SN65 LV1024接收串行数据。并行接口:选用5片DS90LV047来发送并行数据,5片DS90LV048来接收并行数据。其中,4片是传输16位并行数据,1片是传输控制信号与时钟信号。本系统传输模块发送中,是FPGA首先向串行接口65LV1023发送DEN及TCLK信号或并行接口DS90LV047发送WEN、CLK,接着LVDS接口芯片,把从LVDS接口接收到的TTL并行信号转换为LVDS标准的串行信号或并行信号。串行LVDS信号通过驱动器CLC001,通过RJ45接口发送出去。并行LVDS信号通过DB37发送出去。接收过程类同。

在本设计中,由于数据发送端与接收端距离较远,两个板卡的地线之间可能出现电位差,在两端产生直流电流,会影响差分对的工作甚至造成可靠性问题。因此,需要采用交流耦合来消除直流电位差,在差分输出端采用隔直电容进行交流耦合。阻抗匹配是通过一对阻值为传输线特征阻抗一半的电阻R6、R7对差分传输的源端进行匹配。接收端LVDS电路,这里主要考虑LVDS接口电路的阻抗匹配设计。因为单纯的LVDS差分传输应用距离较短,所以并行和串行接口都选用了100 Ω的电阻进行匹配。 在经过实验发现,发现LOCK信号有失锁的情况,故要加光电隔离进行隔离。在做PCB板布线时是要注意:至少要用4层布板,LVDS信号层、地层、电源层、TTL信号层;使TTL和LVDS放在由电源/地隔离的不同层上。使LVDS驱动器和接收器尽可能靠近连接器的LVDS端,使用分布式的多个电容旁路LVDS设备[4]。

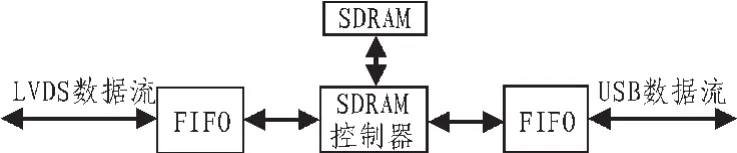

3 系统存储控制模块

系统的存储控制模块,在本系统中LVDS的传输速率高达600 MBPS,而 USB的读取速率理论上为 480 MBPS,由于写的速度过快,读取的速度慢,容易造成读数据的丢失[3],并且系统要求系统在短时间内能够传输并存储传输结果[5]。选用了容量更大,处理速度更快的SDRAM。中间加异步FIFO,用于时钟匹配。SDRAM是一种随机访问存储器,SDRAM的特点是大容量和高速。其单片容量可达256 MB或更高,工作速度高达 100~200 MHz[6],本系统选用芯片 MT48LC16M16A2。时钟频率选择133 MHz。LVDS串口信号中有8位有效数据,要经过FIFO缓冲,进行数据整合,时钟匹配,变成16位并行的信号,在存入SDRAM中,而LVDS并行信号,直接通过FIFO缓冲,达到时钟匹配,进入SDRAM中。如图8所示。

图7 LVDS串口接收模块Fig.7 LVDS serial port receiver module

图8 系统存储控制模块Fig.8 System storage control module

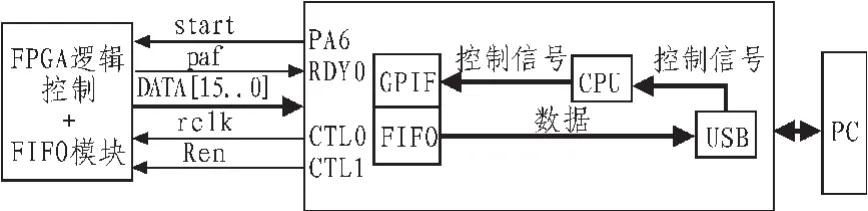

4 系统接口控制模块

传输系统与上位机通过USB接口进行通信,选用CYPRESS公司的CY7C68013单片机作为USB控制器。CY7C68013包含增强型8051内核和智能USB接口,开发简单,价格低廉,包含通用可编程接口(GPIF),包括4KB的大缓冲区,能真正体现USB2.0传输速度[7]。本系统采用GPIF模式与FPGA通信,通过判断FIFO状态进行读写数据,配合USB控制逻辑上传数据和下发命令。其中,GPIF提供了接口信号(包括16位数据总线、输出控制信号CTL、输入控制信号RDY),这些信号负责完成USB与FPGA的数据读/写控制和传输[8]。系统如图9所示。

图9 FPGA与68013逻辑控制关系Fig.9 FPGA and 68013 logic control relationship

5 实验结果

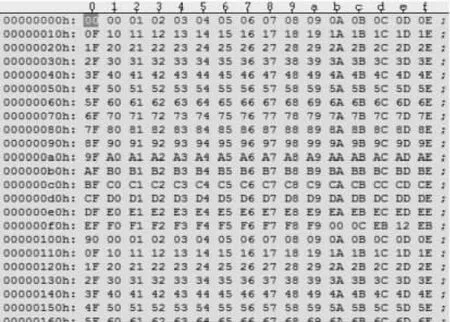

图9为雷达获取信号的获取,数据接收的开始两个字节为EB 90,然后是传输的数据,分析数据结果得知,,经过LVDS传输系统回读数据的格式与信号源发出的数据格式保持一致,并且未出现丢数、误码现象,实现了LVDS数据传输的基本功能。如图10所示。

图10 存储器存储数据Fig.10 Memory store data

6 结束语

文中采用LVDS与FPGA相结合,很好的完成了对雷达数据高速、高容量、远距离、低功耗、高可靠性等特点的要求,在需要远距离传输和大容量存储的环境中,具有广泛的应用。

[1]储成群.基于LVDS接口的高速数据记录器的设计[D].太原:中北大学,2011.

[2]王胜,王新宇.LVDS技术及其在高速系统中的应用[J].遥测系统,2005,26(4):41-46.

WANG Sheng,WANG Xin-yu.LVDS and it’ s application in high speed system[J].Joumal of Tele-metry,Tracking and Command,2005,26(4):41-46.

[3]金松波.基于PCI总线的数据采集与存储系统[D].南京:南京理工学,2009.

[4]贾小云,懂普松.基于LVDS接口的多通道高速串行数据采集系统[J].陕西科技大学学报,2008,26(5):103.

JIA Xiao-yun,DONG Pu-song.Multi_channel high speed serial data acquisition system based on LVDS interface[J].Journal of shaanxi university of science&technology,2008,26(5):103.

[5]朱宏光,司静.一种用于高速数据采集的SDRAM控制器[J].无线电工程,2010,40(4):62-64.

ZHU Hong-guang,SI Jing.A SDRAM controller for highspeed data acquisition[J].Radio Engineering,2010,40 (4):62-64.

[6]周昆正.基于FPGA的SDRAM设计[J].现代电子技术,2003(13):63.

ZHOU Kun-zheng.Design of SDRAM controller based on FPGA[J].Modern electronic technology,2003(13):63.

[7]钱峰.EZ-USB FX2单片机原理、编程及应用[M].北京:北京航空航天大学出版社,2006,13(156):66.

[8]龙玲,许海清.USB2.0微控制器CY7C68013的GPIF接口设计[J].单片机与嵌入式系统应用,2006(10):47-49.

LONG Ling,XU Hai-qin.USB2.0 micro controller CY7C68013 GPIF of interface design[J].SCM and embedded system application,2006(10):47-49.