基于m序列叠加DDS信号源的设计与实现

2013-06-26邹向阳董杨波

李 鹏,邹向阳,董杨波

(1.桂林电子科技大学电子工程与自动化学院,广西 桂林541004;2.空军空降兵学院,广西 桂林541003)

雷达干扰,作为一种常用的雷达对抗方式在电子战中倍受关注。采用噪声信号对敌方雷达进行干扰,可以有效地降低雷达发现目标和跟踪目标的能力,所以噪声信号源的设计,就显得尤为重要。目前产生噪声信号的方式通常可分为模拟式、数字式和混合式。而将噪声与DDS(直接数字式频率合成器)信号叠加,既方便使用,又能有效地干扰对方的信号。为了达到这个要求,本文提出采用m伪随机序列信号与DDS信号叠加来作为其噪声信号源,生成一种频谱丰富、带宽可调的干扰信号,这种干扰信号具有更好的干扰效果。

1 m序列叠加DDS信号源的设计方案

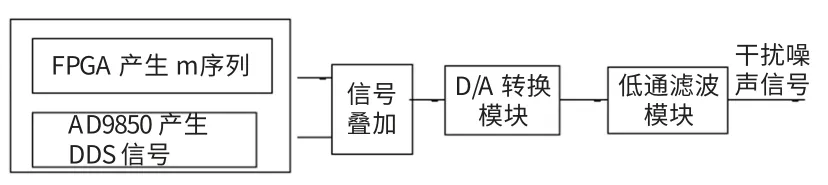

m序列叠加DDS信号源的具体设计方案如图1所示。利用FPGA芯片高速,稳定,低功耗的特点和具有反馈移位寄存器的逻辑功能,实现D触发器串接,生成m伪随机序列信号。同时利用AD9850芯片可产生高分辨率的频率的特点,通过串行方式输入频率/相位控制字,经过芯片内部的正弦查找表,把输入地址的相位信息映射成正弦波幅度信号,再经过AD9850内部的DA变化器输出十分稳定的DDS信号。最后通过ARM7作为主控芯片,将FPGA产生m序列的信号与AD9850产生的DDS信号叠加,把产生的信号通过D/A转换,低通滤波,最终得到理想的噪声信号。

图1 基于FPGA和DDS的设计原理图

1.1 伪随机序列的分析

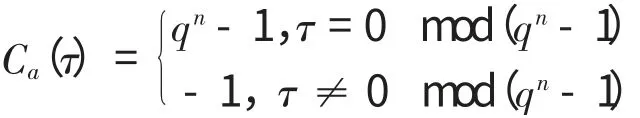

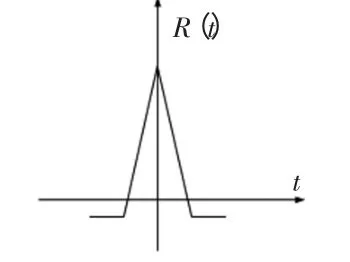

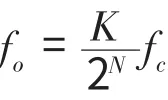

在加密或干扰等相关的工作中常用到伪随机序列,这是因为其同时具有一定随机特性和确定性。它通常由寄存器产生,具有近似于白噪声的相关函数。例如:序列x=0110100,0和1的数目相差1个。若x为周期是7的无限的序列,左移1位可得,x1=1 101 000,再把x1也看成周期为7的无限序列。可见x=0 110 100,x1=1 101 000在一个周期里,x和x1的对应位置元素相同的位置有3个,元素不同的位置有4个,它们的差为-1,这个数即是x的自相关函数在1处的值。同理,把x左移2位,3位,…,6位,可以求出x的自相关函数在2处,3处,…,6处的值也等于-1。当0 也就是说,一个周期为v的无限序列,如果在一个周期里,0和1的个数相差1,并且其自相关函数的旁瓣值有且只有一个为-1,则称其为伪随机序列或拟完美序列。x的自相关函数的旁瓣值的绝对值越大,就表明(或把的0和1互换得到的序列)与x越像。因此如果周期为v的序列x是一个伪随机序列,那么x不管左移几位(只要不是v的倍数),得到的序列都和x很不像,这样就很难分辨出x是什么样子。这说明了用伪随机序列作为密钥序列,是比较安全的。因此,可以利用这样的序列做加密或是干扰等相关的工作。 m序列是一种典型的伪随机序列,具有良好的自相关的特性和平移可加性,在实际中经常使用。例如:若a元n级非退化线性反馈移位寄存器生成序列最大的周期是an-1,则每一个非零状态在一个周期内只能出现一次。这种以an-1为周期的序列是最大长度线性反馈移位寄存器序列,就是m序列。n级m序列的线性复杂度是n。n级m序列a的自相关的特性[5]: m序列具有一种典型的平移可加性:包含它的平移等价类再加上零序列刚好组成一个线性空间。例如:设序列是周期为P的m序列,k是n级m序列移位寄存器在其中一个i时刻的内部状态,那么,集合对加法是封闭的,其中L是左移算子,也可以说对于任何的0燮i 由上述可知,m序列的自相关函数只有两种取值。有时把这类自相关函数只有两种取值的序列称为双值自相关序列。m序列拥有良好的自相关特性。其自相关函数如下图2所示。在图2中,m序列具有较理想的伪随机性,自相关函数尖锐,类似白噪声的特点,适合作为雷达干扰机噪声信号的核心模块。 图2 m序列的自相关函数 m伪随机序列信号的生成方法有很多,一般来说,k级线性移位寄存器能够生成多个m序列并且每一个m序列对应着一个确定的线性反馈函数:f(x)=其中cn-1-i∈GF(2)是反馈系数,ci∈GF(2)是每一位寄存器的状态。使用m序列f(a)=1+a2+a3+a4+a8所生成的数字信号,是一种常用的产生m序列伪随机信号方法,可以通过FPGA的线性移位寄存器发生器生成数字信号和相应的时钟信号,这样产生的信号误差很小,并且可以输出TTL电平,使用方便。同时,也可以采用对任意级数的m序列发生器进行Verilog语言进行编程的产生方法,来满足产生任意级数的m序列发生器的要求。原理是m序列发生器是在多级移位寄存器的基础上产生多个m序列,并且每一个m序列都相应存在确定的反馈的函数。结合FPGA芯片的特点和反馈移位寄存器的逻辑功能,实现D触发器串接,即能生成m伪随机序列信号。 直接数字合成(Direct Digital Synthesis,简称DDS),又称为直接数字频率合成(DDFS)。DDS的出现改变了以往的采用RC振荡电路、直接频率合成、锁相环等传统的频率合成方法。它以固定的精确时钟源为基准,利用数字处理模块产生频率和相位均可调的输出信号。DDS理论依据是时域抽样定理,即一个频带限制在(0,f/2)Hz范围内的时间信号f(t),如果以T=1/f秒的间隔对它进行等间隔抽样,则该信号f(t)可以由其采样值完全地恢复。DDS正是基于此原理,将一个阶梯化的信号(采样信号)通过理想低通滤波器得到原始的连续信号。DDS的基本结构包括:相位累加器、存储器ROM、数模转换器DAC等,其原理框图如图3所示。 图3 DDS信号生成的原理框图 DDS输出信号的频率与时钟频率fc以及频率控制字K,累加器位数N之间的关系如式下所示: 当K=1时,DDS输出最低频率(也即频率分辨率)为fc/2N。因此,只要N足够大,DDS可以得到很细的频率间隔,要改变DDS的输出频率,只要改变K即可。本雷达训练干扰机使用的是AD9850来产生DDS信号。 将FPGA产生的m伪随机序列信号与AD9850产生的DDS信号通过加法器进行叠加。其中,FPGA采用Cyclone IIEP2C8Q208芯片。其等效门数为42万门,内嵌乘法器时钟采用50MH有源晶振,通过EP2C8内部PLL3倍频到150 MHz作为系统全局时钟,因此,为了提高量化精度,必须提高D/A转换的位数。同时,为了提高带宽和转换速率,必须提高D/A转换的采样速率,所以D/A器件选用Analog Device公司的AD9752。该芯片是单电源供电的低功耗电流输出型的12位并行高速数模转换器,支持速率高达125MSPS,建立时间不大于35ns,转换精度为1/4 LSB,能够满足系统对D/A的要求。最后,将得到的数字序列分别通过高速D/A转换器、低通滤波器和运算放大器转换为所需要的某型号雷达噪声干扰信号。 经过上面的分析,具体把这种噪声信号源应用到某雷达训练干扰机,将这个信号经过微波固态振荡源的功率放大,通过天线辐射出最终的干扰信号,某雷达训练干扰机使用ARM7来控制微波固态振荡源的功率大小,提供良好的人机交互方式(包括矩阵键盘和液晶显示屏),方便使用。具体的实现方法如图4所示。 图4 雷达训练干扰机整体设计方法 采用上述信号的雷达干扰训练器在雷达附近工作时,雷达显示器上出现了明显的干扰噪声,如图5所示。测试结果表明:使用了m序列叠加DDS信号源的雷达干扰训练器干扰了雷达正常工作。波形显示正常,无明显失真;从输出指定幅度的波形上来看,波形稳定,幅度值误差在1%以内,达到了预期效果。 图5 某雷达训练干扰机在雷达车上的实际干扰效果图 [1]曾菊容.基于FPGA和DDS技术的任意波形发生器设计[J].现代电子技术,2010(24):98-100. [2]高 望.直接数字频率合成技术及其杂散分析[D].南京:南京理工大学,2002. [3]熊 燕.直接数字频率合成器的频谱分析及ROM压缩算法研究[D].广州:中山大学,2005. [4]杨玉梅.直接数字频率合成器(DDS)杂散谱计算机仿真[D].成都:电子科技大学,2000. [5]李 烨.长周期伪随机序列局部性能分析和快捕获及其应用[D].成都:电子科技大学,2002. [6]任建新,余乐永,张 鹏.基于FPGA的高精度信号发生器的实现与优化[J].测控技术,2011,30(1):13-16. [7]周红艳.一种基于DDS的函数发生器[J].机电工程,2011,28(1):83-86. [8]向道朴.宽带步进频率雷达信号源的设计与实现[D].长沙:国防科技大学,2006. [9]王元华.基于DDS技术的虚拟式任意波形发生器研究[D].济南:山东大学,2007. [10]王 琪,邹向阳,胡巍彪.雷达干扰训练器噪声干扰源的设计[J].自动化仪表,2010,633-634.1.2 m伪随机序列的实用性解析

1.3 m伪随机序列信号的生成方法

1.4 DDS信号的生成

1.5 m序列叠加DDS信号

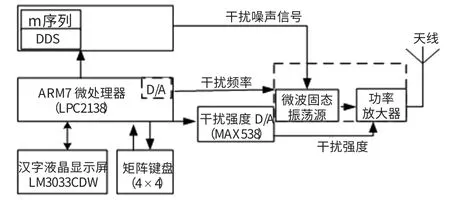

2 在雷达训练干扰机的应用

3 结束语