基于FPGA的DDC中CIC滤波器的设计

2013-06-23肖瑞川刘艳萍彭成功

肖瑞川,刘艳萍,彭成功

(河北工业大学 信息工程学院,天津 300401)

在软件无线电中,数字下变频器位于信号处理链的前端,靠近A/D,由于A/D之后的数据速率过高,无法满足实时处理的需要,所以需要数字下变频器接收高速的中频数字采样信号,将所需的频带下变频到基带。

数字下变频(DDC)中数字滤波器的主要作用是抽取、低通滤波,一般由FIR滤波器实现。但FIR滤波器需要大量的乘法器,且一般DDC中的采样速率很高,因此FIR滤波器需要工作在很高的频率,使用资源多、功耗大。由于级联积分梳状滤波器(CIC)结构只用到加法器和延迟器,没有乘法器,很适合用作为第一级滤波器,实现抽取、低通滤波;第二级则采用一般的FIR或者FIR实现的特殊滤波器(如半带滤波器),此时它们工作在较低的频率下,且滤波器的参数得到了优化,因此更容易以较低的阶数实现,节省资源,降低功耗[1]。

单级CIC滤波器的频率响应为:

平为:

它与主瓣电平的差值为

单极CIC滤波器的旁瓣电平是比较大的,只比主瓣低13.46 dB,只也就是意味着阻带衰减很差,一般难以满足实用要求,为了降低旁瓣电平,我们可以采用多级CIC滤波器级联的方法来解决,N级CIC滤波器旁瓣抑制为:

1 CIC滤波器的原理

CIC抽取滤波器包括两个基本组成部分:积分部分和梳状部分,单级CIC抽取滤波器结构如图1所示。

图1 单级CIC抽取滤波器结构Fig.1 Single stage CIC decimation filter structure

单级CIC抽取滤波器传递函数为:

可见5级级联CIC滤波器具有67 dB左右的阻带衰减,基本能满足实际要求。综合以上分析可知,CIC滤波器的性能由参数D,M,N共同决定,级数N可以控制阻带衰减和旁瓣抑制,减小通带混叠。但N值得增加受通带内容差的限制,所以N值不可以太大,一般不超过5级;延迟因子D的取值决定了抽取后幅频特性曲线的零点位置,加大D值可有效减小混叠,但同时也会增加通带内容差;M值决定了CIC滤波器的主瓣宽度和旁瓣宽度以及抽取后的数据速率。因此,必须根据工程对数据和时钟速率,通带宽度,通带和阻带的衰减等指标要求全面考虑这几个参数的选取。

2 CIC滤波器的设计

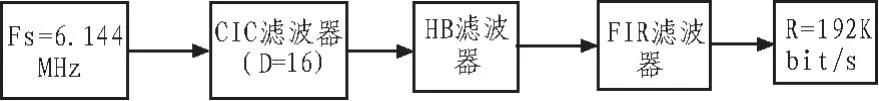

2.1 数字下变频器抽取滤波系统

整个抽取滤波系统的第一级用CIC抽取滤波器实现,完成16倍抽取;后面级联一个半带滤波器和一个基二抽取器,最后加上一个简单的FIR低通滤波器即可。在设计中由于CIC抽取滤波器通带衰减不符合要求,所以需要级联一个ISOP滤波器进行补偿。整个抽取滤波系统结构如图2。

图2 数字下变频抽取滤波系统结构Fig.2 Structure diagram of the DDC decimation filter system

2.2 CIC滤波器参数的设计

信号指标要求为带内波动小于0.6 dB,带外抑制大于60 dB;初步拟定CIC滤波器的通带纹波为0.5 dB,半带滤波器的通带纹波为0.1 dB,它们的阻带衰减均为60 dB。

CIC滤波器的参数[3-4]为:通带截至频率fc=B=60 kHz,抽取倍数D1=16,输入采样率fs=6.144 MHz,可得到带宽比例因子b=B/(fs/D1)=0.156 25,则单级CIC滤波器无混叠信号带宽内的阻带衰减A≈-201gb≈16.12 dB,不满足要求,所以必须进行级联,而当进行5级级联时,即当N=5时,A=80.6 dB,阻带衰减大于60 dB,满足阻带衰减的要求。但是单级CIC滤波器通带内容差为dB,采用多级级联,即N=5时,δ=1.7585dB,由此可见,带内纹波大于设计要求0.5,不满足设计要求,所以必须对其进行补偿,在此选用内插二阶多项式ISOP滤波器与之级联进行补偿。

2.3 ISOP补偿滤波器

ISOP滤波器的系统传递函数为P(x)=(1+cz-1+z-2)/|c+2|,其中I是正整数,c是实数。它是二阶多项式S(z)=(1+cz-1+z-2)/|c+2的插值后的变化形式。系统传输函数p(ejω)的频响为|p(ejω)|=|c+2cosIeω|/|c+2|。由S(z)频响的性质可知,P(z)得频响在ω∈[0,π/I]区间是单调递增,并且是2π/I以为周期的,其中I是插值率。可见,在的区间上,P(z)是能够补偿CIC抽取滤波器带内的单调衰减的。为了补偿级联CIC抽取滤波器带内的衰减,在区间ω∈[0,π/I]单调递增的宽度应该与输入2πf0保持一致。因此可以得到I=kM。

如级联CIC滤波器的各参数已确定,ISOP滤波器的参数则可用传统的滤波器设计方法来设计。对每一个满足1≤k≤的k值,按照下列方法求出c:1)给定最小的;2)将它带入|H(ejω)P(ejω)-1|<δ,1≤ω≤2πfc,其中H(ejω)是 给定的级联CIC抽取滤波器传输函数,P(ejω)是待求得ISOP滤波器传输函数;3)求出c值。由此,对应每个k按照以上步骤可以得到使最小的(k,c)对,也就得到了优化的ISOP滤波器。因为ISOP滤波只需要一次乘法和两次加法运算,可见运算量是很小的,且对减小通带衰减非常有效,因此,它是补偿滤波器设计很好的选择。

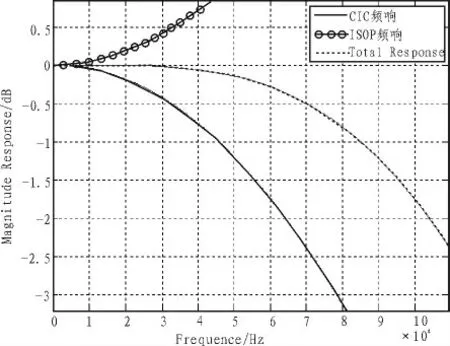

在文中的设计中信号的归一化通带宽度Fc=60/6144=0.009 8,而抽取因子M=16,则由可以得到k=1,2,3。再根据以上步骤进行优化设计,得到(k,c)=(1,-6.8)。通过分析CIC滤波器和ISOP补偿滤波器的频谱可以看出CIC滤波器的通带纹波大于系统要求的0.5 dB,大致为1.75 dB,补偿后的带内纹波得到了改善,约为0.27 dB,满足了设计的要求,但是补偿是以减小阻带衰减为代价的。

图3 CIC滤波器和ISOP滤波器幅频特性曲线Fig.3 CIC filter and ISOP filters amplitude-frequency characteristic curve

图4 CIC滤波器级联ISOP滤波器带内纹波图Fig.4 CIC filter and ISOP filters amplitude-frequency characteristic curve

图5 Modelsim仿真图Fig.5 Simulation diagram

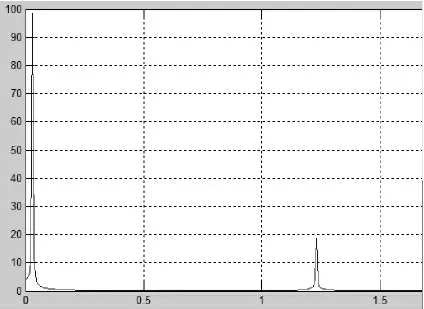

2.4 CIC滤波器的FPGA实现

文中采用VHDL语言描述,在quartusII11.0开发环境下进行仿真综合,在modelsim软件下进行仿真。结构中包括5个积分器,一个16倍的抽取器,最后是5个梳状滤波器。仿真结果如图所示。仿真过程通过Matlab产生30 kHz的正弦信号,叠加上1.2 MHz的正弦信号作为噪声。通过modelsim仿真结果,可以发现完成了对信号16倍的抽取。利用Matlab对输入输出信号频谱信号进行分析,可以发现滤波器很好的滤除了高频分量。输入输出信号频谱如下图6,图7所示,图6是输入信号的频谱,图7是输出信号频谱。

图6 输入信号频谱图Fig.6 Input signal frequency spectrum diagram

图7 输出信号频谱图Fig.7 Output signal spectrum diagram

3 结 论

文中以多速率数字信号处理理论为基础,分析了CIC抽取滤波器的原理和设计方法,并介绍了通过ISOP滤波器对CIC滤波器进行通带补偿。通过对指标参数的分析,以Matlab为工具设计了符合系统要求的CIC滤波器,并通过仿真证明了设计方案是可行的。最后通过FPGA[7-8]对该设计方案进行了仿真综合并利用Matlab进行了频谱分析,可以发现该设计很好的完成了信号的抽取和滤波。

[1]杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010.

[2]李翔,万栋义.数字下变频中抽取技术研究[J].电子科技大学学报,2006,35(4):471-473.LI Xiang,WAN Dong-yi.Digital down-conversion extraction technology research[J].Journal of university of electronic science and technology,2006,35(4):471-473.

[3]刘彬彬,林伟.基于Matlab和FPGA的CIC滤波器的设计[J].电子器件,2010,33(2):231-234.LIU Bin-bin,LIN Wei.Design and implement of CIC filter with Matlab and FPGA[J].Chinese Journal of Electr on Devices,2010,33(2):231-234.

[4]姜宇柏,游思晴.软件无线电原理与工程应用[M].北京:机械工业出版社,2007.

[5]UweMeyer-Baese.数字信号处理的FPGA实现[M].刘凌,译.北京:清华大学出版社,2006.

[6]徐尚中,何东健,万海军.基于FPGA的DDC中抽取滤波系统的设计[J].微计算机信息,2008,24(9-2):132-134.XU Shang-zhong,HE Dong-jian,WAN Hai-jun.Based on the FPGA DDC extraction of filtering system design[J].Micro computer information,2008,24(9-2),132-134.

[7]王维松,王金生,章伟,等.十字路口智能交通灯控制系统的FPGA实现[J].电子科技,2012(9):37-39.WANG Wei-song,WANG Jin-sheng,ZHANG Wei,et al.FPGA implementation of the intelligent traffic light control system for crossroads[J].Electronic Science and Technology,2012(9):37-39.

[8]何光明,黄云.多相滤波的数字相干检波原理及FPGA实现[J].电子科技,2010(8):58-61.HE Guang-ming,HUANG Yun.Principles of polyphase filtering for digital quadrature detection and its realization on FPGA[J].Electronic Science and Technology,2010(8):58-61.