基于IEEE1588频率漂移补偿算法研究与实现

2013-06-20陈金凤华宇孙中尉

陈金凤, 华宇,孙中尉

基于IEEE1588频率漂移补偿算法研究与实现

陈金凤1,2,3, 华宇1,2,孙中尉1,2

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院精密导航定位与定时技术重点实验室,西安 710600;3. 中国科学院大学,北京 100039)

在IEEE1588精密时间协议的应用中,为了进一步提高同步精度,应该引入对从时钟频率的漂移补偿。在介绍了IEEE1588时间同步过程及版本2中新增内容的基础上,阐述了一种频率漂移补偿算法并建立基于IEEE1588的时钟同步系统验证该算法。实验结果表明该算法在各种网络环境下都能有效地提高时间同步精度,对于电力、测控等有高精度时间同步需求的领域具有一定意义。

IEEE1588;频率漂移补偿;硬件时间戳

0 引言

随着网络技术的迅猛发展,各种分布式的网络和局域网都得到了广泛应用,高精度的时间同步技术成为当前许多系统的一项关键性技术。目前应用最广泛的网络时间同步方法有NTP(network time protocol,网络时间协议)和SNTP(简单网络时间协议),但是NTP的时间精度只能达到几十毫秒,而SNTP同步精度也只有1 ms,不能满足高精度时间同步应用要求。2002年出现的IEEE1588协议是IEEE制定的网络测量和控制系统精密时间同步协议标准,简称PTP(precision time protocol),它作为新的时间同步标准提高了同步精度,其时间同步精度在各种同步协议中是最高的,能达到亚微秒级同步精度[1]。目前该协议已经颁布了第2版本,即IEEE1588v2。为了提高长距离传输的时间同步精度,版本2中增加了透明时钟、端延时机制等内容。

在PTP系统中,规定了主、从两种时钟。主时钟是同步时间发布者,从时钟是同步时间的接收者。大多数的文献[2-3]实现PTP时钟同步采用瞬时调节方式对时钟偏差进行调整,没有考虑对从时钟进行时钟晶振的频率漂移补偿问题。由于从时钟的频率与标准频率存在偏差,造成两次同步时间间隔内从时钟频率发生漂移。为了进一步提高同步精度,应该引入从时钟晶振的频率漂移补偿。

本文在介绍了IEEE1588标准的时间同步过程及版本2中新增内容的基础上,提出频率漂移补偿算法,并建立基于IEEE1588时钟同步系统对频率漂移补偿算法进行验证。

1 IEEE1588时间同步技术

1.1 时间同步原理

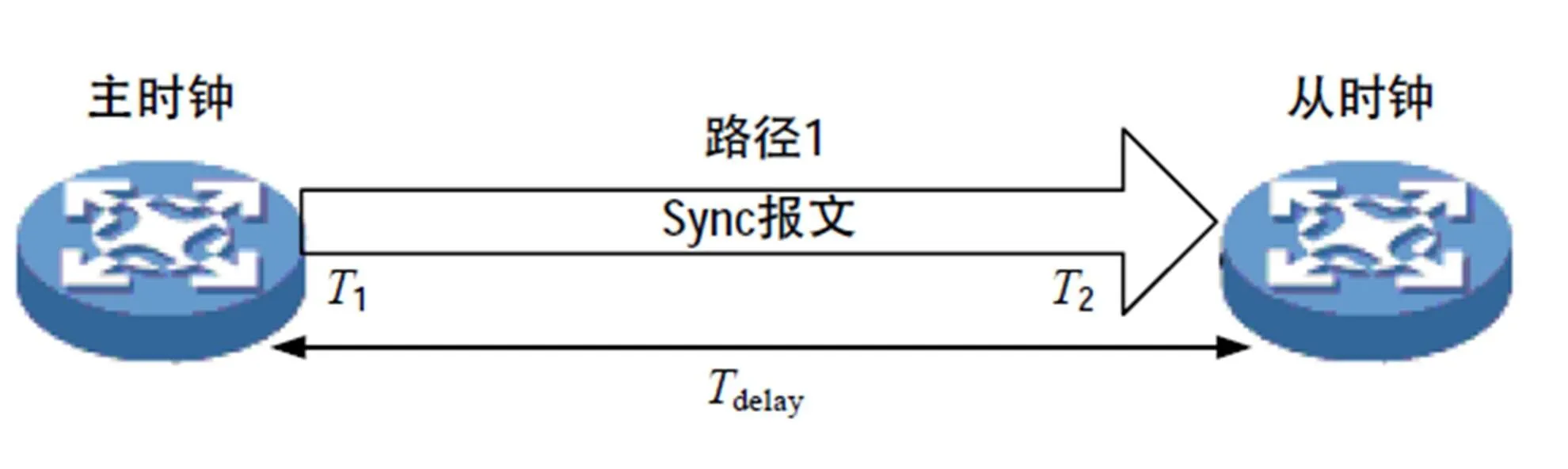

在一个PTP系统中采用主从层次式结构来同步时钟,主时钟是同步时间的发布者,从时钟是同步时间的接收者,且与主时钟实现同步。图1是主、从时钟通过直连模式实现时钟同步的基本原理图。

图1 PTP时间同步原理

1.2 延时测量机制

在IEEE1588v2中新增了端延时机制测量主从时钟间的传输时延[4]。测量过程如图2(a)(延时请求应答机制)和图2(b)(端延时机制)所示,延时请求应答机制与端延时机制不能同时被用于同一通信链路的传输时延测量。延时请求应答机制中,只在从时钟处计算路径延时,主钟处不计算延时。然而端延时机制中,主、从时钟处都计算路径延时。端延时机制具有较强的网络重构能力,但双向的延时计算增加了网络的负载。

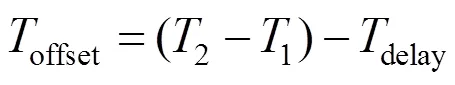

下面以延时请求应答机制为例说明主、从间传输时延测量的实现过程(参见图2(a))。根据是否需要发送Follow_Up报文,延时请求应答机制又分为单步模式和双步模式两种:在单步模式下,Sync报文的发送时间戳1由Sync报文自己携带,不发送Follow_Up报文;在双步模式下,Sync报文的发送时间戳1由Follow_Up报文携带。这里以双步模式为例进行说明。

主时钟向从时钟发送Sync报文,并记录发送时间1,从时钟收到该报文后,记录接收时间2,主时钟发送Sync报文之后,紧接着发送一个携带有1的Follow_Up报文,从时钟向主时钟发Delay_Req报文,并记录发送时间3。主时钟收到该报文后,记录接收时间4。主时钟收到Delay_Req报文之后,向从时钟发送一个携带有4的Delay_Resp报文。此时,通过从时钟记录的1~4这4个时间戳,假设主从系统链路之间的传输时延相等,由此可计算出主、从时钟间的平均路径时延为

在图2中,时间戳1,4由主时钟产生,2和3由从时钟产生。根据式(2),delay由1,4的差与2,3的差计算得到。因此,除传输链路的对称性外,主、从时钟频率同步性对同步精度有很大的影响。

1.3 透明时钟

在图1中,如果路径1上的事件报文经过一个交换机或路由器传输,事件报文进出交换机或路由器的时间戳差,即报文在交换机或路由器中的驻留时间。该驻留时间随网络流量和报文长度而变化。这导致了链路不对称,影响了传输时延的测量。为了解决这个问题,IEEE1588v2标准引进了一种新的时钟类型——透明时钟(TC)。TC能够计算事件报文在网络交换设备中的驻留时间并把该时间信息提供给事件报文的接收时钟。根据使用延时请求测量机制不同,将透明时钟分为端到端透明时钟(end to end transparent clock,E2ETC)和点对点透明时钟(peer to peer transparent clock,P2PTC),E2ETC用于延时请求应答机制中,P2PTC用于端延时机制中。在IEEE1588v1中只定义了普通时钟(ordinary clock,OC)和边界时钟(boundary clock,BC)。

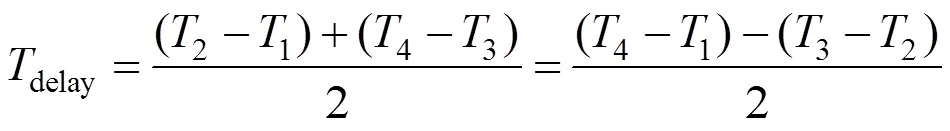

如图3所示,RT表示通过TC测量的驻留时间,PD表示路径上的传输时延。因此主、从时钟间的时间偏差可以表示为

2 频率漂移补偿算法

主时钟作为同步时间的发播者,它的晶振的稳定性比从时钟的晶振要好。主时钟一般采用高稳晶体振荡器,从时钟一般是普通晶体振荡器。因此,从时钟的晶体的频率和标准频率相比存在漂移,造成两次Sync同步信息时间间隔内从时钟频率相对主时钟频率发生漂移。这是影响PTP时间同步精度提高的一个重要因素,为此引入对从时钟频率的漂移补偿。

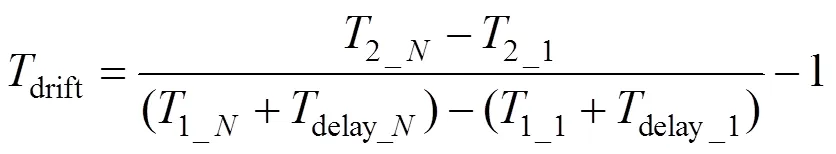

如果时钟A与时钟B的频率一致,则这两个时钟对于同一段时间的测量值相等,如果测量值不等,则测量值的比率为这两个时钟频率比的倒数,从而可以计算出从时钟相对主时钟的漂移值,如下式所示:

式(4)中,表示同步周期的个数,1_1表示第1个同步周期时发送时间戳,1_N表示第个同步周期时发送时间戳,2_1表示第1个同步周期时Sync报文的接收时间戳,2_N表示第个同步周期时Sync报文的接收时间戳,delay_N表示第个同步周期时主从时钟链路传输时延。从时钟分别根据offset调整时间,根据drift调整频率,实现主从时钟间的高精度时间同步。

3 PTP时间同步系统设计

3.1 系统设计

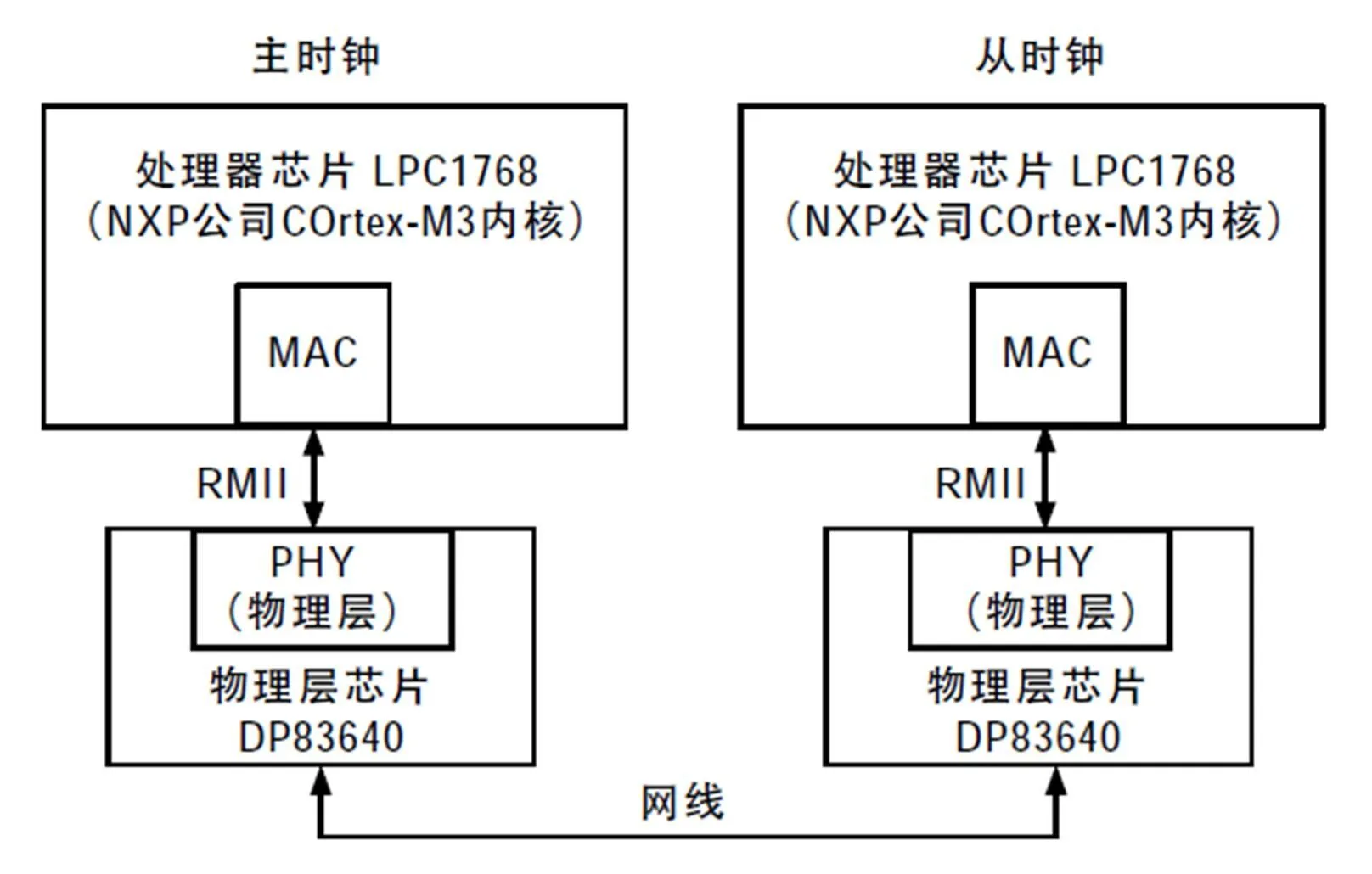

PTP时间同步系统整体设计框图如图4所示,由主时钟与从时钟两部分组成。主、从时钟的控制芯片相同,选用NXP Semiconductors(恩智浦半导体)公司生产的基于Cortex-M3内核的处理器芯片LPC1768,该芯片集成了10 Mbps或100 Mbps的以太网MAC(media access control)层功能,并具有DMA(direct memory access,直接内存存取)硬件加速器提高以太网传输速率。

图4 PTP时间同步系统设计框图

PTP协议实现时间同步的关键技术之一是收发报文时间戳的准确标记。时间戳标记的位置直接影响时间戳的精度。传统的时间同步协议(例如NTP协议)是软件标记时间戳,存在协议栈等延迟。本文以美国国家半导体公司推出的DP83640 物理层(physical layer,PHY)芯片为硬件辅助,完成对PTP报文的收发时间戳标记。DP83640支持IEEE1588标准,其内置高精度 IEEE1588 时钟,并集成了能够对收发数据包加盖时间戳的硬件,可以在最靠近网线的位置记录时间戳,避免了执行软件协议过程中的延时[5]。

上述两芯片之间采用简化媒体独立接口RMII主模式进行连接,减少了连接的管脚数目,易于布线及扩展。本系统选择PTP报文通过UDP(用户数据报)/IP协议传输。PTP事件报文的UDP目的端口号是319,普通报文的UDP目的端口号是320[1]。主、从时钟通过网线连接进行通信,完成PTP协议报文的交互。

3.2 时间校正

前面提到从时钟的时间校正根据时间偏差offset进行调整,频率漂移补偿根据drift进行调整。时间偏差可由式(1)计算得到。根据分析,主从传输路径时延delay只受主从间晶振振荡频率不同的影响,与时间偏差无关。如果在2与3(2,3如图2(a)所示)间调整时间,将无法保证时钟频率变化的连续性。delay将不能被正确计算,从时钟计算的offset的误差将增加。为了解决这个问题,从时钟对本地时间偏差的调整放在传输路径时延delay计算之后进行。

从时钟的时间偏差校正及频漂补偿的调整,都能够通过上面提到的DP83640芯片完成。该芯片提供了4种时间更新机制,包括直接时间调整,时间加减调整,频率调整和临时频率调整。本文充分利用这4种更新机制,完成从时钟的时间及频率调整,实现主从时钟的高精度时间同步。

4 PTP系统测试与结果分析

4.1 测试环境与条件

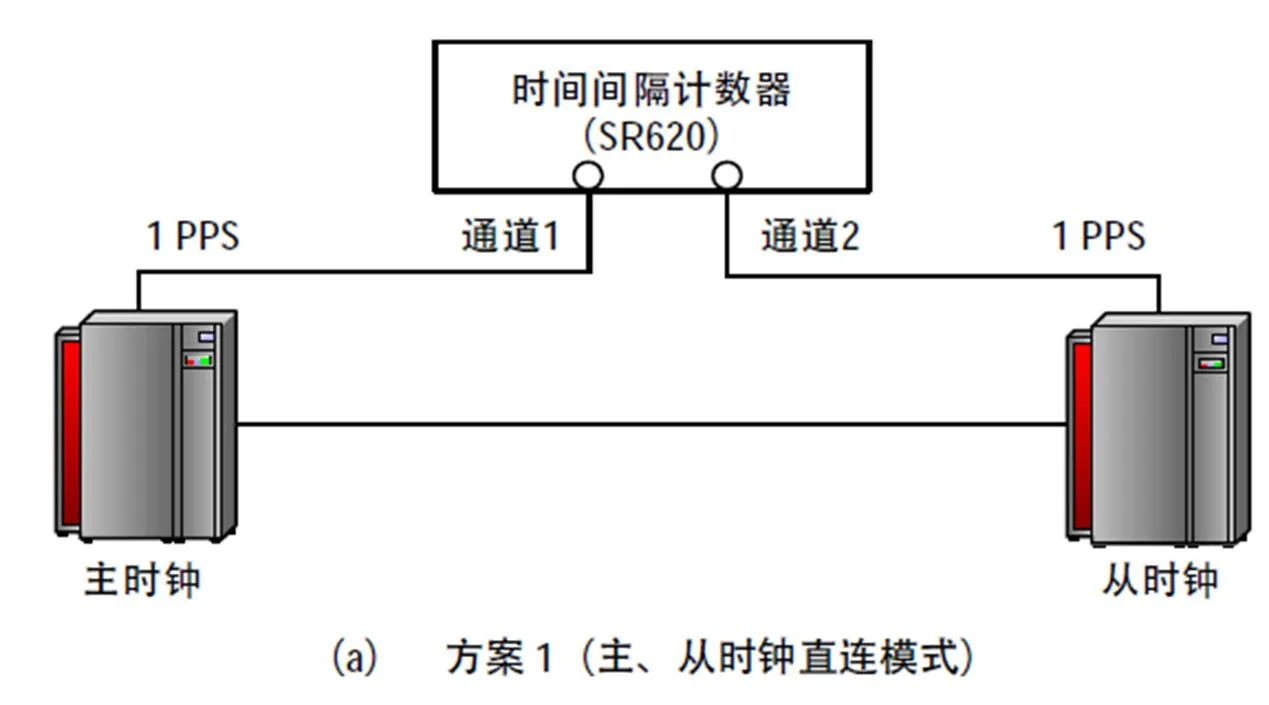

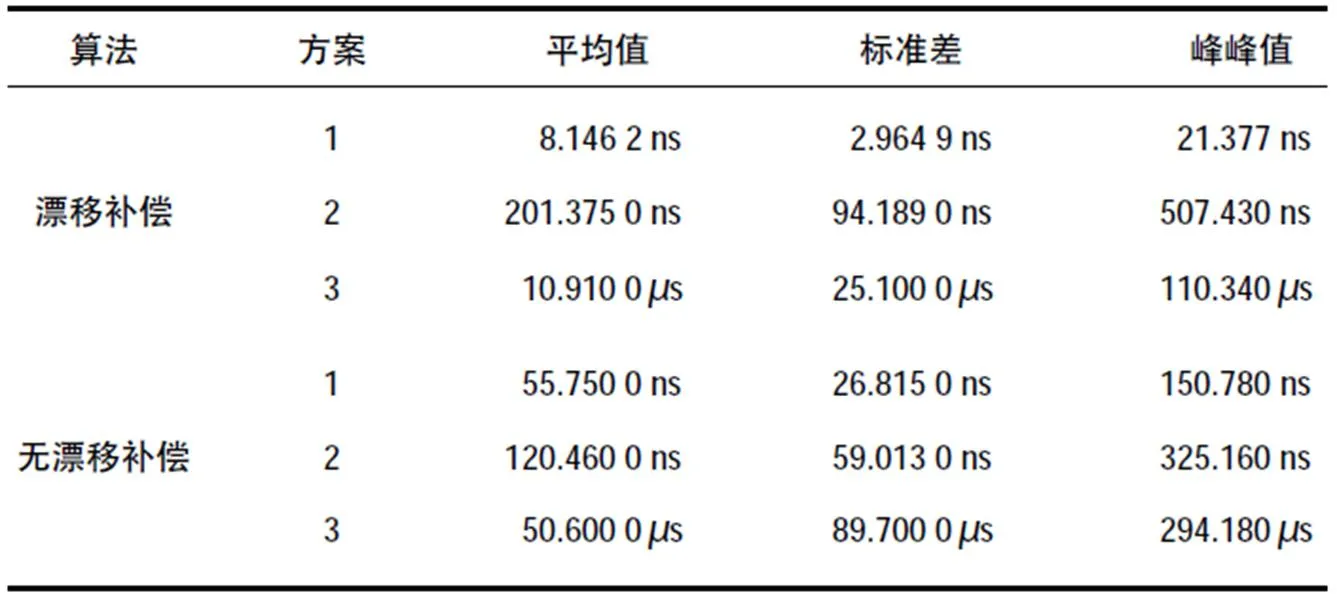

为了验证频率漂移补偿算法,建立如图5所示的PTP主、从时钟的实验测试平台。其中方案1为主从时钟直连模式,方案2为主从时钟在同一局域网内通过交换机互联,方案3为主从时钟在不同的网域内通过路由器互联。分别测试3种情况下,对从时钟进行频率漂移补偿算法及无漂移补偿算法时,从时钟的时钟同步精度。主、从时钟的频率源分别为NTSC钟房输出标准10 MHz信号和10 MHz OCXO恒温晶振经可移相分频钟产生25 MHz信号,频率稳定度分别为10-9和10-6。主时钟发送同步报文的周期设为1s/次。同步精度测试采用比较1 PPS秒脉冲信号方式。通过控制DP83640芯片能使主、从时钟分别输出1 PPS秒脉冲信号。利用时间间隔计数器SR620进行测量,通道1,2分别接主、从时钟秒脉冲信号。

4.2 实验结果与分析

用SR620时间间隔计数器进行测量,将主、从时钟分别输出的1 PPS秒脉冲信号,分别接入SR620时间间隔计数器的通道2中。将主时钟1 PPS信号的上升沿作为开门信号,从时钟1 PPS信号的上升沿作为关门信号,测试两个秒脉冲信号上升沿之间的差值,并通过串口线将SR620自带的数据采集软件得到的数据送到电脑中保存起来,最后经MATLAB软件进行处理,得到精确的同步精度值。测试实验结果如表1所示。

表1 测试结果比对

测试结果表明对从时钟进行频率漂移补偿的同步精度优于无漂移补偿的同步精度,该算法有效地提高了时间同步精度,对于电力、测控等有高精度时间同步需求的领域具有重要的意义,有重要的工程实践价值。

5 结语

本文介绍了IEEE1588标准的时间同步过程及IEEE1588版本2中新增内容,提出频率漂移补偿算法,并建立基于硬件标记时间戳的IEEE1588时钟同步系统对频率漂移补偿算法进行验证。实验测试结果表明该算法能有效地提高时间同步精度,能满足电力、测控等领域对于时间同步高精度的需求,对于工程实践具有一定的指导意义。

[1] EINDON J C. The application of IEEE1588 to test and measurement systems[R]. AGILENT, 2005.

[2] 王康, 胡永辉, 何在民. 基于DP83640硬件辅助的IEEE1588研究与实现[J]. 时间频率学报, 2011, 34(1): 1-8.

[3] 常永亮, 黄晓苹. 基于TMS320DM642的硬件实现IEEE1588时钟同步[J]. 电子设计工程, 2010, 19(19): 95-98.

[4] IEEE Std l588-2008 IEEE standard for a precision clock synchronization protocol for network measurement and control system[S]. 2008.

[5] National Semiconductor Corporation. DP83640 Precision PHYTER-IEEE 1588 Precision Time Protocol Transceiver[K]. USA: 2008.

Implementation and study of frequency drift compensation based on IEEE1588

CHEN Jin-feng1,2,3, HUA Yu1,2, SUN Zhong-wei1,2

(1. National Time Service Centre, Chinese Academy of Sciences, Xi′an 710600, China; 2. Key Laboratory of Precision Navigation and Timing Technology, National Time Service Center, Chinese Academy of Science, Xi′an 710600, China; 3. University of Chinese Academy of Science, Beijing 100039, China)

For further improving synchronization precision, a compensation for the frequency drift of the slave clock should be introduced in the application of IEEE1588 precision time protocol. In this paper, following an introduction of the time synchronization process of IEEE1588 and the added content of the IEEE1588(Second Edition), a method of frequency drift compensation is demonstrated and a time synchronization system is established based on IEEE1588 for verifying the compensation method. The experiments indicate that the method is helpful to improve the synchronization precision in various internet environments and can satisfy the high precision time synchronization demand of some fields such as electric power and measurement /control.

IEEE1588; frequency drift compensation; hardware-timestamp

P127.1+3;TM935.11

A

1674-0637(2013)03-0141-07

2012-08-23

中国科学院科研装备研制资助项目(Y307YR1301);西部之光联合学者资助项目(Y305YZ1301)

陈金凤,女,硕士,主要从事网络时间同步技术研究。