JTAG并口下载设计

2013-06-13张立强刘宝娟

张立强,宋 玲,刘宝娟

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

利用并口下载电缆实现JTAG下载,把并口的有效端口和JTAG端口连接起来,实现了数据写入、数据读出、控制器的信号输入、时钟的传输。在状态机的正确状态下进行指令匹配和数据传输。并在保证数据下载正确的前提下,达到下载速度的最优化。

2 JTAG下载设计与实现

2.1 并口和JTAG管脚关系

计算机的标准并行端口是25针的母接头端口。这25只管脚并不是都被用到。这些管脚分别用于数据的传输、检查打印机的状态及控制打印机。数据端口保存了写入数据和输出端口的一个字节信息。每位数据都是并行传送的,它通常是以字节(8位)为单位进行数据传输。并口的Pin2(TCK)、Pin3(TDI)、Pin8(TMS)分别对应数据寄存器的第0位、第1位、第6位。并口的Pin11(TDO)对应状态寄存器的第7位。Pin18到Pin25是引脚GND。

2.2 测试访问端口TAP控制器

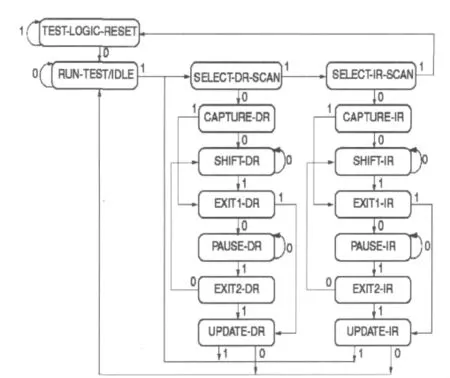

TAP控制器是一个有限状态机,一共有16个状态。测试访问状态机的目的是选择指令寄存器和数据寄存器,使其连接到TDI和TDO之间。

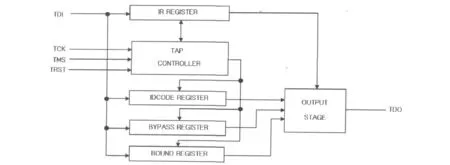

逻辑测试单元有一个指令寄存器和三个数据寄存器,三个数据寄存器为:旁路寄存器(BYPASS),识别码寄存器(IDCODE),边界扫描寄存器(BOUND)。指令决定使用哪个寄存器。指令寄存器为4位,指令由TDI引脚串行输入。如图1所示。

1位旁路寄存器(BYPASS)为TDI-TDO提供了一个最短的串行通路。在板级测试期间,可以通过这条通路绕开不需测试的设备。这可以提高测试速度。32位识别寄存器(IDCODE)提供了设备的制造商、版本号等信息。边界扫描寄存器(BOUND)保持引脚的状态或引脚需要的数据。边界扫描寄存器为一个串行的移位寄存器,每个单元分配给芯片的相应引脚。

图1 测试单元的结构

在这些指令中时钟的上升沿对TDI和TMS进行采样。所有的输出TDO都是在下降沿产生的。

2.3 JTAG下载流程

JTAG并口编程的实质就是首先将EXTEST指令串行移入可编程芯片上JTAG器件的指令寄存器,然后控制JTAG器件的TCK和TMS引脚使其进入SHIFT-DR状态,再将数据串行移入到JTAG器件的边界扫描寄存器,最后控制JTAG器件的TCK和TMS引脚使其进入UPDATE-DR状态,将位流写入FPGA。指令装载完成后,只要不更改指令,就不需要再进行指令移位了,此时只需要进行数据移位,所以数据移位是编程的主要操作。状态转换如图2所示。

图2 TAP控制器的16种状态切换图

首先对状态机复位,使JTAG单元从任何的未知状态回到TEST-LOGIC-RESET状态,让TMS至少保持连续6个周期的高电平后,回到TESTLOGIC-RESET状态。程序代码片段如下:

for(n=0;n<6;n++)

send_bit(0,1);//连续6个周期的高电平

TMS加一个周期的低电平,转到RUN-TEST/IDLE状态。TMS加两个周期的高电平转到 SELECT-IR状态。加两个周期的低电平后转到SHIFT-IR状态。程序代码片段如下:

send_bit(0,1);

send_bit(0,1);

send_bit(0,0);

send_bit(0,0);//转到SHIFT-IR状态

开始加载CFG_IN指令,指令码是0101,加载一个周期的高电平转到EXIT1-IR。程序代码片段如下:

send_bit(1,0);

send_bit(0,0);

send_bit(1,0);

send_bit(0,0);

send_bit(0,1);//加载CFG_IN指令

TMS加载两个周期的高电平转到SELECT-DR状态,再加载两个周期的低电平后转到SHIFTDR。程序代码片段如下:

send_bit(0,1);

send_bit(0,1);

send_bit(0,0);

send_bit(0,0);//转到SHIFT-DR状态

开始写配置寄存器选项 COR,写入指令后SHUTDOWN置1。写START指令到CMD指令寄存器。写清CRC指令寄存器。然后加载三个周期的高电平转到SELECT-IR,再加载两个周期的低电平转到SHIFT-IR状态。程序代码片段如下:

send_bit(0,1);

send_bit(0,1);

send_bit(0,1);

send_bit(0,0);

send_bit(0,0);//转到 SHIFT-IR 状态

加载 JSTART指令到指令寄存器,指令码是0011,加载一个周期的高电平转到EXIT1-IR状态。程序代码片段如下:

send_bit(0,0);

send_bit(0,0);

send_bit(1,0);

send_bit(1,0);

send_bit(0,1);//加载JSTART指令

加载两个周期的高电平,再加载两个周期的低电平转到SHIFT-DR状态。程序代码片段如下:send_bit(0,1);

send_bit(0,1);

send_bit(0,0);

send_bit(0,0);//转到SHIFT-DR状态

加载17个时钟周期关闭时序。程序代码片段如下:

for(n=0;n<17;n++)

send_bit(0,n==16);

加载三个周期的高电平和两个周期的底电平转到SHIFT-IR状态,加载CFG_IN指令。在SHIFTDR状态写AGHIGH指令到CMD寄存器中,产生GHIGH_B信号。写COR使得SHUTDOWN状态是0。写完指令后,加载三个周期的高电平和两个周期的低电平,状态转到 SHIFT-IR状态。加载JSTART指令后转到SHIFT-DR状态。加载17个时钟周期关闭时序转到SHIFT-IR状态,加载CFG_IN指令。在SHIFT-DR状态写AGHIGH指令到CMD寄存器中,产生GHIGH_B信号。写COR使得SHUTDOWN状态是1。写完指令后,加载三个周期的高电平和两个周期的低电平,转到SHIFT-IR状态。加载JSTART指令。转到SHIFT-DR状态,加载17个时钟周期关闭时序。转到SHIFT-IR状态,加载CFG_IN指令。转到SHIFT-DR状态,加载二进制位流文件,进行编程下载工作。位流全部移进后,转到SHIFT-IR状态,加载JSTART指令。加载两个周期的高电平和两个周期的低电平后转到SHIFT-DR状态。加载17个周期的低电平后,再加载两个周期的高电平和一个周期的低电平,状态机转到RUN-TEST/IDLE状态。程序代码片段如下:

send_bit(0,1);

send_bit(0,1);

send_bit(0,0);

JTAG编程下载完成。

2.4 测试与验证

JTAG下载程序在多款可编程芯片上进行了测试,位流能成功进行下载,电路的功能经验证完全正确。

3 结束语

JTAG并口编程很好的实现了位流文件到FPGA的下载,并对下载成功与否做出了明确的判断。通过指令回读出状态寄存器的状态,用于对比下载前后FPGA的状态变化。

[1][美]Dhananjay.V.Gadre.并行端口编程[M].北京:中国电力出版社,2000.

[2]何希顺,张跃,何荣森.嵌入系统中的JTAG接口编程技术[J].电子技术应用,2001,27(12):9-12.