基于CPCI总线的图像数据采集和回放系统设计

2013-05-14詹来龙李长森刘刚军

詹来龙 李 可 张 萌 李长森 刘刚军

北京航天自动控制研究所,北京 100854

目前,红外和可见光等技术被广泛应用,红外或可见光图像的好坏直接影响系统对目标的探测、捕获、跟踪能力,因此在各种试验条件下,红外或可见光的图像数据记录和回放尤为关键。红外或可见光图像具有速率快、数据量大的特点,考虑到视频采集的实时性、准确性和试验环境恶劣性要求,采用CPCI总线和SSD(Solid State Drive)技术,开发了基于CPCI总线的图像数据采集和回放系统。

1 系统概述

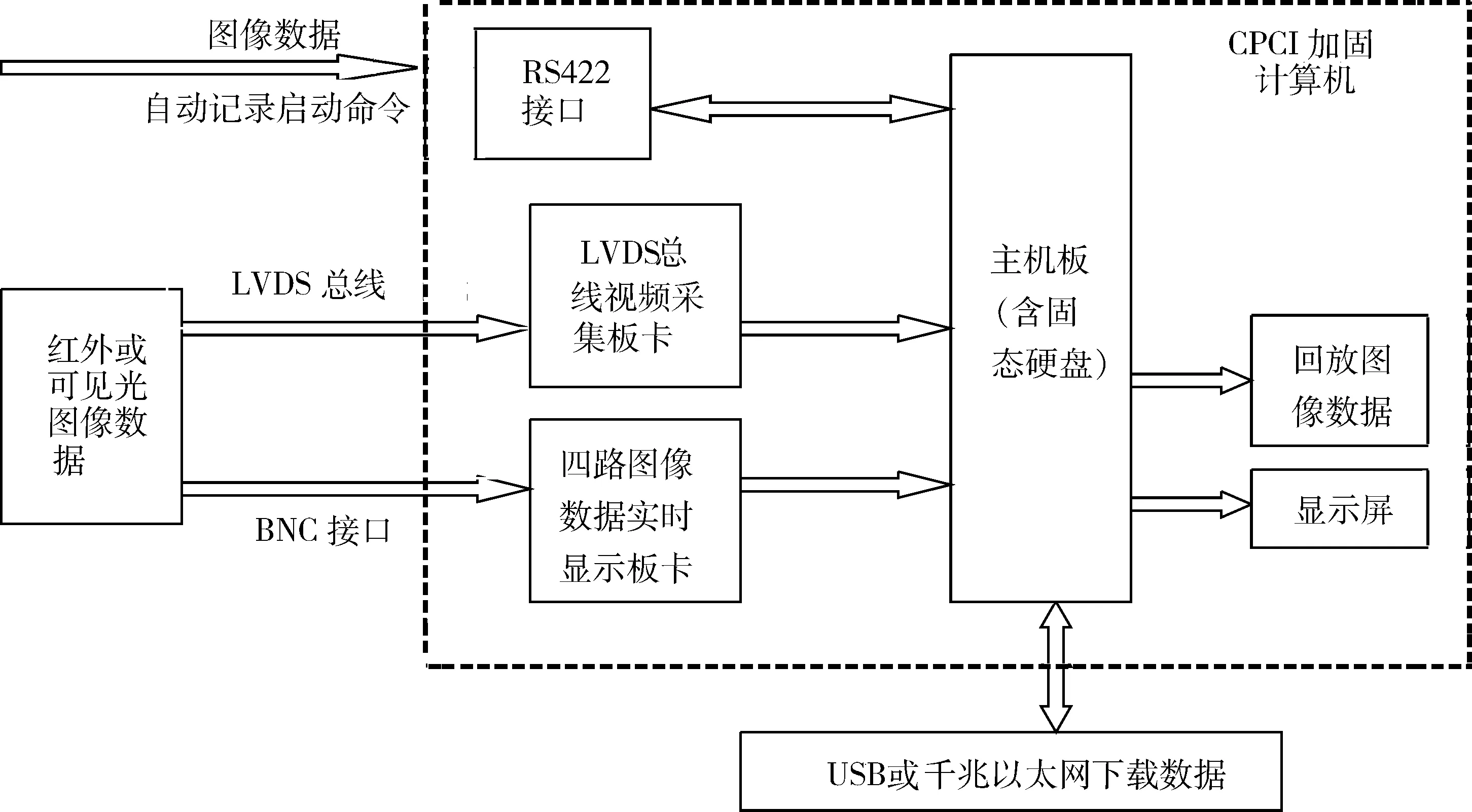

基于CPCI总线的图像数据采集和回放系统主要由CPCI总线计算机、LVDS总线视频采集板卡、主机板(含固态硬盘)和图像数据实时显示板卡构成,组成框图如图1所示。

图1 基于CPCI总线的图像数据采集和回放系统组成框图

图像数据采集和回放系统能对红外(或可见光)图像数据进行实时采集、记录存储,并能在各种试验结束后回放红外(或可见光)图像。主要功能如下:

1)红外(或可见光)视频图像采集,存储,回放;

2)将数据存储在固态硬盘中,文件管理方式,每个文件大小在1GB左右;

3)可以通过USB2.0下载数据,也可以通过千兆以太网口下载数据;

4)图像数据实时显示板卡可以实时显示4路红外或可见光图像;

5)RS422接口可以进行串口通信和命令控制;

6)记录图像状态信息和参数信息。

该系统采用32位,33MHz的CPCI总线,提供带宽132MB/s;采用了高可靠欧洲卡结构,改善了散热条件、提高了抗振动冲击能力和电磁兼容特性;采用了3U的板卡尺寸结构,体积小,集成度高。

该系统采用固态硬盘存储技术。固态硬盘SSD(Solid State Drive) 采用FLASH闪存芯片进行数据存储和读取,它内部没有机械结构,没有数据查找时间、延迟时间和寻道时间。固态硬盘的优点在于:抗振、宽温、无噪、可靠。固态硬盘没有普通硬盘的旋转介质,因而抗振性能和低功耗性能极佳。选用的固态硬盘工作温度为-40℃~85℃,可适应各种恶劣的环境条件。

该系统采集的红外图像数据率为12MByte/s,可见光图像数据率为24MByte/s。如果选用512G固态硬盘,单独存储红外图像,它可存储16h。系统具有良好的扩展性,可以灵活扩展和升级固态硬盘,达到更快的速率和更大的存储容量。

2 LVDS视频采集板卡

2.1 硬件设计

LVDS视频采集板卡采用3U的CPCI板卡架构,原理框图如图2所示。

图2 LVDS视频采集板卡原理框图

1)接收红外成像传感器送来的LVDS差分数字图像数据,发送方使用DS90LV047A(驱动)芯片,接收方应使用DS90LV048A(接收)芯片与之匹配,其接口定义见表1。

表1 图像数据LVDS总线信号定义

红外图像信号时序关系见图3。

图3 红外图像信号时序图

可见光图像信号时序关系见图4。

图4 可见光图像信号时序图

其中,VCLK是24MHz的连续时钟,VSYN是周期为20ms的场同步信号,它的上升沿与VCLK的下降沿对齐,当VSYN为高电平时,每个VCLK的上升沿可以采样到1个4位的图像信息。红外成像传感器每发出4个4位的图像信息后,发出1个字完成信号BSYN,根据这个信号采集卡可把收到的4个4位的图像信息组成1个16位的图像,将该16位图像信息写入FPGA缓存中,并迭加协议帧头、协议帧尾等字符信息;

2) 红外图像1场的数据量:红外实时图像大小为512×320×2 Byte,像素时钟频率24MHz,图像每秒50场;同时通过串口通信要接收80个字节的SER数据,周期为20ms,SER数据在下一个场同步信号下降沿时开始记录,波特率为115.2kbps,分别为1位起始位、8位数据位和1位停止位,无奇偶校验位;

3)由于外部来的第1组数据和VSYN上升沿之间的时间间隔不确定,所以FPGA中使用BSYN信号将4个4位的图像信息组帧成1个16位的图像数据。每帧图像的大小为512×320×16bit=262.14KB,缓冲深度不小于512KB,同时使用硬件DMA存储方式,满足存储图像数据的速率和图像数据不丢失;

4)可见光图像1场的数据量:可见光图像大小为800×600×8bit,像素时钟频率为50MHz,图像每秒50场;各种LVDS信号接口和时序与红外图像接口和时序差别只是BSYN信号将2个4位的图像信息组帧成1个8位的图像数据。只需要简单更改FPGA中组帧代码就可以采集存储可见光图像数据;

5)CPCI接口模块,控制PCI9054 Local Bus和FPGA之间的数据通讯。

PCI9054是一个高性能PCI总线接口芯片,片内集成2个独立的DMA控制器。利用DMA控制器可以进行高速、大数据量传输。当系统准备读写板卡上的寄存器时, PCI9054 Local bus 是slave interface;当板卡准备启动DMA时, PCI0954 Local bus 是 master interface。PCI接口模块就是控制主和从接口的时序,实现高速稳定的数据传输。

2.2 接口电路设计

LVDS视频采集板卡的LVDS总线接收芯片采用NS公司的DS90LV048A,该芯片是3V四路LVDS总线差分线性接收器,最高可达400Mbps转换速率,差分输入端接100Ω匹配电阻。LVDS总线在PCB设计时器件紧挨接口,差分信号线严格等长,外部线缆双绞屏蔽,有很好的电磁兼容效果。差分输入接口电路如图5所示。LVDS差分信号经过DS90LV048A后转换成TTL信号,再经过4通道高速数字隔离器ADUM3440,如图6所示,然后进入FPGA。输出LVDS总线接口电路采用LVDS总线3V四路LVDS总线差分线性驱动器DS90LV047A,其LVDS接口输出接口和隔离电路如图7所示。

图5 LVDS接口差分输入接口电路

图6 LVDS差分输入隔离电路

图7 LVDS接口输出接口和隔离电路

2.3 FPGA设计

LVDS视频采集板卡的FPGA采用Xilinx公司的XC3S1000-4FG456I ,主要完成控制PCI总线时序,控制2个SBRAM协调工作,LVDS总线图像数据接收、组帧和添加传送协议,控制DMA方式启动和数据传送等功能。FPGA程序的Top模块包括BUFG_B,DCM_B,PCI_INTERFACE,ARBITER,DMA_CON,RD_ST,ASYNFIFO和FRAME_PROCESSOR等功能模块,如图8所示。

BUFG_B模块是芯片输入全局时钟缓冲单元,FPGA内的时钟要走专用时钟线。DCM_B是时钟信号调整单元,DCM是FPGA内部的元件,可以提供占空比校正、频率综合、倍频和分频等功能。PCI_INTERFACE是PCI接口模块,控制PCI9054 local bus和FPGA之间的数据通讯。ARBITER仲裁单元控制2个外部SBRAM,实现交叉读写操作,提高总线利用率,缓存大量高速数据。DMA_CON单元主要功能是控制PCI9054DMA通道0, 首先要接收来自于流控制单元输出的DMA启动信号,然后开始设置PCI9054DMA寄存器,最后判断DMA是否完成。RD_ST模块是数据流控制器,读出ASYN_FIFO模块中的数据,然后存储到ARBITER单元,判断一场图像数据是否完成,然后通知DMA_CON模块,启动DMA。ASYNFIFO模块是ISE core generator软件产生的IP CORE,用于完成异步时钟域通讯。FRAME_PROCESSOR模块完成可见光或者红外光图像串行数据转成并行数据、添加主帧头、添加视频数据帧头、添加视频帧序号、添加图像状态帧头、添加帧尾、帧格式控制、接收SER状态数据,并临时存储等功能。

图8 LVDS视频采集板卡的FPGA架构

3 软件设计

启动软件程序后选择视频采集功能,在图像格式单选按钮中选择图像格式红外图像或可见光图像,然后在下方的功能选择多选框中勾选需要的功能:显示或存储。配置完成后点击开始按钮进行数据的采集和记录,完成后点击暂停结束采集工作。

数据采集过程中若选择了显示功能,则程序会在左侧的图像区域内显示当前采集到的视频图像,如图9所示。

图9 红外(或可见光)采集功能界面

启动软件程序后选择视频回放功能,在图像格式和回放模式中进行所需的设置。然后打开之前保存的视频文件。当选择单帧回放模式时,需要在下方的文本框内输入起始时间,然后点击下一帧或上

图10 LVDS接口红外图像采集板卡软件回放界面

一帧进行图像单帧回放;当选择连续回放模式时,在下方文本框内输入回放的起止时间,然后单击开始按钮进行视频回放。

4 结论

基于CPCI总线的图像数据采集和回放系统采用CPCI总线和LVDS总线,实现了长时间、高带宽、高速稳定的图像数据存储,并通过USB2.0或千兆以太网迅速下载,可以回放挂飞或其他大型试验的整个过程的图像数据。

[1] PCI9054 Data Book[Z].PLX Technology Inc.,2000.

[2] CompactPCI Specification Revision 2.2[S].PCI Industrial Computers Manufacturers Group 1999.

[3] DS90LV048A Data Sheet[Z].NS Inc,2001.

[4] DS90LV047A Data Sheet[Z].NS Inc,2001.

[5] Spartan-3 Data Sheet[Z].Xilinx Inc,2007.