硬件失效安全性分析研究

2013-05-08刘伟超黄彬彬孟庆尧

刘伟超 师 进 黄彬彬 孟庆尧 江 明

(北京全路通信信号研究设计院有限公司,北京 100073)

刘伟超,男,硕士毕业于北京航空航天大学,工程师。主要研究方向为ATP底层平台支持,曾参与8号线、长春轻轨3期等项目。

“故障-安全”是铁路信号安全技术的核心和特点,也是所有安全相关信号设备所必须满足的安全需求,设计团队需要不断“挖掘”并“修复”设计当中可能存在的各种“风险”。针对硬件电路设计,对于器件失效导致风险的分析过程常常采用的手段包括FTA、FMEA等,但这些传统的方法本质上提供的是一种思想,是分析问题的一个思路,而具体的实现需要靠人和设计团队。当电路规模较大或复杂度较高时,分析所花费的时间就会指数增加,人员占用严重,同时“漏判”的概率也在增加。基于以上原因,在电路仿真技术飞速发展的今天,考虑将电路仿真技术引入到FTA、FMEA分析当中,也就是将故障注入技术与电路仿真技术相结合,这也许是一种实现电路故障分析及设计的有效方法,能够极大降低设计者的工作负担,并提高设计的正确性。

在电路故障分析中引入计算机仿真的方案早在上世纪80年代起国外就已开始开展相关的研究,比如美国的ADEPT、DEPEND,丹麦的MFM,日本的GO_FLOW项目等,国内这方面起步较晚,且由于成本等多方面因素并未在民用领域广泛推广。本文阐述的仿真平台是针对铁路应用特殊需求并结合国内先进的电路仿真软件开发的一套适合工程化应用的硬件分析平台。

1 硬件故障注入的基本原理

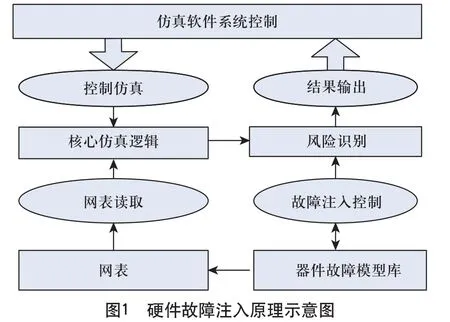

硬件故障注入是以电路网表为核心进行的,基本原理如图1所示。

最顶层为“仿真软件系统控制”层,主要负责完成软件的用户接口功能以及各功能模块的调度。电路仿真软件读取电路网表(SPICE)完成基本电路仿真并将仿真结果输出;网表部分为待仿真电路的SPICE格式网表;器件故障模型库存储失效器件故障模型;风险识别模块负责读取电路仿真软件的输出,并根据风险判断规则生成最终的报告。

下面以最简单的一个例子说明系统的工作流程。

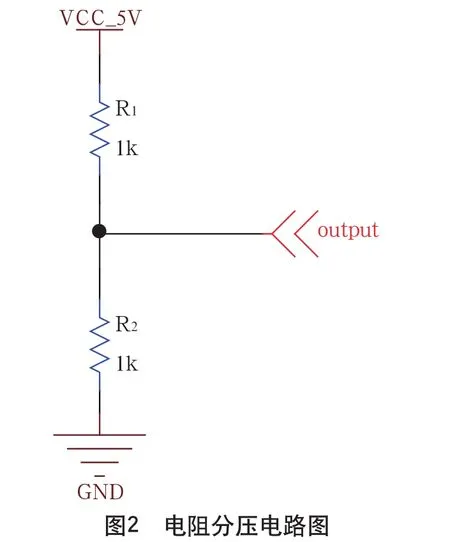

工作电路如图2所示,是一个简单的两电阻分压电路,R1、R2均为1 kΩ输出output为2.5 V,现对于R1阻值在500 Ω至断路范围内变化(步长为1 Ω,断路状态等效于100 MΩ)进行失效仿真,假定输出电压大于3 V即定为危险状态。

首先利用器件故障模型中R1=500 Ω器件替换当前网表内的R1电阻,进行电路仿真将电路输出output(3.3 V)送至风险识别单元,风险识别单元根据危险状态判断原则判定该故障存在风险,并进行记录;随后系统利用R1=501 Ω器件替换当前网表内R1电阻,继续上述流程直至所有R1可能取值被扫描完全。

2 硬件故障注入协同仿真的优势

传统的FMEA、FTA分析,仅仅给出方法论,最终的具体实现依靠设计团队,在具体的实践过程中,发现存在以下的弊端。

1)分析时间较长,人力资源占用严重;

2)分析结果与设计团队人员水平相关;

3)多次迭代设计后,分析人员易产生固化思维,对于潜在问题的敏感度下降;

4)在FTA分析中,对于多器件组合失效的判断较为困难,特别是在电路规模较大情况下,容易产生遗漏。

从上面论述可以看出,传统分析方法的主要弊端在于人,因此“基于故障注入的电路仿真”尽量将人为因素排除,设计人员仅仅需要指定仿真范围、各类器件的失效形式以及风险识别的原则,具体的识别过程是可重复的,由计算机负责完成,因此最大程度避免了上述传统设计方法的弊端,这也是相对于传统设计方法的优势所在。

3 元器件失效的建模

针对失效仿真的元器件建模,主要考虑两方面内容:一方面是元器件基本功能(正常行为)的模拟,该过程主要参考厂家提供的器件手册;另一方面是元器件在失效情况下行为的模拟,该过程以EN50129为标准,并将EN50129所规定的定性故障模式进行量化。

3.1 元器件基本功能建模

我们当前所使用的仿真平台也是以SPICE为核心。SPICE仿真所使用的均为基本的元件和单管,因此,对于基本元器件包括电容、电阻、普通二极管等都有标准的仿真模型可以直接使用,仅仅需要根据实际使用环境对参数进行调整即可。在此基础上,对于较复杂的器件,可以按照其行为,利用基本器件进行搭建。

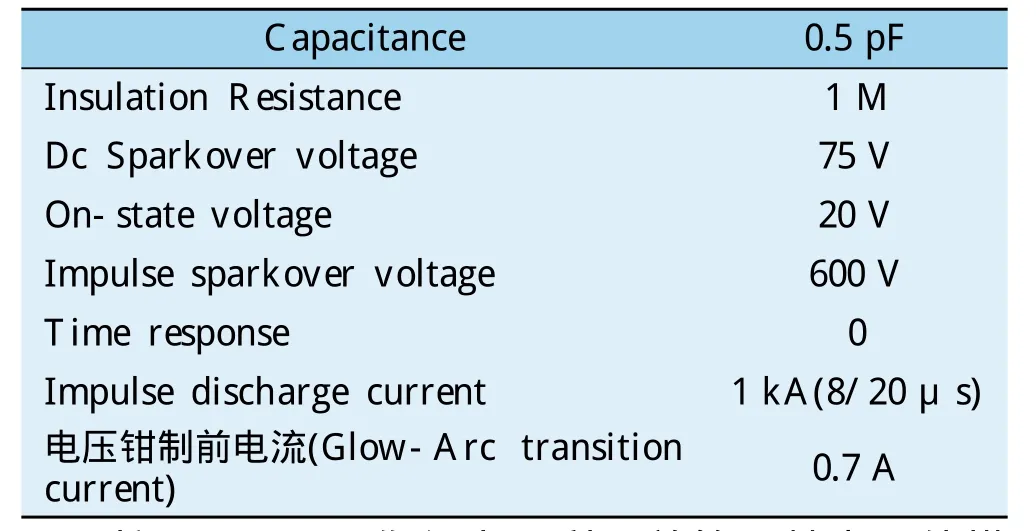

比如GDT器件,GTCS23,工作参数如表1所示。

表1 GTCS23 工作参数列表

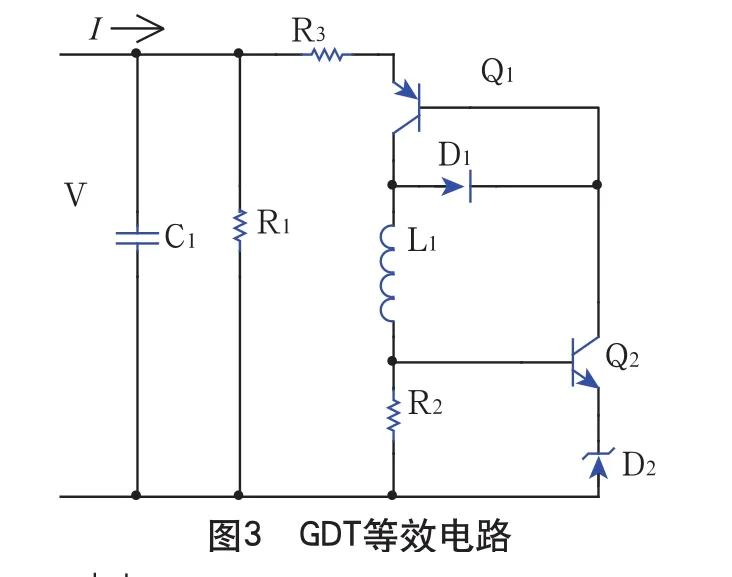

按照GDT工作行为,利用单管及基本器件搭建等效电路如图3所示。

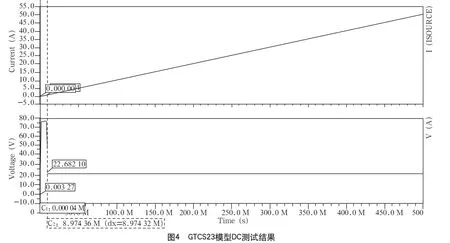

针对该器件,进行DC测试结果如图4所示。

AC测试结果如图5所示。

以上结果可以看出,GDT模型设计基本满足原有工作参数。

3.2 元器件失效行为建模

元器件的失效,可以认为元器件的参数发生恶化,导致对外行为的异常。针对与仿真应用,需要确定以下两方面内容。

1)变化的参数是什么;

2)该参数变化值。

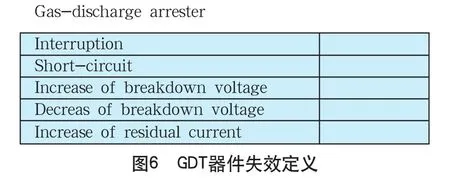

首先需要对变化的参数确认。对于器件,有些参数是明确可以认定的,比如电阻,当阻值变大或减小,变化的参数均为电阻值,很明确。但对于一些参数并不明确的器件,为了简化建模过程,需要人为引入该参数。仍以上述GDT器件为例,EN50129中对于器件失效定义如图6所示。

下面依次实现上述失效形式(器件标号参考图 3)。

1)Interruption:调节R3电阻值至100 MΩ,此时对于GDT在电路中行为与断开一致;

2)Short-circuit:调节R1电阻值至0.01Ω,此时对于GDT在电路中行为与短路一致;

3)Increase of breakdown voltage:提高稳压管D2击穿电压值,此时对于GDT外部行为与击穿电压提高一致;

4)Decrease of breakdown voltage:降低稳压管D2击穿电压值,此时对于GDT外部行为与击穿电压降低一致;

5)Increase of residual current:增加电感L1的电感量,GDT被击穿后残流增加;

对于上述实现,GDT参数改变分两类:一类是实现GDT正常行为所必须的,比如2)、3)、4)、5)条,所针对的器件本身在实现GDT正常行为过程中发挥重要作用;另一类是为实现GDT失效型式所引入的,比如第1)条当中的R3,这个器件对于实现GDT正常行为的模拟没有作用,但能够更简洁实现Interruption的行为。

在确认变化的参数后,对于器件参数变化范围需要进行明确规定。因为涉及到计算机仿真,因此对于简单的电阻短路、断路不能使用理想0 Ω或∞,这对于计算机容易造成除0错误或算法不收敛。因此这里假定对于短路情况电阻设定为0.01 Ω,对于断路情况,电阻设定为100 MΩ即可,其他情况以此类推。

4 安全侧的定义和检验

在图1中,“风险识别”模块是整个仿真平台的核心。在具体实践过程中,设计人员首先利用自然语言描述系统的安全侧(该描述应来源于系统需求),针对于具体电路,设定并量化接口侧的对应关系(由于利用计算机进行器件失效分析,因此电路内部工作结果可以考虑,仅仅需要定义输入、输出的关系)。最后,根据量化后的接口对应关系以及系统安全侧定义确定“风险描述”,概括起来就是“在A输入条件下如果产生输出为B时,将会导致系统风险”(A、B均为量化条件)。

在风险识别阶段,“风险识别”模块读入仿真输出结果(接口侧的电压、电流值),并根据上述定义的“风险描述”筛选可能出现风险的case并形成最终报告。在具体实践过程中,风险识别的判断通过SPICE的measure语句实现。

5 实践案例

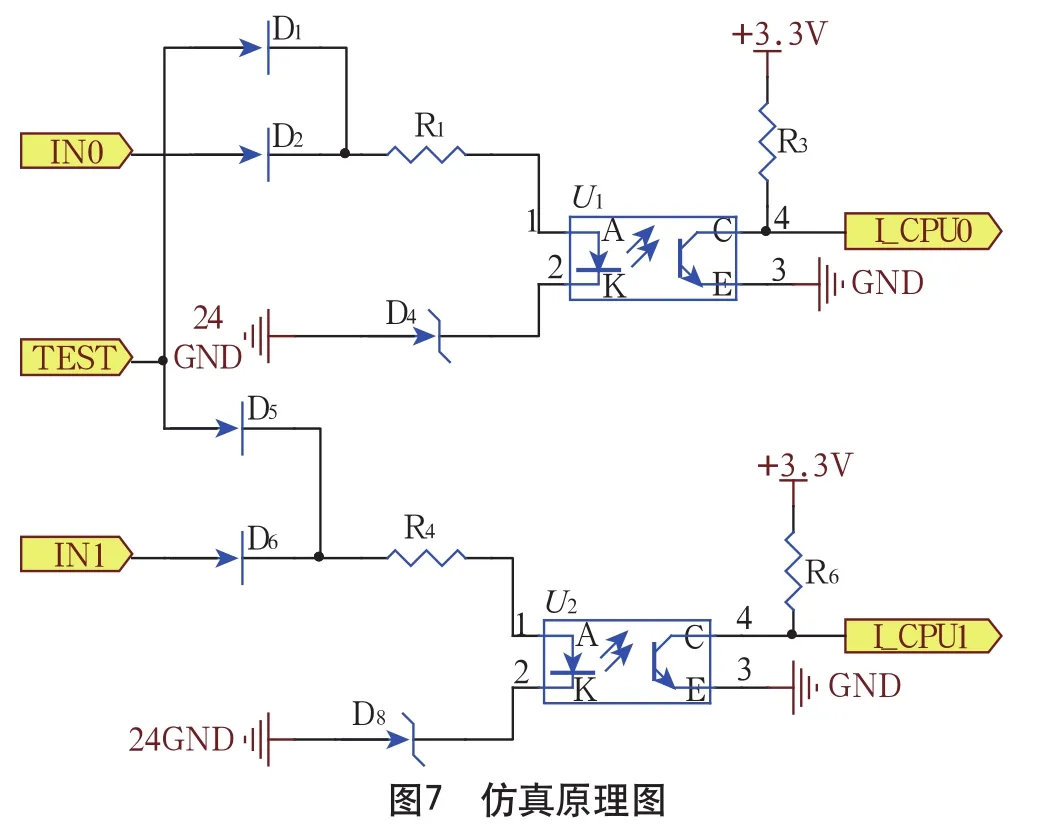

原理如图7所示。

该电路为简单的输入采集电路,当输入IN0为高电平(24 V)时,输出I_CPU0为低电平‘0’;当输入IN0为低电平(0 V)时,输出I_CPU0为高电平(3.3 V)。同理,对应第二通道。定义:“当没有输入的情况下采集到输入视为危险情况”,对应电路中,当IN0为‘0’(V_IN < 9 V)且I_CPU0为‘0’ (V_ I_CPU0 < 2 V)或当IN1为‘0’(V_IN < 9 V)且 I_CPU1 为‘0’ (V_ I_CPU1< 2 V)时,定义为危险情况。按照下述步骤进行。

1)利用Protel输出该电路网表“testcase.nsx”;

2)设定电路激励:IN0为5 Hz方波,IN1为2.5 Hz方波;

3)设定器件扫描范围:对于所有器件的所有失效模式进行扫描,存在最大两器件组合同时失效情况;

4)设定风险识别原则:“当IN0为低电平时,若I_CPU0为低电平,则为危险侧或当IN1为低电平时,若I_CPU1为低电平,则为危险侧”,并编写对应的measure语句;

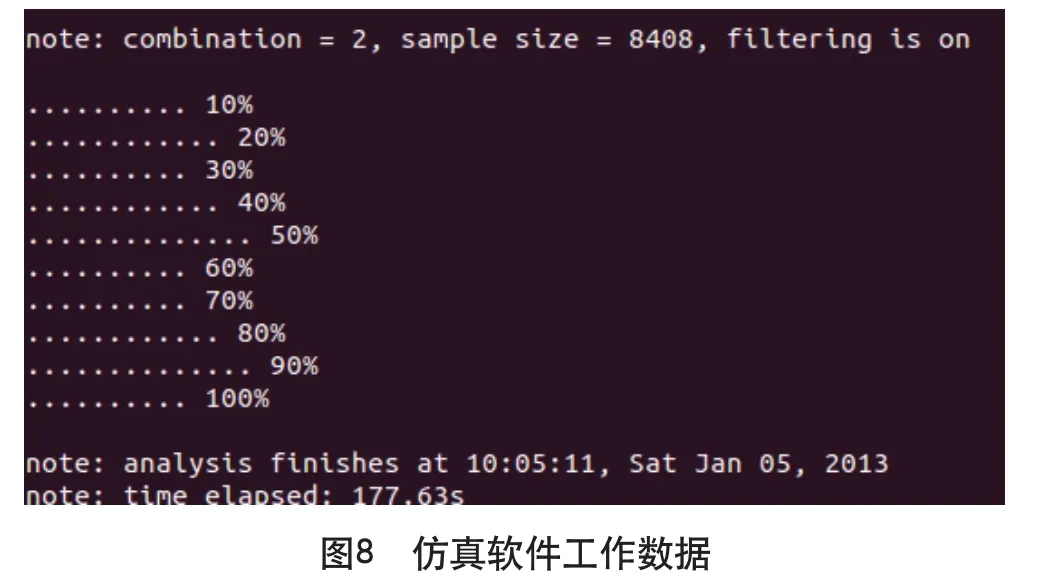

共扫描案例8 408个,耗时177.63 s,数据如图8所示。

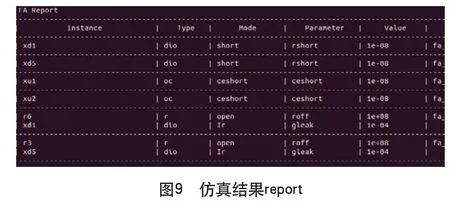

如图9所示,根据扫描结果判定当d1或d5短路后将出现IN0与IN1间串扰;U1或U2的ce间短路将造成电压的误采集;r6断开并且d1反向漏电流增加时的组合故障导致输出电压I_CPU0出现错误电平(在本案例中,r6断开导致I_CPU0呈现高阻态,但在实际工作过程中,由于I_CPU0将会接有负载,因此该种失效模式不会带来风险), 同理r3断开与d5反向漏流的增加同样导致I_CPU1出现错误电平。分析结果与实际工程人员FTA分析一致。

6 面临的问题及挑战

从建模上可以看到,引入仿真系统后最大的工作量就是器件的建模过程,对于新增加的器件往往要付出比较大的时间进行模型建立及验证;对于较为复杂的元器件比如大、中规模集成电路建模过程更为复杂,实现难度较高;

从计算角度而言,随着电路规模增加、分析同时失效器件数目的增多,系统的计算量将呈指数形式增长。但随着多核技术以及云计算技术的发展,仿真计算速度将有质的飞跃。

7 结束语

本文阐述了基于电路仿真技术的失效仿真技术的基本原理以及基本的建模方法,并通过简单的案例证明的该技术的可实施性,该方法具有很高的工程实用价值,可以贯穿产品的整个设计周期。放眼将来,随着计算机技术的发展,计算机仿真技术将渗透到传统信号设备设计周期的各个方面,仿真技术的应用将会大大提高设计效率、减少设计中的缺陷、提高产品的安全性与可靠性。

[1]赵广燕,孙宇峰,杨立波.电路功能可靠性仿真平台的设计[J]. 系统仿真学报,2005,17(12):2931-2934.

[2] EN50129 Railway applications: safety related electronic systems for signaling[S].

[3]郭梁,马立元,郭礼,等.基于仿真的电子元器件故障模型研究[J].工程设计学报,2008,15(2):145-148.