四管像素满阱容量影响因素研究*

2013-04-27姚素英徐江涛张冬苓

孙 权,姚素英,徐江涛,徐 超,张冬苓

(天津大学电子信息工程学院,天津300072)

CMOS图像传感器因其更低的功耗,更低的成本,更高的集成度[1],以及可以在像素级别与CMOS模拟及数字电路更好的集成[2],因而得到了迅猛发展。CMOS图像传感器广泛应用于安防、科学研究、工业控制、数码终端等领域[3]。通常的CMOS图像传感器像素结构包括三管、四管与五管像素,三管与五管像素因为不能使用相关双采样而具有较高的随机噪声[4-5]。引自电荷耦合器件 CCD(Charge-Coupled Device)技术中的表面钳位光电二极管结构PPD(Pinned Photo-Diode),使得硅与二氧化硅的界面得以更好的隔离,大大减小了暗电流,同时提高了短波长光的响应[6]。因此带有表面钳位光电二极管的四管像素结构成为当前CMOS图像传感器像素结构的主流。像素的满阱容量是指通过光电二极管可以收集并顺利转移至浮空节点FD(Floating Node)的最大可用光生电荷数[7]。低的满阱容量会降低像素的动态范围、信噪比以及灵敏度,从而严重降低图像的质量,在当今小像素应用逐渐增加的条件下显得尤为严重[8]。国内外已经提出了很多提高满阱容量的方法。例如在像素曝光期间,在传输管栅上加一个负偏压,提高光电二极管与传输栅之间的电子势垒,从而有效的增大像素满阱容量[9],但外围电路很难产生需要的负偏压。也可以通过增大PPD的电容来增大像素的满阱容量,包括在光电二极管中横向注入P型杂质从而扩大耗尽区[10],或者在光电二极管中多次注入P型杂质,形成蜂窝状光电二极管[11],但是上述方案工艺均相对比较复杂,很难在标准工艺中实现。

本文分析了影响四管像素满阱容量的主要因素,着重分析了PPD电容对满阱容量的影响,得到PPD周长、面积对满阱容量的模型公式,采用0.18 μm CMOS工艺进行了像素流片测试,并根据流片测试结果进行了拟合。其次,针对像素积分时间内由于PPD向FD的漏电而造成的满阱容量的减小,本文通过在PPD与FD之间增加P型注入的方法来提高电子势垒,减小漏电,有效的提高了像素满阱容量。通过对比不同工艺条件下实际流片测试结果,验证了本文提出的方法。

1 像素满阱容量影响因素分析

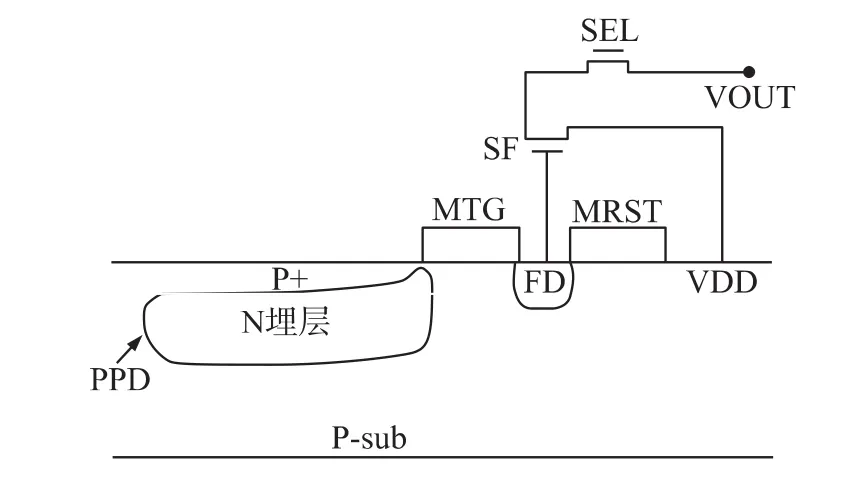

本文所有的研究均基于四管(4T)像素结构,如图1所示。4T像素包括钳位光电二极管(PPD),传输管(MTG),浮空节点(FD),源跟随器(SF),复位管(MRST)以及行选择管(SEL)。PPD是由高掺杂浓度的P型表面钳位层P+、N埋层以及P型衬底构成。

图1 4管像素基本结构

像素的满阱容量是指PPD经过耗尽区收集到的,并且可以在读出时间内通过传输栅转移至FD的最大光生电子总数。主要受PPD电容、FD电容,以及自PPD向FD的电荷转移效果三方面的影响。PPD用于产生并收集光生电子,而FD负责将转移来的相应的光生电子转变为对应的相关双采样输出信号并传输至列总线。电荷转移效果对有效势阱容量有很大影响。PPD势阱中产生并收集的光生电子,只有全部转移至FD,转变为相应的相关双采样信号输出,才能形成有效的图像数据。FD电容如果较小,会导致无法容纳由PPD转移至FD中的光生电子,尤其是当PPD较大时更为明显,此时像素满阱容量将受限于FD电容的大小。这种情况下PPD储存的光生电子会在FD处不断的向外溢出,形成向FD周围衬底的漏电,造成PPD势阱无法产生并收集足够多的光生电荷的假象,限制了像素实际可用满阱容量。

图2为正常大小FD与较小的FD两种光响应曲线的对比。由于较小的FD具有较小的电容,因此在FD达到饱和之前,相同曝光量会产生更大的电压变化,输出更大的信号值,通常以ADU(Analog to Digital Unit)计算。

图2 FD对输出的影响

下面主要讨论PPD电容对像素满阱容量的影响。PPD可以收集到的光生电子总数QPPD可由式(1)计算得到

其中CPPD是钳位光电二极管 PPD的电容,ΔV是PPD内电荷转移前后的电势差,它取决于像素的工艺条件以及像素内光生电子的转移情况。在相同的工艺条件和电荷转移情况下,ΔV相同,则CPPD越大,QPPD越大,阱容量越大。钳位光电二极管PPD的电容,由PPD底面电容与侧壁电容的和来决定[12]。可由式(2)表示为

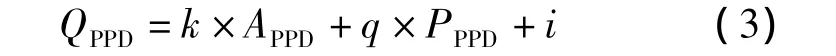

其中Cj为PPD底面电容,与PPD的底面面积成正比;Cjsw为PPD的侧壁电容,与PPD侧壁面积成正比。侧壁面积可以近似由PPD的底面周长与结深的乘积来表示,而PPD的结深是由具体的像素工艺条件决定。当像素的工艺条件确定时,PPD的电容即可由PPD的底面面积与底面周长来近似表示,即式(3)

其中APPD为PPD的底面面积,PPPD为PPD的周长,k、q、i为待定常数。

采用0.18 μm CMOS工艺对4T像素进行了流片测试,像素面积为15 μm×15 μm,其中PPD的N埋层使用85 keV,1.0×1012/cm2的磷注入,表面钳位层使用15 keV,5.0×1013/cm2的二氟化硼注入,实际测试参数如表1所示。

表1 PPD面积、周长与满阱容量的关系

由表1可以得出,增大PPD的面积与周长可以显著的增大其满阱容量。PPD的面积越大,其内部有更多带正电的施主离子,增大了耗尽区收集光生电子的储存区域。而增大PPD的周长,可以有效增大PPD的耗尽区,同样增大了收集光生电子的区域。使用MATLAB仿真对实测像素面积、周长及满阱容量进行了拟合。拟合得到式(4),

拟合曲线如图3所示。

图3 PPD面积、周长拟合曲线

2 防穿通注入

在像素积分期间内,即传输管关断时,PPD内积累的光生电子越来越多,由于FD电势较高,其对PPD内部储存的光生电子的吸引可能会导致PPD内部的电子流向FD,形成漏电流,严重减小像素的满阱容量。

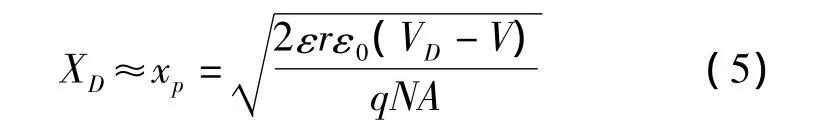

如图1所示,在传统的4T像素设计中,PPD与FD之间区域由衬底构成。PPD与FD之间的距离基本可以认为是传输管的栅长,在FD复位过程中,(采用的0.18 μm CMOS 工艺中的电源电压为 3.3 V),其电势为3.3 V减去复位管的阈值电压,这个较高的电势会对此时储存在PPD内部的光生电子产生较强烈的吸引作用。根据半导体物理理论,PN结耗尽区宽度XD由以下公式给出

其中,ε0为绝对介电常数,其值为8.85 ×10-14F/cm;εr为硅的相对介电常数,其值为11.6;VD为PN结内建电势,其值一般在0.6 V ~0.9 V之间,本文中取0.75 V;V为PN结两端的电势差,正向时V>0,反向时V<0;NA为衬底的掺杂浓度,本文中为1×1015/cm3。若取FD电势为2 V,即V为-2 V,代入式(5),可以得到FD与衬底的之间的耗尽区宽度为1.89 μm。而传输管的栅长为700 nm,即PPD最靠近传输栅的一侧将处于FD与衬底形成的耗尽区之中,因此PPD中储存的光生电子也将处于此耗尽区的电场之中,形成流向FD的漂移电流;同时还存在由扩散引起的自PPD流向衬底的PN结反向电流。这个自PPD向FD方向的漏电流,会导致大量光生电荷的损失,造成像素满阱容量的大幅减小。

利用软件对FD在复位的过程中传输栅下电子电流密度的情况进行了仿真,结果如图4所示。可以看出,此时PPD中电子有很大一部分在向FD流动,因而造成了二者之间较大的电子电流密度。

图4 电子电流密度二维仿真

可以防止此漏电的方法有2种,第1种是加大PPD与FD之间的距离,即传输管的栅长,以致超出FD与衬底之间的耗尽区宽度,这样PPD就不会暴露在耗尽区电场之中。第2种方法是在PPD与FD之间增加一种P型注入,增大其掺杂浓度,减小与FD之间的耗尽区宽度。根据式(5)可以得到增加其掺杂浓度为1×1017/cm3,就可以使耗尽区宽度减小为原先的1/10。这次注入为防穿通注入。

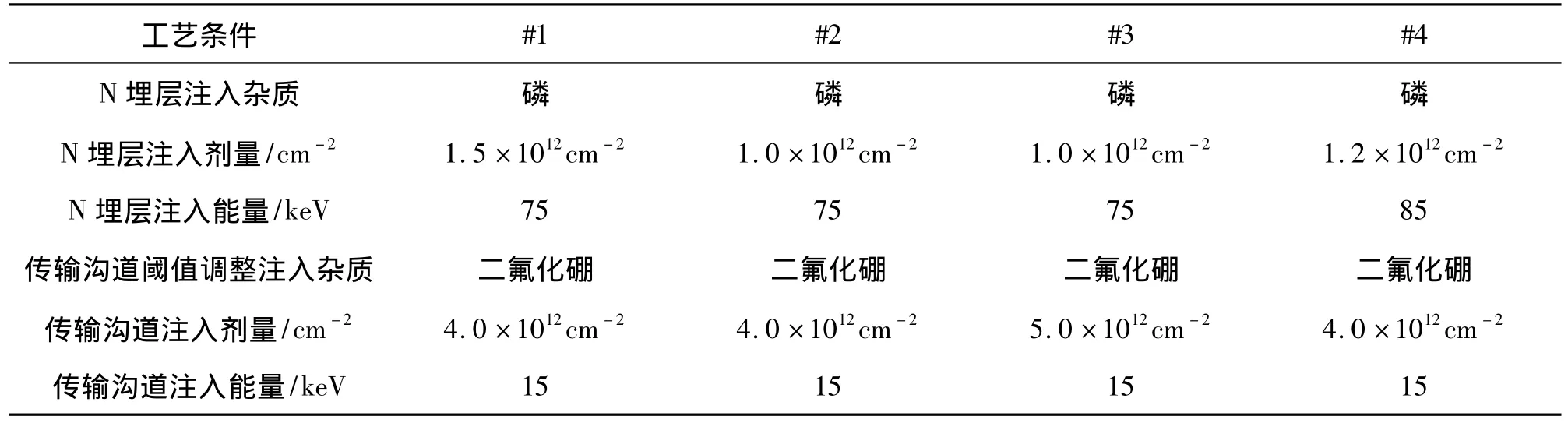

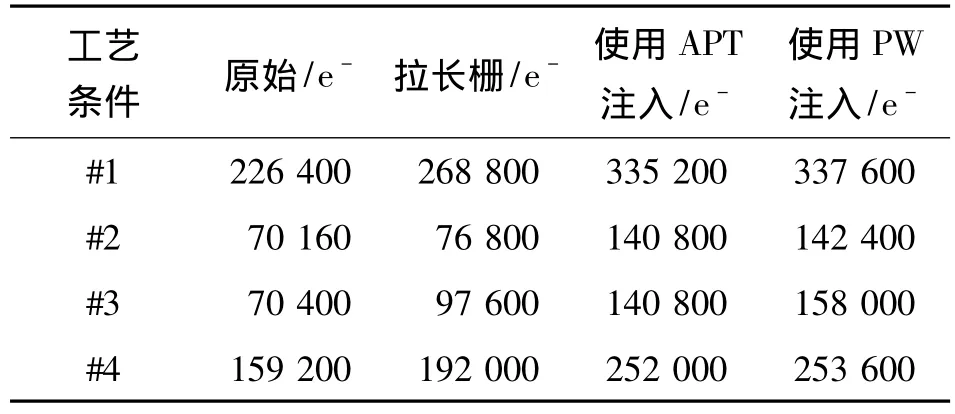

将700 nm的传输管栅拉长至1 μm,可以在一定程度上实现第1种方法。对像素增加一层P型注入,称之为防穿通APT(Anti-Punch Through)注入,或者使用工艺流程中的P阱(P-Well,PW)注入,将其置于PPD与FD之间,即可实现第2种方法。通过软件仿真了4种不同工艺条件下,采取这三种具体实施方式之后的满阱容量。4种工艺条件的主要参数如表2所示,其对应的仿真像素满阱容量如表3所示。

表2 不同工艺条件主要参数

表3 仿真像素满阱容量

由表3可知,将传输栅拉长,使PPD尽量移出FD的耗尽区,能够在一定程度上缓解由于漏电造成的满阱容量的减小。而使用APT注入或者使用PW注入增加传输栅下掺杂浓度的方式,都能在很大的范围内有效增加像素满阱容量,获得较好的效果。

3 流片测试结果

经过实际流片测试,原始的像素结构在实际流片测试后,由于漏电严重,其满阱容量基本可以忽略。拉长传输栅之后,获得改善效果非常小。只有使用APT或者PW增加掺杂浓度的方式能够有效的增加像素满阱容量。以#2号工艺条件为例,给出原始以及3种具体实施方式的像素光响应曲线,如图5所示。

图5 实测光响应对比

正常工作的像素,在曝光时间一定的条件下,随着光照强度的逐渐增加,单位时间内可以产生的光生电子-空穴对也会相应增加,其相关双采样的输出值变大,直至PPD达到满阱状态,此时即使光照强度继续增加,由于PPD内可以容纳的电子总数已达到最大值,则像素的输出值将基本不再变化。即像素输出随光照强度的增大而增大,并在像素达到满阱时而达到饱和。从图5可以看出,采用原始的像素结构,其光响应曲线基本保持较低水平。而将栅拉长之后的像素结构,光响应水平得到提升,但效果非常有限。只有使用PW注入与使用APT注入的两种像素结构能够实现正常的像素功能。由此可见,在PPD与FD之间必须加入一层P型掺杂的注入,来防止自PPD向FD的漏电,从而提高像素的满阱容量,实现正常的像素功能。

实际测试不同工艺条件下,4种不同像素的满阱容量如表4所示。由于原始的像素结构与拉长栅的像素结构,其沟道穿通比较严重,满阱容量在实际测试中无法精确获得。且由于软件仿真与实际测试的差异,对于可以测量满阱容量的像素结构,测得的数值较软件仿真相比也小了很多,但是能够得出防穿通注入不可缺少的结论。

表4 测试像素满阱容量

4 结论

分析了影响4T像素满阱容量的主要因素,即PPD电容、FD电容以及电荷转移情况。着重分析了PPD电容对满阱容量的影响,得到PPD周长、面积对满阱容量的影响关系,并通过MATLAB对实际测试结果进行了拟合。针对积分时间内由于FD的高电势对PPD中的光生电子的吸引而导致的漏电使像素满阱容量减小的问题,可以通过在PPD与FD之间增加一次P型注入或者PW注入,增加其掺杂浓度,从而减小PPD与FD之间的耗尽区宽度,使PPD远离FD耗尽区的电场,减小了由于FD的高电势而引起的PPD严重漏电流,从而提高了像素的满阱容量。增加一次P型注入和使用PW注入均依据其功能称为防穿通注入。流片测试结果表明,使用PW或增加一次P型注入的效果较好,能够顺利实现像素的基本功能,其光响应曲线正常。而未使用防穿通注入的像素结构,都得不到正常的像素功能。使用新增P型注入的方式,需要在整个像素的工艺流程中增加一层掩膜版,而使用PW的方式,没有引入任何其他的改变,可以有效节约成本。本文结果对研究像素满阱容量有一定的借鉴价值。

[1] El Gamal A,Eltoukhy H.CMOS Image Sensors[J].IEEE Circuits and Devices Magazine,2005,21(3):6 -20.

[2] 赵士彬,姚素英,徐江涛.基于压缩感知的低功耗高效率CMOS图像传感器设计[J].传感技术学报,2011,24(8):1151-1157.

[3] Liu X,Fowler B,Hung Do,et al.High Performance CMOS Image Sensor for Low Light Imaging[C]//Proc,2007 International Image Sensor Workshop,June 7 -10,2007 Ogunquit Maine,USA.

[4] 张钰.一种新的片上抑制CMOS图像传感器暂态噪声方法[J].传感技术学报,2011,24(6):859 -863.

[5] Zhou Yangfan,Cao zhongxiang,Li Quanliang,et al.Image Lag Optimization of Four-Transistor Pixel for High Speed CMOS Image[C]//International Symposium on Photoelectronic Detection and Imaging 2011 - Advances in Imaging Detectors and Applications,Proc.SPIE,2011,8194:819435.

[6] Lee P P,Guidash P M,Stevens E G,et al.Active Pixel Sensor Integrated with a Pinned Photodiode [P].USA Patent,No.5625210,1997.

[7] Hinckley S,Gluszak E A,Eshraghian K.Modeling of Device Structure Effects in Backside Illuminated CMOS Compatible Photodiode[C]//Proceedings Conference on Optoelectronic and Microelectronic Materials and Devices 2000,Melbourne,399 -402.

[8] Agranov G,Smith S,Mauritzson R,et al.Pixel Continues to Shrink Small Pixels for Novel CMOS Image Sensors[C]//International Image Sensor Workshop,June 26 -28,2009 Bergen,Norway.

[9] Bongki Mheen,Young-Joo Song,Albert J P Thwuwissen.Negative Offset Operation of Four-Transisitor CMOS Image Pixels for Increased Well Capacity and Suppressed Dark Current[J].IEEE E-lectron Device Letters,2008,29(4):347.

[10] Younsub Lim,Kyunglak Lee,Heejeong Hong,et al.Stratified Photodiode a New Concept for Small Size-High Performance CMOS Image Sensor Pixels[C]//Proc,2007 International Image Sensor Workshop,June 7 -10,2007 Ogunquit Maine,USA.

[11] Wang Ching-Chun.A Study of CMOS Technologies for Image Sensor Applications[D].National TsingHua University,Taiwan,August 2001.

[12] SuatUtku Ay.Photodiode Peripheral Utilization Effect on CMOS APS Pixel Performance[J].IEEE Transactions on Circuits and System -1:Regular Papers,2008,55(6):1405 -1411.