基于故障统一模型的故障检测策略

2013-04-25王锐

王 锐

(合肥工业大学 电子科学与应用物理学院,安徽 合肥230009)

多目标故障检测通过信号违规检测能实现同时在线检测多种故障,其中包括老化故障预测。文献[1~2]对比做了较有价值的研究。中科院计算所鄢贵海博士基于此方法提出了一种统一的故障模型——侵犯信号稳定性(Stability Violation,SV)以及基于SV的故障检测方案SVFD。但因为多目标会导致多时序约束,所以,对电路的时序有严格要求。本文研究发现,对于动态CMOS电路的“充放电”时间,统一故障检测方法并未予以重视,在严格要求时序的高速电路中,需做出优化。

根据软错误和电路老化的诱导机制不同,现有单独对软错误或者老化预测结构进行改进不能满足要求。要将预测老化和检测软错误等其它目标故障整合在一个结构中进行违规检测,建立新的理论基础。通过数字信号学分析可以得到如下结果:由跳变、毛刺或串扰等引起的延迟故障都可以统一描述为信号稳定违规,因此可以提出统一的故障检测模型,从而在检测能力、设计复杂度和成本方面达到要求。

1 研究现状

基于上述要求,对于统一故障模型,SV期望研究的目标故障类型如下:

(1)软错误。包括单事件翻转(Single Event Upset,SEU)和单事件瞬态(Single Event Transient,SET)[3]。如果一些高能辐射粒子诱导存储单元发生翻转,这种偶然的翻转被称为SEU。如果粒子导致某个组合逻辑的节点收集了足够多的电荷,可以产生瞬态电流脉冲。该脉冲转化成电压脉冲并随着组合逻辑向下传播。这种类型的错误被称为SET。基于3种屏蔽效应[4],软错误可能被捕获:逻辑屏蔽,电屏蔽和锁存屏蔽。

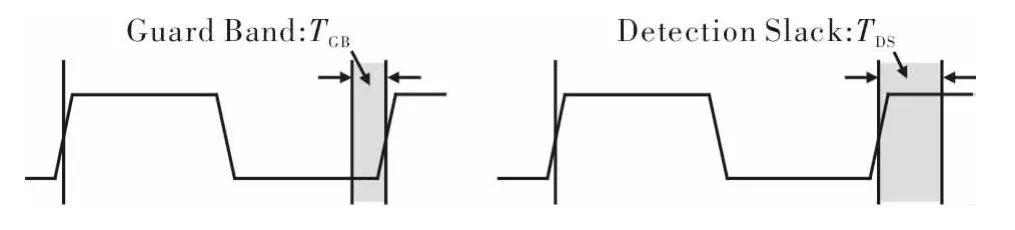

(2)老化延迟。老化效应,例如负温度不稳定性导致的老化延迟可以用来对老化进行预测[5]。通常,老化延迟是时间的一个累积效应。它的检测时间窗为TGB。

(3)延迟故障。延迟故障是指传统的延迟故障,一般由器件故障,包括由缺陷、串扰、电压不稳等导致的时延故障。这类故障的检测通常都在时钟上升沿之后,与老化检测类似,都是后检测带(Detection Slick),检测窗口为TDS(即后检测带间隔)。对于一般的数字电路可以用这样的逻辑模型表示:组合逻辑的输入信号Si来自上一级触发器,输出So被后一级的触发器捕获,触发器间使用同步时钟,周期为T。

对于软错误、老化延迟和延迟故障,一般在保护带预测老化延迟,在后检测带检测延迟故障,如图1所示。用上述信号模型分别对软错误、老化延迟和延迟故障的故障行为进行了分析:(1)延迟故障。延迟的So会在TDS期间发生SV,但没有在TGB期间发生的跳变。延迟故障还会在时钟周期的后端导致So的TVV故障,TVV会在下一个时钟周期引起下一级逻辑发生IVV故障。因此,对于延迟故障来说,SV、TVV和IVV是等效的。(2)老化延迟。延迟的So在TGB期间将会导致SV。但老化延迟不会导致TVV或IVV。(3)SEU。发生SEU的触发器,其输出端Si会发生的是SV,之后Si将保持稳定。因此,SV可能会导致下一级触发器捕获到错误的数据,继而导致发生TVV以及下一级触发器Si发生IVV,即SEU将表现为SV、IVV或TVV。(4)SET。对于宽度<TDS+TGB的SET故障,其行为与普通的延迟故障相似。因此,对于SET来说,SV、IVV和TVV也是等效的。

图1 保护带和后检测带

综合上述分析,结论如下:对于上述引起电路时序发生错误、时序违规的各种故障行为都可以统一为SV,即统一故障模型。

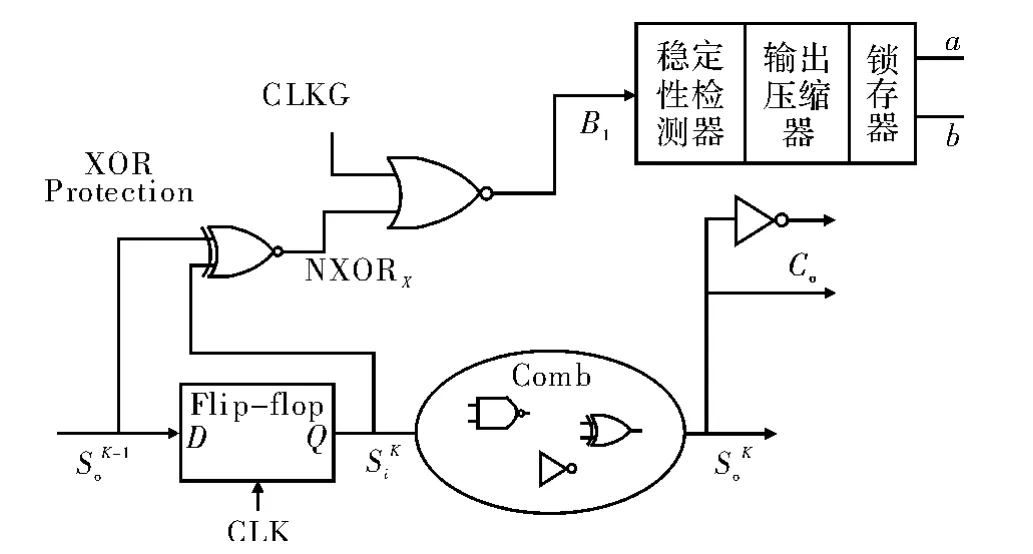

统一故障检测中最重要的单元是信号稳定性检测单元。图2显示了SVFD在电路中的位置及其主要结构。通过插入检测单元的一个关键路径末端,触发器采用XOR保护检测,通过将触发器输入端和输出端两路信号送入一个同或门NXORX。当CLKG低电平期间触发器受到SEU时,其会在或非门B1输出高电平,导致X节点放电。

图2 统一故障检测在电路中的位置和结构

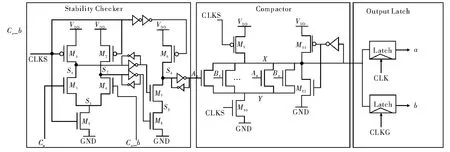

检测电路由3部分组成:稳定性检测器(Stability Checker,SC)、输出压缩器(Compactor)和输出锁存器(Output Latch)。稳定性检测器的基本结构来自于在线老化预测,与之类似,稳定性检测器也是通过比较一对预充电的节点状态来判断被检测信号上是否发生SV。下面分析SVFD的工作原理。

如图3所示,稳定性检测器是通过对动态节点S1和S2状态的监测来控制节点S4的状态,判断电路是否发生故障。然后把信号输出给输出压缩器用于判断故障类型。当经过预充电阶段后,S1与S2均处于高电平,电路进入检测状态。当组合逻辑输出的信号Co正常时,M3和M4的栅极状态总是互斥的,即为“0”、“1”或“1”、“0”,S1与S2其中必有一个发生放电。这种情况下,节点S4会稳定在高电平,稳定性检测器的输出A1为0,SV没有发生。与之相反,当Co在在保护区间发生SV,这时原本保持在高电平状态的节点发生放电,即S1和S2均处于低电平状态,从而打开节点S4的下拉网络,稳定性检测器的输出A1由0变成1。输出压缩器捕获到A1信号,从而释放节点X的电荷。与节点X相连的两个锁存器分别在不同时钟CLK和CLK锁存X的值,根据两个锁存器输出a,b的值来判断具体故障类型。

图3 故障检测单元的晶体管实现

文献[2]在面积开销、功耗、以及故障检测能力等方面都进行了分析,发现SVFD对于有时序违规引起的电路故障有着较好的检测结构。然后,它也存在着明显的缺点:(1)需要额外的控制信号。与其他检测结构相比,需要额外的控制信号才能保证SVFD的正常工作,而引入一路控制信号必然增加它的面积开销。(2)不适用于高速电路。在SVFD结构中,大量的保护器被用来保护动态节点高状态的稳定性,这会导致节点充放电时间的增加,使其不适用高速电路。

2 高速信号违规检测结构

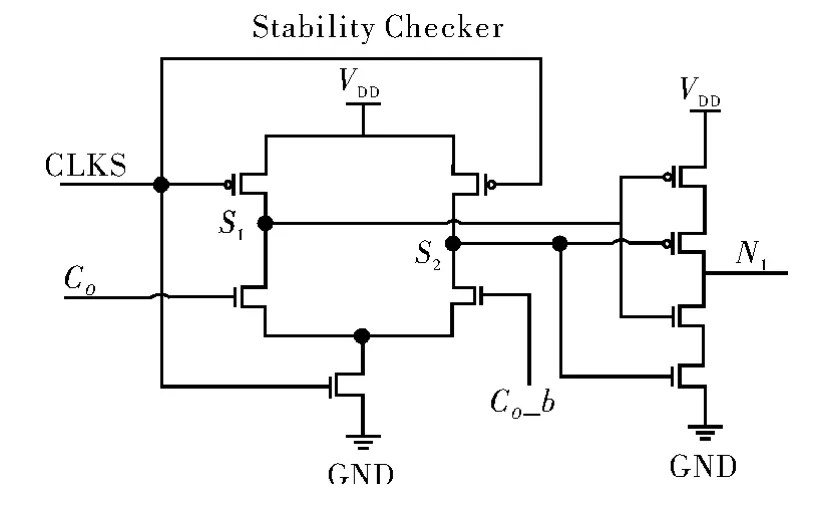

考虑上述原因,针对SVFD的稳定性检测器是影响电路在高速电路中运用的主要障碍。根据这个分析,论文提出了一种高速信号违规检测结构(Highspeed Signal Violation Detector,HSVD),如图4所示。

图4 HSVD中SC的电路结构

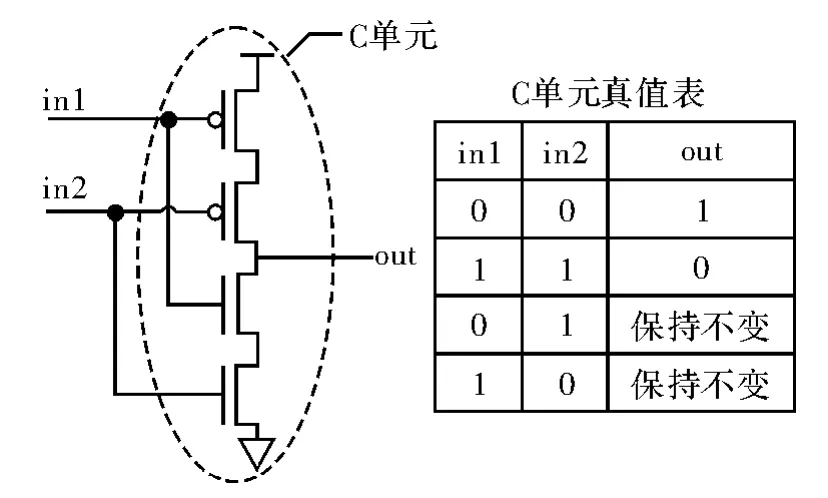

新的稳定性检测器(Stability Checker,SC)在保留原先结构的基础上,最大的改动是引进了被用于软错误防护时序单元中使用的Muller C单元(简称C单元)[6]。图5给出了C单元以及对应的真值表。这样就减少了SC中动态节点和补偿动态节点“弱”逻辑所需的保持器的数量,大幅减少了检测单元的硬件开销。不仅如此,C单元所具有的保持功能加强了SC输出的N1信号的保持时间,还提高了输出压缩器中X节点的电荷释放时间,从而避免在高速电路中因X节点放电不足而可能造成的电路检测失效。这种改进大幅提高了HSVD对高速电路的适应能力。

图5 C单元及其真值表

3 仿真与对比

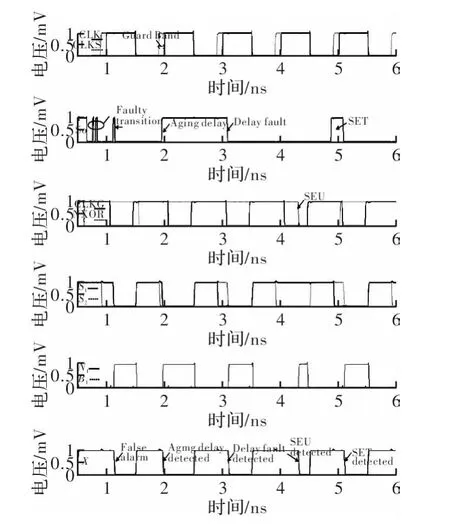

为验证HSVD的功能,对单个检测单元进行了晶体管级的Hspice故障模拟仿真。图6是使用32 nm PTM工艺模型[7],对HSVD中几个关键节点状态在5个周期中变化的仿真波形图。其中系统主时钟信号为CLK,CLKS为控制预测时钟,So是组合逻辑输出信号,CLKG为保持时间的控制信号,NXOR是XOR保护的输出信号;在第4个波形图中,显示了SC内部节点S1和S2随着上述信号变化而出现的状态变化图形;第5个波形显示的是SC输出信号N1以及XOR保护的输出信号,从图中可以看出,N1信号具有较好的保持性,N1和B1是输出压缩器的输入信号;最后一个图显示了最终的检测结果,从中可以看出结果对故障的识别。

图6 Hspice仿真波形图

与其它方案的比较:将HSVD与其他几种方案进行比较。表1列出了与老化预测策略(Aging Resistant Stability Checker,ARSC)[8]以及SVFD在晶体管数目、时钟信号数量以及检测完备性上的比较结果。面积开销可以利用晶体管数目来估算。可以看出新结构对比传统ARSC具备明显的性能优势,而增加的开销微小。与原先的SVFD相比,HSVD的硬件开销更少。

表1 与其它方案的比较

4 结束语

相对于目标故障检测,多故障统一检测具有明显的应用价值。通过对SV的分析,提出一种适合高速电路的多故障统一检测策略HSVD,给出了其电路实现。在HSVD的稳定性检测器中,C单元的使用使HSVD更适用于高速芯片。Hspice仿真验证其功能有效,与已有的机制方案相比也具有面积和功耗的优势。

[1]YAN Guihai,HAN Yinhe,LI Xiaowei.A unified online fault detection scheme via checking of stability violation[C].Soul:DATE,2009:395-400.

[2]NICOLAIDIS M.Design for soft error mitigation[J].IEEE Transaction on Device Mater.Reliab,2005(5):405-418.

[3]SHIVAKUMAR P,KISTLER M,KECKLER S W,et al.Modeling the effect of technology trends on the soft error rate of combinationallogic[C].in Proc.International Conference Depend System Network(DSN),2002:389-398.

[4]VAZQUEZ J C,CHAMPAC V,ZIESEMER A M,et al.Built-in aging monitoring for safety-critical applications[C].Washington D C:Proc.IEEE Int.On-Line Test Symp.(IOLTS).IEEE Computer Society Press,2009:9-14.

[5]NICOLAIDIS M.Time redundancy based soft-error tolerance to rescue nanometer technologies[C].San Diego:Proceedings of the 17th VLSI Test Symposium,1999:86-94.

[6]YU Cao,WEI Zhao.Predictive Technology Model(PTM)[C].Nano-Networks and Workshops,2006.NanoNet'06.1st International Conference on,2006:1-5.

[7]AGARWAL M,PAUL B C,ZHANG MING,et al.Circuit failure prediction and its application to transistor aging[C].Washington D C:Proc.of Very Large Scale Integration Test Symposium,IEEE Computer Society Press,2007:277-286.