低功耗0.18 μm 10 Gbit/s CMOS 1∶4分接器设计

2013-03-22潘敏冯军

潘 敏 冯 军

(1东南大学射频与光电集成电路研究所,南京 210096)

(2合肥工业大学计算机与信息学院,合肥 230001)

随着社会的发展,信息交换量与日俱增,光纤通信技术已成为目前信息高速公路的主体.分接器可将信道中传输的串行高速信号还原为并行的多路低速信号,是光接收机以及SerDes接收机等系统中的核心模块.近年来,随着绿色环保节能意识的不断加强,降低功耗成为电路设计中一个明确的重要任务.

目前,国内外10 Gbit/s以上的分接器大都采用SiGe[1],InP[2-3]等工艺,但是这些工艺制造费用普遍较高,不易代工,且设计出的电路功耗较大.而互补金属氧化物半导体(CMOS)工艺具有成本低、集成度高、工艺容易获得等诸多优点.随着CMOS工艺的不断进步,其特征频率fT越来越高,可实现电路的工作速率也日益提高,采用不同CMOS工艺实现的高速超高速分接器不断涌现[4-10].其中多数采用的是CML(current-mode logic)电路[4-9];文献[4]甚至采用了低工艺的超高速设计,以说明CML电路的高速工作特性,但此设计只是以功耗换取速率.虽然也有少数电路使用了CMOS逻辑电路,但均工作在较低的速率级别[8-10],因为设计者认为CMOS逻辑电路的工作速率一般低于fT/20[11](采用0.18 μm CMOS工艺时fT大约50 GHz).如何在提高速率的同时降低功耗是分接器研究的一个热点问题.

本文基于已在低工艺设计中使用并证实的设计理念[12],采用全CMOS逻辑电路设计实现了一种10 Gbit/s分接器,以减小功耗和芯片面积,且输出的满摆幅还可以提供大的噪声裕度,省掉在系统集成中与后续低速数字电路间的电平转换电路,实现无缝对接.

1 1∶4分接器的系统结构

1.1 基本结构选择

分接器一般采用串行、并行、树型3种基本结构[13].串行结构的优点在于原理和结构简单,缺点是处理速度受限,功耗高;并行结构的优点在于工作速率高、功耗低,缺点是所需时钟相位复杂,高阶的分接系统难以实现;树型结构的优点在于电路可以分级设计,只有第1级工作在最高速率上,且可对高低速模块分别进行速度和功耗上的优化,从而得到低功耗和高速率间的最佳权衡.鉴于本文以低功耗和高速率为主要设计目标,因此设计的10 Gbit/s 1∶4分接器系统结构采用树型结构(见图1).

图1 1∶4分接器系统结构

由图1可知,整个1∶4分接器由数据通道和时钟通道组成,其中数据通道由3个1∶2分接单元以及缓冲电路构成.一路速率为10 Gbit/s的输入数据信号通过输入缓冲进入高速分接单元,分接成2路速率为5 Gbit/s的信号,然后经过2个低速分接单元和输出缓冲,得到4路速率为2.5 Gbit/s的信号输出.时钟通道由2分频器和缓冲电路组成,频率为5 GHz的输入时钟经过缓冲电路,一路送入高速分接单元,另一路送入2分频器,得到频率为2.5 GHz的时钟信号,并送入低速分接单元.

1.2 半速率1∶2分接器

图1中的1∶2分接单元采用半速率1∶2分接器,其结构见图2.这种结构由5个锁存器构成,其中下面2个锁存器构成主-从D触发器,该触发器在时钟下降沿采样,然后在时钟上升沿输出.上面3个锁存器构成主-从-从D 触发器,该触发器在时钟上升沿采样,然后在时钟下降沿输出.当时钟频率等于输入数据速率的一半时,可将输入数据的相邻比特分接到上下2路触发器中,并且在时钟的上升沿同步输出.这种结构所需时钟的速率是输入数据比特率的一半,降低了时钟通道的设计难度,同时也降低了功耗.

图2 半速率1∶2分接器结构

2 电路设计

2.1 锁存器电路选择

分接器电路设计中,1∶2分接器和2分频器是其核心模块,2分频器采用由触发器构成的数字分频器结构,故锁存器是分接器模块和分频器模块中的基本单元,设计的好坏直接影响整个分接电路的性能,其速度决定了分接器的最大工作速率.在传统的高速分接器设计中,一般采用CML锁存器.CML电路具有全差分电路的所有优点,并能工作至高速率;但因其电源提供的是恒定电流,电路功耗尤其是低速电路的功耗不易降低,且结构复杂,需要晶体管的数目多,芯片面积大[4-6],故在改进的CML电路中,应采用减小尾电流源的电流、去除尾电流源以及分时提供电流的方法来减小功耗[7-9].另外,在部分高速芯片研究中,高速部分采用CML电路或其改进电路来实现,低速单元则采用CMOS 逻辑电路来实现;高、低速单元采用不同的设计,其间必须增加缓冲以及电平转换电路[8-9].因此,本文采用全CMOS逻辑电路设计来实现高速分接器,充分发挥CMOS逻辑电路的优点,使得实现的电路结构简单、功耗低、芯片面积小.

2.2 动态CMOS逻辑电路

动态CMOS逻辑电路是指依赖于将信号值暂时存储在电路的高阻抗节点电容上的电路.电路结构比较简单,具有较高的开关速度和较低的功耗,实现电路的芯片面积较小.动态CMOS逻辑锁存器电路由一个传输门和一个反相器构成(见图3).图中,Cp由晶体管寄生电容组成,主要包括传输门的结电容和反相器的输入电容.当CK为高电平时,传输门打开,输入信号被反相输出;当CK为低电平时,传输门关断,之前采样的信号就被保存在节点A的寄生电容Cp上.Cp上的电荷在传输门关断时会因为电荷泄漏等原因丢失,造成误码.因此,对于这样的动态锁存器,存储节点A必须周期性地刷新.

图3 动态CMOS逻辑锁存器

本文采用仿真软件Candence来验证动态CMOS逻辑锁存器能否满足设计速率要求.由于仿真时必须留有一定的裕量,故电路工作速率设定为6和2 Gbit/s.采用0.18 μm CMOS工艺设计的动态CMOS锁存器分别工作在6和2 Gbit/s速率上的仿真结果见图4和图5.由图可知,锁存器输出逻辑正确,输出波形满摆幅.因此,在数据通路中,电路的刷新频率不是问题,电路设计采用动态CMOS逻辑锁存器结构是完全可行的.同时,动态CMOS逻辑锁存器与传统的CML锁存器相比,优点显而易见:① 电路不采用恒定电流源;② 没有静态功耗;③ 仅需4只晶体管,较传统的CML锁存器至少减少了3只晶体管.这些优点都有利于实现电路的高性能和低功耗.

图4 锁存器工作速率为6 Gbit/s时的仿真波形

图5 锁存器工作速率为2 Gbit/s时的仿真波形

在动态CMOS逻辑锁存器中,还有一个需要特别注意的问题是时钟重叠.由动态CMOS逻辑锁存器实现的D触发器结构见图6.考虑如图7所示的时钟波形,在CK和CKn同时为0的重叠期间,TG1的PMOS晶体管和TG2的PMOS晶体管同时导通,形成了从输入数据d到输出数据q的直接通路.如果0重叠的时间太长,则输出数据q很有可能在时钟下降沿时便跟随输入数据d翻转.对于如图7所示的正沿触发器而言,显然这是不希望出现的效应.同理,在CK和CKn同时为1的重叠期间也会产生类似情况.因此,对于由动态CMOS逻辑锁存器构成的触发器,时钟重叠是应该避免的.

图6 动态CMOS D触发器

图7 重叠时钟的波形

2.3 时钟缓冲电路设计

在1∶4分接器中,2分频器输出的是单端信号,而1∶2分接单元需要的是差分时钟信号.因此,采用如图8所示的时钟缓冲电路,不但可以获得差分时钟信号,还可以避免时钟重叠问题.此电路以信号通过传输门TG的时间来等效反相器Inv1的延迟时间,从而提供互补的时钟信号.图8虚框内的2个反相器形成正反馈,以提高输出信号的转换速度,同时保证时钟信号的占空比为50%.

图8 CMOS时钟缓冲电路

3 芯片测试结果

分接器芯片采用0.18 μm CMOS工艺加工实现.芯片面积为0.475 mm×0.475 mm,芯片照片见图9.

图9 1∶4分接器芯片照片

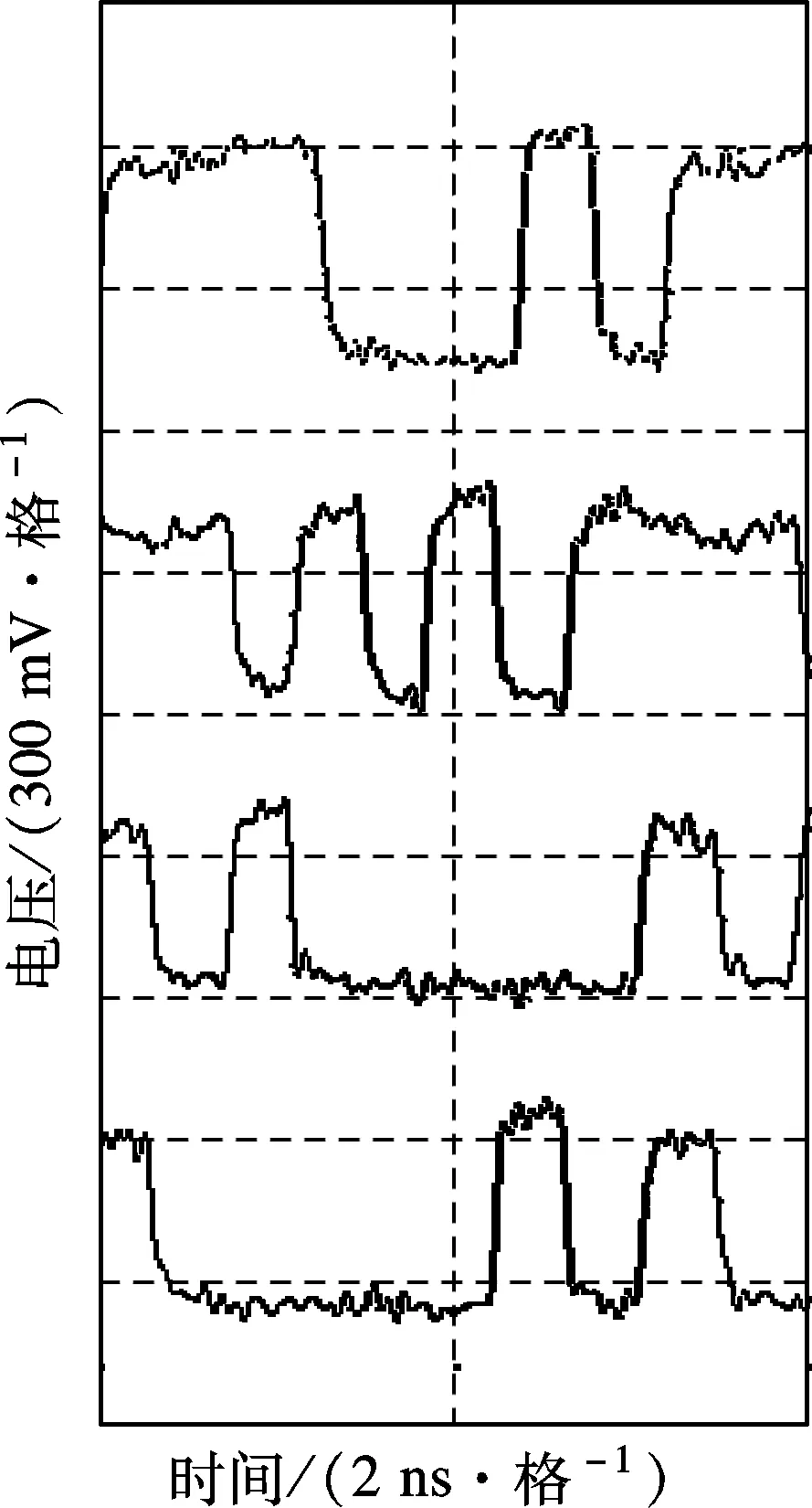

采用Cascade Microtech探针测试台、Adventest D3186脉冲信号发生器以及Tektronix MS071254C示波器对芯片进行了测试.当输入速率为10 Gbit/s的数据0100 0000 0100 1001 0100 1111时,测试输出的4路速率为2.5 Gbit/s的数据的逻辑波形见图10.由图可知,输出信号逻辑正确.2分频器的最高工作频率可达5.6 GHz,其输出频率为2.8 GHz,输出波形见图11,此图采用无限叠加眼图模式输出.输入速率为10 Gbit/s、长度为231-1的伪随机数据时,分接器输出的一路速率为2.5 Gbit/s的数据眼图见图12.测试芯片在1.8 V的电源电压下,输出信号的摆幅为400 mV,芯片整体功耗为48.6 mW,不包含输出缓冲的核心功耗仅为25 mW.

文献[4-6,8]中CMOS工艺1∶4分接器与本文分接器的综合比较结果见表1.表中功耗是指输出信号摆幅为400 mV时得到的芯片整体功耗.由表可知,采用动态CMOS逻辑实现的分接器在芯片面积和功耗等性能指标上具有一定的优势.

图10 10 Gbit/s速率下的输出逻辑波形

图11 输入频率为5.6 GHz时的时钟分频器输出波形

图12 10 Gbit/s速率下的输出信号眼图

表1 1∶4分接器性能

4 结语

本文采用0.18 μm CMOS工艺设计实现了一种低功耗全CMOS逻辑的10 Gbit/s 1∶4分接器.分接器采用半速率树型结构,锁存器采用动态CMOS逻辑电路,很大程度上降低了功耗,减小了芯片面积,验证了低功耗CMOS逻辑电路在速率为10 Gbit/s的高速分接器设计中的应用,大大提高了芯片设计的性价比,为今后低功耗高速电路设计积累了经验,具有广泛的产业化应用前景.

)

[1]王贵,王志功,李伟,等.基于锗硅工艺的40-Gbit/s分接器[J].固体电子学研究与进展,2009,29(2):276-280.

Wang Gui, Wang Zhigong, Li Wei, et al. 40-Gbit/s demultiplexer based on SiGe process [J].Research&ProgressofSolidStateElectronics, 2009,29(2): 276-280. (in Chinese)

[2]Makon R E, Driad R, Losch R, et al. InP DHBT-based 1∶2 DEMUX IC operating at up to 120 Gbit/s [J].ElectronicsLetters, 2009,45(25): 1340-1342.

[3]Sano K, Murata K, Kitabayash H, et al. 50-Gbit/s InP HEMT 4∶1 multiplexer/1∶4 demultiplexer chip set with a multiphase clock architecture [J].IEEETransactionsonMicrowaveTheoryandTechniques, 2003,57(12): 2548-2554.

[4]王贵,王志功,朱恩,等. 12-Gbit/s 0.25-μm CMOS 1∶4 分接器[J]. 电路与系统学报,2006, 11(2): 133-135.

Wang Gui, Wang Zhigong, Zhu En, et al. 12-Gbit/s 1∶4 demultiplexer in 0.25-μm CMOS[J].JournalofCircuitsandSystems, 2006,11(2): 133-135. (in Chinese)

[5]徐阳,冯军. 0.18μm CMOS 10 Gbit/s 分接器设计[J]. 电子工程师,2004,30(3):5-9.

Xu Yang, Feng Jun. Design of 10Gbit/s demultiplexer in 0.18μm CMOS [J].ElectronicEngineer, 2004,30(3): 5-9. (in Chinese)

[6]Kim B G, Kim L S, Byun S, et al. A 20 Gbit/s 1∶4 DEMUX without inductors and low-power divider-by-2 circuit in 0.13 μm CMOS [J].IEEEJournalofSolid-StateCircuits, 2008,43(2): 541-549.

[7]Mineyamal A, Suzuki T, Ito H, et al. A 20 Gbit/s 1∶4 DEMUX with near-rail-to-rail logic swing in 90 nm CMOS process[C]//Proceedingsof2009IEEEMTT-SInternationalMicrowaveWorkshopSeriesonSignalIntegrityandHigh-SpeedInterconnects. Guadalajara, Mexico, 2009: 119-122.

[8]Jiang Junjie,Feng Jun. A kind of low-power 10 Gbit/s CMOS 1∶4 demultiplexer[J].JournalofSoutheastUniversity:EnglishEdition, 2006,22(1): 1-4.

[9]Xie Feng,Xu Yanyi. Design of low voltage ultra high-speed 1∶16 DEMUX by 0.18 μm CMOS process[C]//Proceedingsofthe2ndInternationalConferenceonFutureComputerandCommunication. Wuhan, China, 2010: 36-39.

[10]Tanga X S, Wang X J,Zhang S Y, et al. A 2-Gbit/s 1∶16 Demultiplexer in 0.18 μm CMOS process[C]//Proceedingsof2008GlobalSymposiumonMillimeterWaves. Nanjing, China, 2008: 98-100.

[11]Utku S, Chih K K Y. A comprehensive delay model for CMOS CML circuits [J].IEEETransitionsinCircuitsandSystems, 2008,55(9): 2608-2618.

[12]Li Yujun, Feng Jun. A 3.6 Gbit/s 60 mW 4∶1 multiplexer in 0.35-μm CMOS[C]//ProceedingsofInternationalSymposiumonSignals,SystemsandElectronics. Nanjing, China, 2010: 1-3.

[13]王志功. 光纤通信集成电路设计[M]. 北京:高等教育出版社,2003: 253-258.