一种UFH频段RFID读写器的硬件设计与实现

2013-03-11何滔

何滔

(云南能源职业技术学院,云南 曲靖655001)

射频识别(RFID)技术凭借其远距离的可读取性、快速的识别性、大容量的资料存储能力,已经越来越受到人们的关注。在国外,零售业、交通系统、物流管理以及个人身份管理是其最为主要的应用范畴;而国内RFID市场虽然才起步,但在居民身份证、公交售票、高速公路收费和校园管理等方面已经取得了长足的进展,RFID已经开始逐步深入到我们生活的各个方面。本文针对RFID的一些硬件模块,设计了相应的接口电路,组合成一个实用的基于ARM的RFID读写器[1-3]。

1 总体方案

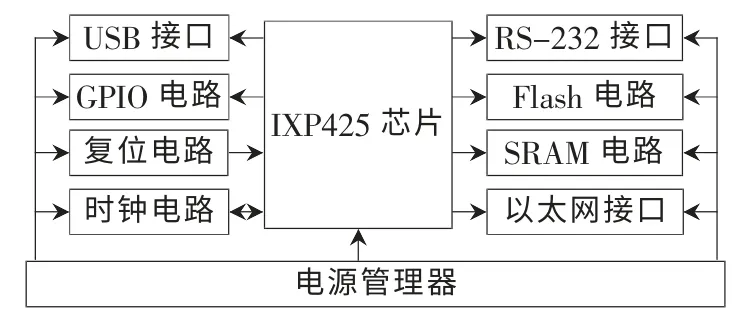

整个系统采用模块化设计,每个模块采用集成度高、功能独立的芯片,并配上一定的外围电路。系统主要分为基于IXP425控制器的主控模块、通信接口(包括以太网、串口和USB接口,电源管理)、具备基带信号调制解调的射频信号采集处理板以及功率放大模块组成,如图1所示。

目前,嵌入式处理器的种类很多,常见的32 bit嵌入式处理器有ARM、PowerPC、Co1dFire等。与其他嵌入式处理器相比,ARM具有体积小、功耗低、成本低、性能高的优点,并提供丰富的片内外围控制电路。设计采用ATMEL公司的AT91SAM7S64微处理器。

图1 高频读写器结构框图

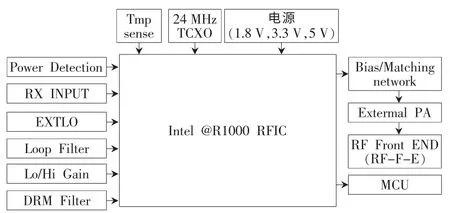

射频模块采用Intel R1000收发器。内含能源扩大器,可在近距离或者2 m内对标签进行编码和阅读,而具体距离由读写器所使用的天线决定。使用R1000读写器的读写范围可以达到10 m。R1000与单独的微处理器连接,这个微处理器可以把由R1000数字信息处理器产生的原始数据转换成EPc或者18000-6c格式的代码,其工作频率为860 MHz~960 MHz,共有56个引脚,采用0.18μm SiGe BiCMOS先进工艺,面积仅为8 mm×8 mm,功耗只有1.5 W左右,具有很高的集成度。此芯片既可降低设计中的复杂性和生产成本,又能使制造商制造出体积更小,更有创新性的读写器,从而开拓新的RFID应用领域。

2 硬件设计与实现

2.1 基于IXP425控制器的主控制部分

普通阅读器在处理由阅读器访问电子标签获得的原始RFID数据时,通常通过阅读器上的通信接口将该信号送到上层具有中间件的上位机中,这样的处理方式增加了设备集成费用,降低了系统集成度。在此设计中设计一块嵌入式微处理器来替代上位机,将图2所示的中间件和应用进程装到此板子中,只要设计的微处理器系统中嵌入式CPU配置达到ARM9的标准,就能达到运行的要求。

图2 系统软件结构框图

此电路板主要由IXP425芯片、时钟电路、复位电路、SRAM存储电路、Flash存储电路、USB接口电路、串口电路、以太网电路、GPIO电路和电源管理电路组成,如图3所示。

图3 基于IXP425的电路结构框图

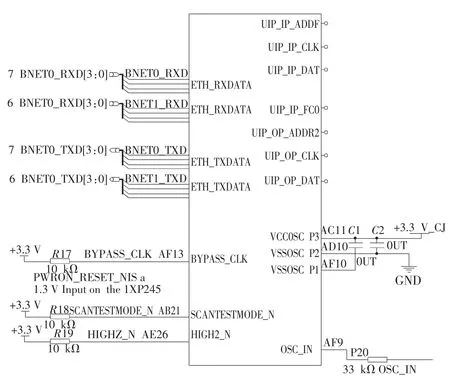

基于IXP425芯片实现ARM9功能电路,主要功能为通过外围条件的实现来处理外围提供的信号,或利用主芯片输出总线形式的信号给Flash或SRAM,其中它的工作必须留有晶振信号输入口,如图4所示。

图4 基于IXP425的电路原理图

2.2 基于ARM7的射频采集处理器部分

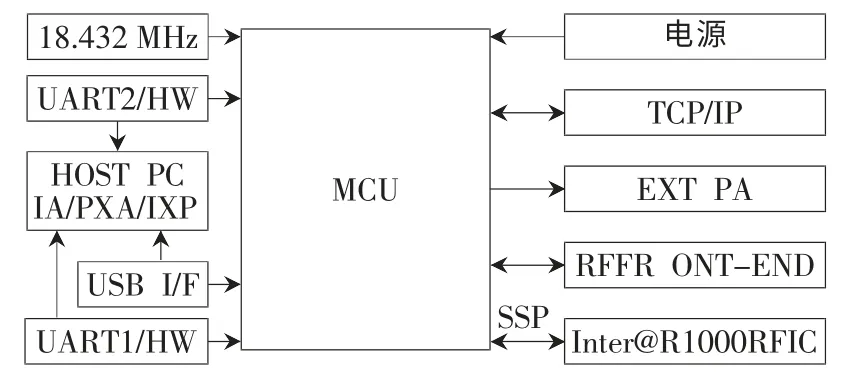

射频信号采集处理[4-6]采用基于ARM7的嵌入式系统进行处理,与主机之间的通信为串口和以太网接口,与射频芯片进行的数据交换可根据技术方案中采用的射频芯片具体信号灵活设定。基于ARM7的射频采集处理器结构框图如图5所示。

图5 基于ARM7的射频采集处理器结构框图

基于ARM7的MAC射频采集处理器是系统的核心部分,它负责接收用户命令、对发送信号进行收发控制,协议的所有命令集也将存储其中,支持ISO 18000-6C和EPCGen2协议,并完成以上协议的所有命令操作,定义标签各个状态,对所有信号(包括数据信号、命令信号)的收发控制,完成与上位机的通信控制,如RS-232、TCP/IP的通信,如图6所示。

图6 基于ARM7的射频采集处理器电路框图

基于R1000的射频信号收发部分是系统另外一个核心部分,它负责把天线接收的超高频UHF信号解调后送给主控制芯片,或者将主控制芯片的数据和命令调制后生成基带信号,结构如图7所示。

图7 基于R1000的射频信号收发电路结构框图

功率放大模块用于对发射信号进行功率放大,增加传输功率,经过功率放大后直接连接到环行器。

在天线前端AFE部分,天线作为信号从读写器到标签的收发端,直接与环行器相连。对Intel R1000超高频收发器,基于不同的天线子系统,天线有两种配置情况,即单天线模式和双天线模式。双天线模式采用分离的天线将接收器和发射器连接起来,通常情况下,两根独立的天线由一个开关控制,每根天线仅具备接收器功能或发射器功能。对单天线模式,因天线的反射系数并不理想,所以接收增益不能太大,会有饱和的问题。以R1000的高接收灵敏度,可以搭配-10 dB左右的耦合器,视整体线路的隔离而定;对于双天线模式,天线的收发隔离比较理想,接收路径可以使用高增益。

2.3 外置天线部分

设计的天线应满足以下要求:

(1)满足超高频UHF频段要求;

(2)近场、远场RFID操作可读取单品级标签;

(3)匹配超高频Gen2或ISO18000-6C RFID标签;

(4)高性能、低成本天线解决成本;

(5)适合桌面、壁挂安装。

3 多层PCB设计

基于ARM7的射频信号采集PCB板为4层板,顶层、底层为原件面和布线层,中间层为电源层和地层,材料为FR4,介电常数为4.7,尺寸为180 mm×90 mm。基于IXP425控制器的主控制PCB板为6层板,顶层、第3层、第4层、底层为原件面和布线层,第2层和第5层为电源层和地层,材料为FR4,介电常数为4.7,尺寸为250 mm×90 mm。板中有过孔和铜皮设计,过孔的设计是为了布线方便,铜皮的设计减小了信号干扰。

按本文所述的硬件结构设计方案,可实现一个工作频率为850 MHz~930 MHz的RFID读写器,在系统最大输出功率条件下,有效识读距离可达8 m。目前,RFID超高频技术的发展已比较成熟,也已经有了一些标准,标签的价格也有所下降,但RFID超高频读写器却有变得更大、更复杂和更昂贵的趋势,其消耗能量将更多,制造元件达数百个之多。然而,此次项目的设计采用高度集成的R1000芯片,希望能解决上述问题,既降低芯片设计中的复杂性和生产成本,又能制造出体积更小、更有创新性的读写器,从而开拓新的RFID应用领域。

[1]吴泽海,赖声礼,张建明,等.一种UHF频段RFID读写器的硬件设计与实现[J].电子技术应用,2005(1):50-52.

[2]江小平,李中捷,余晓峰.基于ARM的射频识别读卡器电路设计[J].信息与电子工程,2010,8(4):451-454.

[3]程小辉,魏力.低功耗RFID数据采集系统的优化[J].电子技术应用,2013,39(2):118-120.

[4]Texas Instruments.Multi-standard fully integrated 13.56-MHz radiof requency identification analog front end and data framing reader system[Z].2009.

[5]陈邦媛.射频通信电路[M].北京:科学出版社,2002.

[6]张玉兴.射频模拟电路与系统[M].成都:电子科技大学出版社,2008.