基于FPGA高速线阵CCD的驱动电路设计*

2013-02-21喻依虎孟丽娅岳陈平

喻依虎,孟丽娅,岳陈平

(重庆大学 光电技术及系统教育部重点实验室,重庆 40030)

线阵电荷耦合器件CCD(Charge Coupled Device)是一种以电荷信号为载体的图像传感器,能够把光学影像转化为电荷信号。线阵CCD的光敏像元紧密地排成一行,它具有传输速度快、密集度高与可靠性好等一系列优点,广泛应用于扫描仪、工业非接触尺寸的高速测量和大幅面高精度实物图像扫描等工业现场的检测、分析与分选领域[1]。其应用系统的关键技术在于CCD的驱动电路能否使其工作在最佳状态。

传统的驱动方法主要偏重于分立式电路的实现,调试比较困难,灵活性较差[2]。而单片机驱动方法虽然编程灵活,但是驱动频率比较低[2]。基于以上问题,本文以TCD1706D的线阵CCD为例,利用FPGA内部硬件资源的可编程性,设计一种高速线阵CCD的驱动电路[3-4]。通过对TCD1706D的驱动时序的分析,使用Verilog语言对电路进行设计,并利用Quartus II对所设计的电路进行时序仿真[5]。通过实验验证,该电路可以使TCD1706D在10 MHz的驱动频率下稳定工作。

1 TCD1706D工作原理

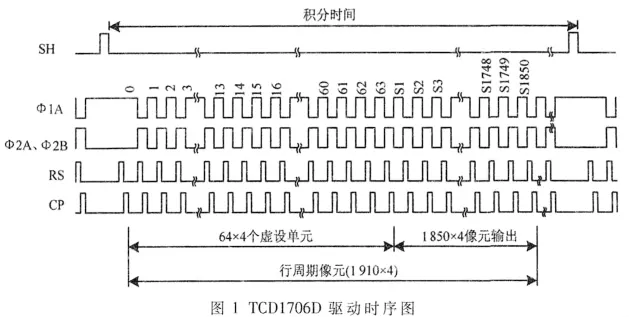

TCD1706D是一款高灵敏度、低暗电流的具有7 400个有效像元的线阵 CCD,像元大小为 4.7 μm×4.7 μm,中心距为 4.7 μm,阵列长度为 34.8 mm,4路并行输出,最高工作频率为25 MHz。其驱动时序图如图1所示。

TCD1706D的驱动时序由SH转移脉冲信号、Φ1A/Φ2A/Φ2B移位脉冲信号、CP钳位脉冲信号和 RS复位脉冲信号6路脉冲信号组成。当SH为高电平时,感光阵列与移位寄存器之间导通,光敏区存储的信号电荷就转移到对应的移位存储器中;当SH为低电平时, 信号电荷在 Φ1A/Φ2A/Φ2B移位脉冲信号的作用下,依次从4路输出端口输出电荷。由图1可知,该CCD首先输出64个虚设单元的信号电荷,然后输出1 850个有效信号电荷,因此,在积分时间内,移位脉冲信号的个数必须大于1 910个。

2 TCD1706D驱动时序的分析

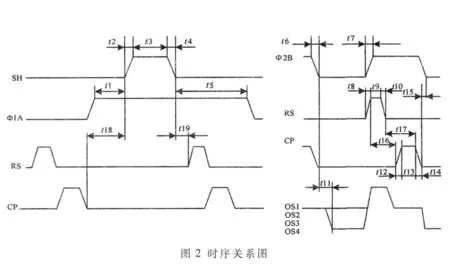

为了使线阵CCD工作在最佳状态,6路脉冲信号之间需要满足一定的关系。各时序间关系图如图2所示。

在转移信号SH为高平之前,移位信号Φ1A至少提前t1时间输出高电平,钳位脉冲CP下降沿与SH上升沿时间间隔为t18。当SH变为低电平时,移位信号Φ1A需要延时 t5输出频率为 10 MHz、占空比为50%的脉冲信号。复位脉冲RS与钳位脉冲CP是频率相同相位不同的脉冲波,其中RS下降沿与CP下降沿的时间间隔为t17。钳位脉冲CP的下降沿比SH的上升沿超前t18,复位脉冲RS的上升沿比SH下降沿滞后t19。移位信号Φ1A与Φ2A、Φ2B频率相同,相位相反。在移位信号φ2B的高电平中必须包含一个复位脉冲RS与一个钳位脉冲CP。各时间关系如表1所示。

3 驱动时序的设计

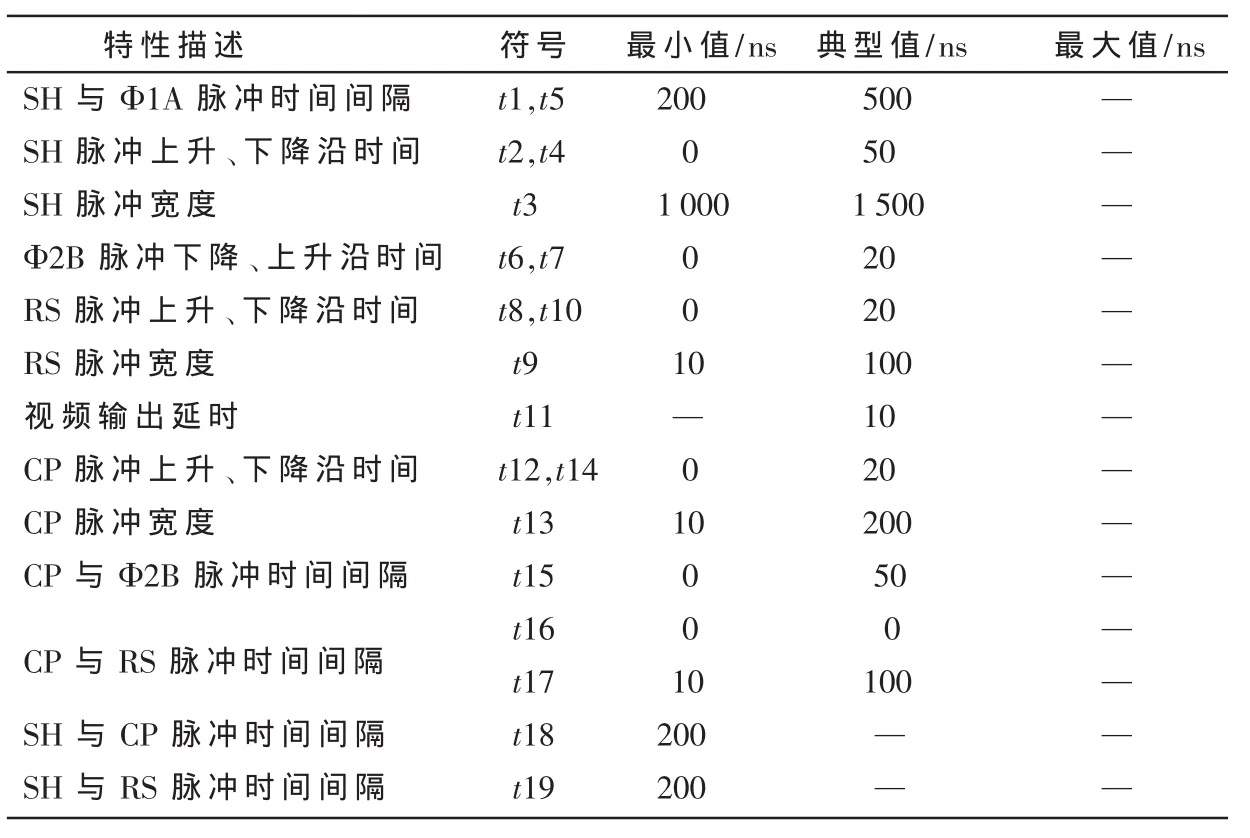

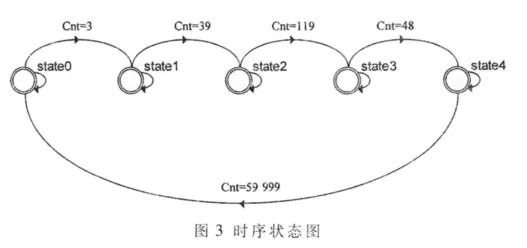

为了满足CCD驱动时序的要求,采用了Altera公司的EP2C8Q208C8N芯片作为时序发生器。其外部的晶振频率为50 MHz。为了满足CCD的10 MHz工作频率,利用Quartus II软件自带的锁相环PLL IP核生成80 MHz用于产生CCD驱动时序的系统频率。通过一个Moore有限状态机来实现6路信号的输出,其时序状态图如图3所示。

表1 时间关系表

将6路信号的时序关系分为5个阶段:Cnt=3即移位脉冲Φ1A先输出半个时钟周期;Cnt=39即t1为500 ns;Cnt=119即SH的脉冲宽度t3为1 500 ns;Cnt=48即t5为600 ns;Cnt=59 999,即设置光积分时间为 750 μs。

转移信号SH在状态state2输出高电平,其他状态输出低电平。位移信号Φ1A在状态 state1、state2、state3输出高电平,在状态state4输出频率为10 MHz、占空比为50%的方波信号,从而实现了其上升沿超前转移信号SH的上升沿 500 ns,下降沿滞后转移信号SH的下降沿600 ns。对位移信号Φ1A取反即得到位移信号Φ2A、位移信号 Φ2B。

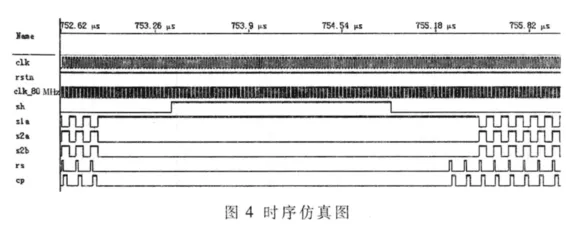

由图2可知,复位信号RS的上升沿滞后转移信号SH的下降沿 t19。故在 state3中,当计数器 Cnt为 32~33及40~41之间,复位信号 RS输出高电平;Cnt为 33~35及41~42之间,钳位信号 CP输出高电平,这样 CP滞后RS 12.5 ns。在状态state4中,当位移信号Φ2B的上升沿到来时,计数器在计数值为0~1内复位脉冲RS输出高电平,在1~3内钳位脉冲CP输出高电平。其他状态下,RS与CP都输出低电平。其在Quartus II环境下的仿真结果如图4所示。

图 4中,clk为 50 MHz外部时钟,clk_80 MHz为锁相环 PLL IP核生成 80 MHz时钟,s1a、s2a、s2b分别代表移位脉冲信号Φ1A、Φ2A、Φ2B。从仿真结果可知,FPGA产生的驱动脉冲满足TCD1706D对驱动脉冲的时序要求。由于FPGA的输出电平为3.3 V,而TCD1706D的驱动脉冲为5 V电平,所以在EP2C8Q208C8N与CCD之间加上一个74HC04反向器作为电平转换,以提高脉冲信号的驱动能力。

4 实验结果

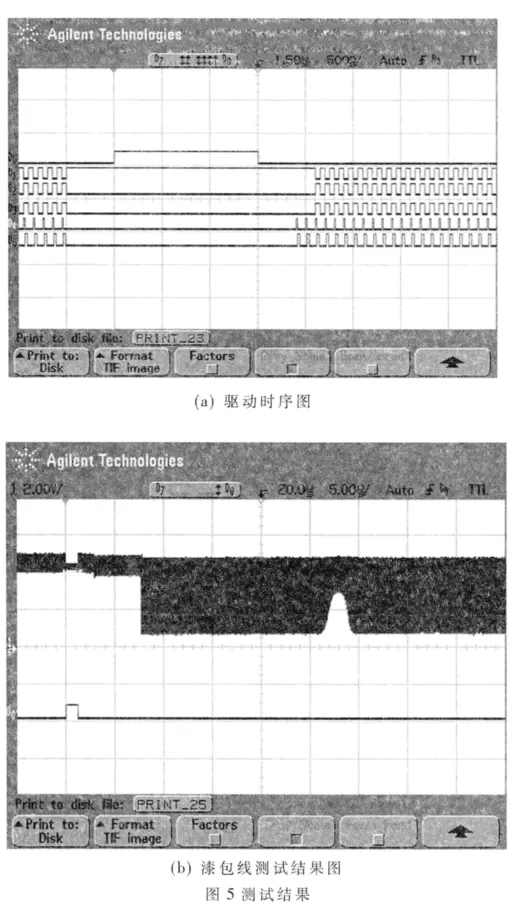

在日光灯的照射下,通过Agilent 54622D示波器观察所设计的驱动信号波形,如图 5(a)所示。D0~D5分别代表转移脉冲SH、移位脉冲 Φ1A、Φ2A、Φ2B、复位脉冲RS和钳位脉冲CP,6路输出信号与仿真结果一致,严格遵守了各个时序之间的相位关系。在CCD的表面放置一个直径为0.16 mm的漆包线,用示波器观察到的漆包线成像的波形图如图5(b)所示,图中凹下去的部分反映了漆包线的大小。

线阵CCD正常工作的关键在于各驱动时序间保持一定的相位关系。本文利用FPGA对线阵CCD TCD1706D的驱动时序进行设计。该设计利用Quartus II软件自带的锁相环PLL IP核可以生成时钟频率作为CCD的驱动时序产生的系统时钟频率,使电路具有集成度高、速度快、可靠性好、编程灵活等特点。实验证明,TCD1706D在10 MHz的频率下能够正常工作,达到了设计要求。

[1]王庆有.光电传感器应用技术[M].北京:机械工业出版社,2007.

[2]虞益挺,饶伏波,乔大勇,等.一种新型 CCD驱动电路设计方法[J].传感技术学报,2005,18(2):388-390.

[3]BJASLER J.A Verilog HDL primer[M].Pennsylvania:Star Galaxy Publishing,2008.

[4]曾立,邢廷文.基于 FPGA的线阵CCD的数据获取系统的 实 现[J].微 计 算 机 信 息 ,2010,26(4-2):132-133.

[5]崔岩,吴国兴,殷美琳,等.基于 FPGA的线阵 CCD驱动设计[J].现 代 电 子 技 术 ,2011,34(10):206-210.