基于移相技术的脉冲宽度精确测量方法及FPGA实现

2012-12-12仵晓辉师廷伟金长江

仵晓辉,师廷伟,金长江

(中国电子科技集团公司第二十七研究所,河南郑州450047)

在工程应用中,经常需要对数字信号的脉冲宽度进行测量,笔者在工作中就需要对由光信号转换过来的电信号的脉冲宽度进行测量。为了更好地满足工程应用的需求,就需要提高测量的精度。本文正是为满足这一需求而设计出了一种基于FPGA的脉冲宽度的精确测量方法。

1 测量方法的原理

测量脉冲宽度最常用的方法是脉冲计数法。脉冲计数法就是在待测脉冲宽度内对时钟脉冲进行计数(一般是对时钟脉冲的上升沿计数,下面以对上升沿进行计数为例),计数值N与时钟周期T相乘就可以得到脉冲宽度的数值。这是比较简单和常用的测量脉冲宽度的方法,这一方法的误差来源于待测脉冲的前沿和后沿与相邻时钟上升沿的时间差t1,t2,最大误差为一个时钟周期的值,如时钟频率为100MHz,则最大误差为10ns。测量原理见图1。

图1 脉冲计数法测量原理图

如果要提高计时精度,就需要提高时钟频率,而时钟频率的提高又受制于器件性能,并给印制板设计及加工带来一定困难,如果要得到纳秒量级的测量精度,时钟频率就需要达到1GHz,这在实际工程中应用起来比较困难。本文在脉冲计数法的基础上,提出运用数字移相技术并结合FPGA设计出新型的脉冲宽度测量方法,可将测量精度提高到纳秒量级。移相即通过FPGA内部锁相环模块(PLL)的延时功能,使时钟信号产生一定时间的滞后,新产生的信号与原始信号形成两路同频却有一定相位差的时钟信号,所以称为移相[1,2]。

测量原理见图2。通过移相技术对时钟信号CLK0进行处理,依次移相90°,形成另外三路时钟信号CLK90、CLK180和CLK270。分别使用以上四路时钟信号驱动四路计数器对待测脉冲进行测量[3,4]。假设时钟信号CLK0的频率为f,其周期则为T=1/f,四路时钟对待测脉冲信号测量的计数值分别为N1、N2、N3、N4,则最后待测脉冲信号的测量值为

图2 数字移相法测量原理图

通过式(1)和图2可以看出,时钟信号CLK0、CLK90、CLK180和CLK270的每一个上升沿分别对应于等效时钟的一个上升沿,从而可以这样表述:使用四路时钟来测量待测脉冲信号并将测量结果相加,等效于使用4倍频的时钟频率为4f的时钟信号测量待测脉冲。根据前面介绍的脉冲计数法可知,测量结果的最大误差为等效时钟的时钟周期,也即是时钟信号CLK0的时钟周期的1/4。通过这样的方式可以在不提高计数时钟频率的前提下,达到减小测量误差、提高计时精度的目的。

使用这一测量方法,在计数时钟频率为250 MHz时,可得到时钟频率为1GHz的等效时钟,从而使测量精度达到纳秒量级。本文在ALTERA公司的QuartusⅡ7.2环境下选用StratixⅢ系列的EP3SE50F484C2芯片进行设计并仿真。下面给出基于这一测量方法的详细设计和仿真结果。

2 实验设计

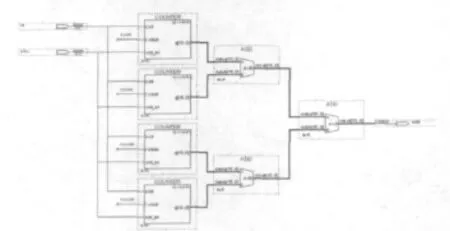

首先,利用Quartus提供的锁相环模块(PLL)生成四路依次相差90°相位的时钟信号。为了降低高频时钟信号对印制板设计带来的影响,设计选用的输入时钟信号频率为50MHz,通过PLL进行5倍频产生频率为250MHz的时钟,并通过PLL的移相功能生成四路依次相差90°相位的计数时钟信号CLK0、CLK90、CLK180和CLK270.PLL模块见图3[5,6]。

图3 PLL模块图

然后,利用Quartus提供的计数模块(COUNTER)产生四个计数模块,分别由计数时钟信号CLK0、CLK90、CLK180和CLK270驱动,在脉冲宽度内进行计数。利用Quartus提供的加法器模块(ADD)对四个计数模块的计数值相加。综合计数模块原理图如图4。其中,输入引脚pulse为待测脉冲信号,输入引脚clr为计数模块清零信号,输出引脚width为测量到的脉冲宽度输出端。

图4 综合计数模块原理图

由于计数时钟信号的频率为250MHz,其周期T为4ns,根据上面介绍的测量技术原理及公式(1)可知,脉冲宽度为t=N1+N2+N3+N4,即加法器最后输出的数值就是测量到的脉冲宽度,单位为ns。

3 仿真结果

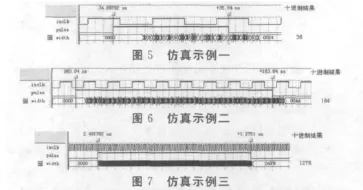

为验证设计,在QuartusⅡ7.2环境下选用StratixⅢ系列的EP3SE50F484C2芯片对设计进行仿真。仿真结果见图5、图6和图7。

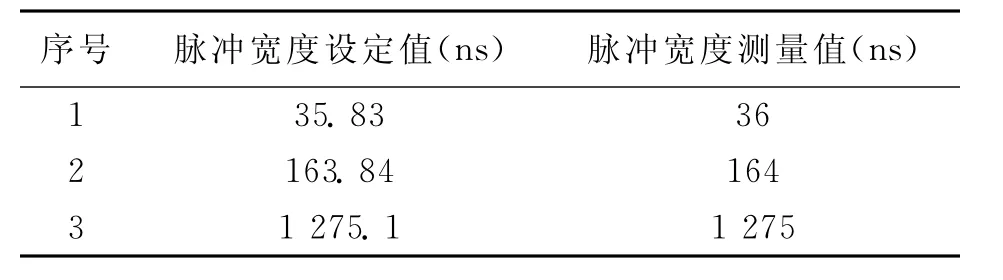

以上示例的脉冲宽度设定值与仿真测量值见表1。比较脉冲宽度设定值与测量值可知,仿真结果符合设计目标,测量精度达到ns量级。

表1 脉冲宽度设定值与测量值

4 结束语

本文介绍的脉冲宽度精确测量方法,在直接脉冲计数法的基础上采用数字移相技术来提高测量精度,并通过仿真验证了设计思路,将脉冲宽度的测量精度提高到纳秒量级。该测量方法可用于需要对脉冲宽度进行测量的各种工程应用中,且该方法可测量的脉冲宽度范围宽,对大于10ns的脉冲都可进行精确测量。当待测脉冲宽度变化时,只需根据脉冲宽度的可能上限更改计数器的位数,方便工程应用。

[1]胡华春,石玉.数字锁相环原理与应用[M].上海:上海科学技术出版社,1990.

[2]Roland E Best.锁相环设计、仿真与应用[M].北京:清华大学出版社,2007.

[3]郑卉卉,程少云.基于数字移相的高精度到达时间测量系统[J].计算机测量与控制,2007,15(4):429-431.

[4]叶超,冯莉,欧阳艳晶.基于FPGA的精密时间间隔测量仪设计[J].信息与电子工程,2009,7(2):159-163.

[5]杨晓慧,杨旭.FPGA系统设计与实例[M].北京:人民邮电出版社,2010.

[6]王诚,吴继华.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005.