基于ARM和NAND Flash的FPGA加载配置在TD-LTE中的实现*

2012-12-07董宏成

董宏成,魏 杨

(重庆邮电大学 通信与信息工程学院,重庆 400065)

TD-LTE无线综合测试仪平台的主要功能是测试接收端与发射端信号的差异,即接收和发射端信号的误码率等性能的优劣,其物理层采用通用的FPGA+DSP+ARM硬件架构,具有开发周期短、可扩展性好等优点。

现场可编程门阵列FPGA是基于门阵列方式为用户提供可编程资源,其内部逻辑结构的形成是由配置数据决定的。由于SRAM的易失性,每次上电时,都必须对FPGA重新进行配置、完成下行链路OFDM信号以及底层交互相关信号的产生等功能。

对于FPGA配置,大多数是采用将配置数据存放在FPGA组成的系统上[1-2]或者将配置数据存放在使用者自己携带的外部存储器中的实现方式,后者在系统上电时需由其他外部控制器读出配置数据再传送给FPGA进行配置。本文提出在TD-LTE无线综合测试仪平台上,通过嵌入式微处理器ARM将配置数据存放于NAND Flash[3]中,由Flash上电启动读出配置数据再对FPGA进行配置。这种方法不但修改、升级简便,而且由于NAND Flash在写入数据时都需要先擦除再写入,所以具有很好的保密性[4],并且可以方便地存储大容量配置数据或多个配置数据文件等。本文介绍了TD-LTE无线综合测试仪平台上电后自动加载对FPGA器件进行配置的设计与实现的新方法,对无线TD-LTE系统的底层控制实现具有重要意义。

1 配置原理

1.1 配置模式

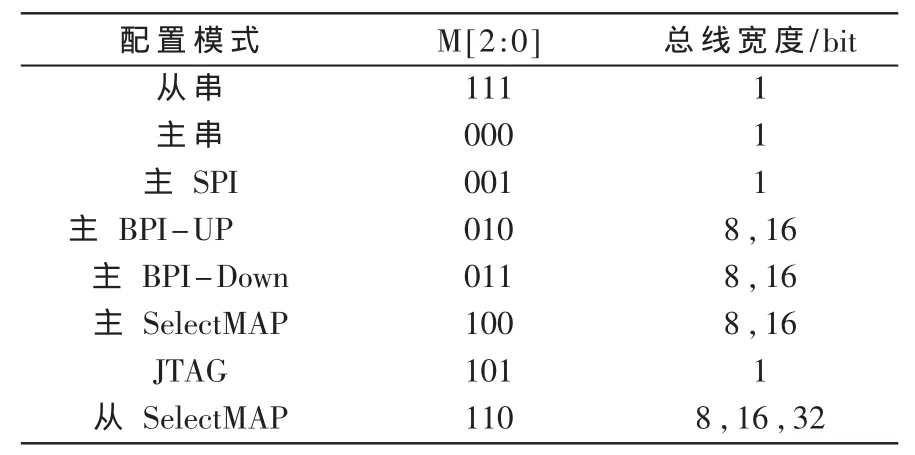

Xilinx公司为其FPGA系列产品提供了多种数据配置方式,在TD-LTE综合测试仪的研究中选用的是Virtex-5系列芯片XC5VSX95T。Virtex-5提供了如表1所示的几种不同的配置模式,其中的从SelectMAP模式最高可以支持32 bit总线宽度[5]。在每次芯片上电初始化完毕后,芯片将以采样模式引脚M[2:0]决定配置模式。

表1 配置模式

1.2 配置方案

本文在FPGA+ARM+NAND的硬件环境下,将ARM作为主控制器,介绍从SelectMAP模式或者从串行模式的配置方案,其中串行模式需要的I/O资源较少,但速度较慢;从SelectMAP模式需要的I/O资源较多,但速度较快。

(1)在串行配置模式下,FPGA在每个CCLK周期载入一个比特的数据,CCLK引脚由外部时钟源来驱动,而且总是每个数据字节的最高位先被写到DIN引脚。从串行配置模式需要用到的配置引脚为模式选择M[2:0]设置为 111、配置时钟 CCLK、配置复位 PROGRAM_B、初始化状态INIT_B、配置完成DONE和配置数据D_IN。其中,ARM除了控制PROGRAM_B、INIT_B外,还需要控制时钟CCLK、配置数据在CCLK的上升沿采样一个比特。通过ARM拉低再拉高相应的GPIO产生CCLK上升沿时序,延时程序则由for循环实现,由时钟控制和比特文件的载入需要分别控制可以知道串行配置耗时是比较多的。

(2)SelectMAP模式提供了与 Virtex配置逻辑之间的一个8 bit双向数据总线接口。从SelectMAP模式支持8、16、32 bit总线宽度。为了利于系统的调试及检测方便,本文选择8 bit总线宽度。该模式所用到的配置引脚为模式选择 M[2:0]、配置时钟 CCLK、配置复位 PROGRAM_B、配置完成 DONE、配置数据 8 bit并行输入 DATA[0:7]和CRC[6]校验信号 INIT_B、片选信号 CS_B、回读信号 BUSY以及从SelectMAP模式使能信号PDWR_B,其中的时钟控制信号可编程实现。在综合测试仪中,FPGA的数据线与双端口RAM的数据线共用,并且将双端口RAM的写使能作为CCLK。因此不需要单独控制,直接向双端口RAM中写数据可同时实现时钟的产生和数据的传送。

在从SelectMAP模式中使用写使能nWE作为时钟线,在传输配置信息和时钟控制上都节约了很多时间。因此,根据TD-LTE综合测试仪的设计要求并考虑到测试的方便性,采用8 bit从SelectMAP模式对XC5VSX95T进行配置是较好选择。

2 总体实现及流程

2.1 配置流程

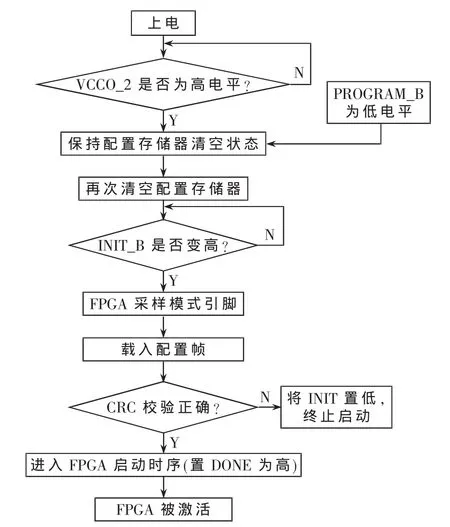

图1给出了FPGA配置流程框图。在上电时,PROGRAM_B输入上的逻辑低电平将会复位配置逻辑,并且使FPGA保持在清空配置存储器的状态。只要PROGRAM_B引脚保持低电平,则FPGA将继续清空它的配置存储器并使INIT_B信号保持为低电平以表明配置存储器在被清空。当PROGRAM_B被释放时,FPGA将继续使INIT_B保持为低电平,直到完成清空所有的配置存储器。只要INIT_B信号变为高电平时,表明清除动作完成,配置就可以开始了。在INIT_B的上升沿,模式选择引脚M[2:0]被采样,以决定配置模式,若为 110,则采用从 SelectMAP模式。此后配置文件信息在CCLK的控制下由D[0:7]共8个配置引脚并行输入XC5VSX95T中。配置数据在CCLK的上升沿采样一个字节。在配置期间芯片会自动进行CRC错误检验,若发生了CRC校验错误,则INIT_B引脚将被置低。当最后的CRC校验成功完成后,FPGA进入启动时序。这个时序期间将会释放DONE引脚(变为高电平),FPGA释放全局三态(GTS),激活I/O引脚,释放全部置位复位(GSR)和全局写使能(GWE)有效,开始执行配置区的逻辑。此后芯片进入正常工作状态。配置时序图如图2所示。

图1 配置流程框图

2.2 硬件设计

图2 SelectMAP模式配置时序图

本系统采用的嵌入式微处理器为S3C6410[7],将FPGA配置文件下载到ARM的存储器存放入Flash中,以ARM处理器作为主设备,FPGA作为从设备。系统上电后,ARM通过读取相应的配置文件对FPGA进行配置,256 MB的DDR SDRAM作为程序运行空间,将NAND Flash中代码移至SDRAM中运行。

2.2.1 外围芯片

(1)S3C6410

S3C6410基于ARM1176JZF-S处理器核,是一类低功率、高性价比、高性能、用于手持和移动等终端设备的通用RISC处理器。其主频芯片可达667 MHz,采用64/32 bit的内部总线架构,拥有比S3C2440、S3C2410等更加丰富的接口。

在S3C6410中,由系统时钟控制逻辑生成所需要的系统时钟信号,用于CPU的 ARMCLK、AXI/AHB总线外设的HCLK和APB总线外设的PCLK。本系统中,采用12 MHz的外部晶体作为S3C6410的外部时钟,ARMCLK:HCLK×2:HCLK:PCLK 分别设置为 553 MHz:266 MHz:133 MHz:66 MHz。

(2)NAND Flash

系统采用 K9F1G08U0C型的 128 MB×8 bit的 NAND Flash。该芯片总共有 1024块,每块有 64(页)×2 GB的容量。额定电压为3.3 V,支持随机读写功能。

(3)双端口 RAM

采用IDT70V28L系列的双端口RAM,其写使能nWE作为配置文件加载控制时钟CCLK。

2.2.2 硬件连接

S3C6410与XC5VSX95T以及双端口RAM主要通过CCLK、PROGRAM_B、DONE、D[0:7]和 INIT_B 信号线相连接,如图3所示。采用S3C6410的通用接口GPN10、GPN12、GPN13 分别控制 INIT_B、DONE、PRORAM_B,用 ARM 的外部存储器双端口RAM的写使能信号nWE控制CCLK,同时其数据线DATA[0:7]作为信息输入的D[0:7]。

2.3 软件设计

根据图2 FPGA配置时序图,主设备ARM编程要实现各信号的时序要求。ARM软件控制设计流程如图4所示,其中应用代码包含FPGA的配置驱动。

2.3.1 比特文件的下载

对所设计的FPGA在Xilinx公司的ISE10.1软件平台上运用Verilog语言编译运行后产生4.25 MB的.bit文件。将此.bit文件通过ARM仿真器RVDS4.1的调试环境Realview Debugger加载到ARM的一段可用内存中。主要方法:在Target选项中选择Load Binary,内存选择为以DDR SDRAM的0x59 000 000作为暂时存放.bit文件起始地址的内存区。这样做的好处是不需要进行额外的下载电缆连接操作,使芯片系统重构时没有对电缆的插拔要求,只需要通过相应软件操作即可。

2.3.2 从NAND启动

将初始化代码和应用代码烧写到Flash后,ARM处理器以NAND Flash模式启动时,内置的NAND Flash控制器将访问控制接口,将其第0块前8 KB的代码自动加载到内部SRAM中,而片内SRAM被映射到地址0x0,上电后运行实现初始化硬件等基本功能。利用片内SRAM中的代码把NAND Flash中的程序代码复制到DDR SDRAM以0x51 000 000作为起始地址的内存中去,通过MMU实现0x51 000 000到0x0的映射,采用 PC指针实现跳转至0x0执行应用代码。

2.3.3 对FPGA发送配置数据

在S3C6410中,通用接口的大多数引脚都是多功能引脚,可以通过端口配置寄存器选择相应的引脚功能。对于端口N,控制寄存器GPNCON用于设定引脚的输入、输出或者特殊的功能。如图3硬件连接框图所示,数据寄存器GPNDAT[10]对应GPN10引脚上的数据,在时钟产生的同时对其写 1、0、1实现 INIT_B的初始时序控制。NAND Flash启动完成初始化后,应用代码实现从Flash相应存储区域读出FPGA配置信息到一段可用地址(如 DDR SDRAM中以0x59 000 000开始的存储区),然后从将其中的数据写到双端口RAM中,由FPGA与双端口RAM的数据线复用,完成配置数据加载到FPGA,实现配置。

由于采用了写使能信号nWE作为配置时钟CCLK,向双端口RAM的地址线中写配置信息即产生时钟,并且在nWE写使能信号的上升沿来实现数据采集的功能。

3 实现结果及分析

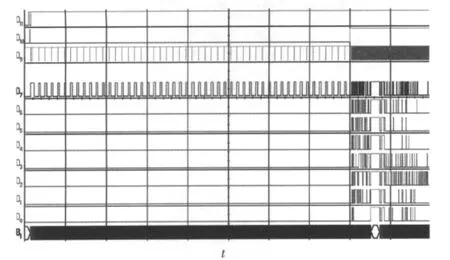

实现结果如图5、图6所示,图中解释了FPGA的CCLK、INIT_B、PROGRAM_B几个控制信号的变化以及部分配置数据。其中,横纵坐标分别表示时间变化和在相应时间变化中的信号采样值,纵坐标D9、D10、D11分别表示 CCLK、INIT_B、PROGRAM_B,D0:D7 作为数据线D[0:7]。其中时钟的产生可以通过向双端口RAM某个可用地址中写数据来实现(这里写的是0x8)。图5中,D10一段连续低电平是FPGA自动CRC校验过程,在CRC校验完毕,D10拉高后开始传送配置信息。图6为FPGA配置部分波形展开图。

图5 FPGA配置实现结果图

SelectMAP模式中总线宽度为8 bit的配置方案在TD-LTE综合测试仪表中已经成功实现。这种配置方式也可以用在其他具有相似硬件环境的情况,如果采用16 bit或者32 bit的传输,相应地时速会成倍提高。

本文介绍的系统采用了ARM+NAND Flash的FPGA配置模式,外围利用SDRAM和DP_RAM的硬件电路,实现FPGA自动加载配置。这种方法灵活且具有保密性,修改、升级简便,可实现多任务电路结构重构和自动重载,满足自动配置的要求,同时也有益于整个系统启动,方便了整个系统启动控制,对无线TD-LTE系统的底层控制实现具有重要意义,应用范围非常广泛。

[1]梅安华,田建生,刘欢,等.基于 PCI总线的 FPGA配置系统的设计[J].计算机测量与控制,2005,13(4):375-377.

[2]王尔申,张淑芳,胡青.嵌入式GPS接收机系统的FPGA配置方法研究[J].计算机工程与应用,2009,45(4):86-88.

[3]128 M×8 bit NAND flash memory REV 0.2[EB].Samsung Electronics.2008.

[4]柔性材料.数据销毁背后的16条法则[EB/OL].(2010-04-16)[2012-1-9].http://www.mcplive.cn/index.php/article/index/id/5347/page/4.htm.

[5]Xilinx,Inc.Virtex-5 FPGA Configuration User Guide[EB].UG191(v3.1)April 25,2008.

[6]Yang Wenlong,Wang Lingli,Zhou Xuegong.CRC circuit design for SRAM-Based FPGA configuration bit correction[J].IEEE,2010(11).

[7]S3C6410X RISC Microprocessor User's Manual[EB].Samsung Electronics.REV 1.10.2008.