基于FPGA的GPS定位信息显示系统

2012-11-15曹新苗林建辉

曹新苗,林建辉,张 兵

(西南交通大学牵引动力国家重点实验室,四川 成都 610031)

0 引 言

全球定位系统(global positioning system,GPS)是美国研制的无线电导航定位系统,能够迅速、准确、全天候地提供定位信息[1-2]。地球上任何一台GPS接收机只要能够接收到4颗以上的卫星信号,经过计算处理后,就能得到这台GPS接收机的位置(经纬度和高度)、时间以及运动状态等信息[3]。

本文以Quartus II软件作为FPGA的开发平台,采用Verilog HDL硬件描述语言,在EP3C10E144C8N芯片上,利用FPGA的可重复编程特点,实现对GPS数据的采集、处理以及显示控制。

1 GPS15L OEM结构板特性和数据输出

本设计选用GARMIN公司的GPS15L接收机,有12个通道,能够快速定位,功耗非常小,数据更新率为每秒一次,其优良的性能既能满足陆地导航的灵敏度要求,也能满足飞行器的动态要求。该OEM板的工作电压为3.3~5.4V,具有2个串行口,串口1为异步串行数据的输入和输出,输入数据为初始位置、时间、秒脉冲状态等设置信息,输出数据为GPS定位信息;串口2接收GPS差分信息,实时修正数据。

该GPS接收机输出的数据格式是美国国家海洋电子协会(National Marine Electronics Association)为海用电子设备制定的NMEA 0183标准格式,该协议采用ASCII码,其串行通信默认参数为:波特率=9600b/s,数据位=8bit,开始位=1bit,停止位=1bit,无奇偶校验[4]。常用的NMEA 0813输出语句有十几种,每种语句是以“S”开头,以<CR><LF>结束,也就是ASCII码字符的“回车”(十六进制的0D)和“换行”(十六进制的0A)。

由于只需要日期、时间和经纬度信息就可实现定位,因此选用最小定位信息GPRMC语句。为了数据处理时更简单,将OEM板初始化,只输出GPRMC一种语句,并设置波特率为19200b/s。其中GPRMC语句格式为:SGPRMC,hhmmss,A/V,ddmm.mmmm,N/S,dddmm.mmmm,E/W,xxx.x,xxx.x,ddmmyy,xxxx,E/W,*hh。例如:SGPRMC,040503,A,3026.6057,N,10412.6057,E,,,011211,,W*67。

从这个例子可以得到UTC日期是11年12月1号,时间为 4∶05∶03,转化为北京时间就为 12∶05∶03,纬度为北纬 30°26.6057′,经度为东经 104°12.6057′。

2 采集与显示GPS定位信息的FPGA系统设计

2.1 硬件设计

整个系统主要是由3个部分组成:(1)OEM板;(2)FPGA;(3)液晶显示模块。

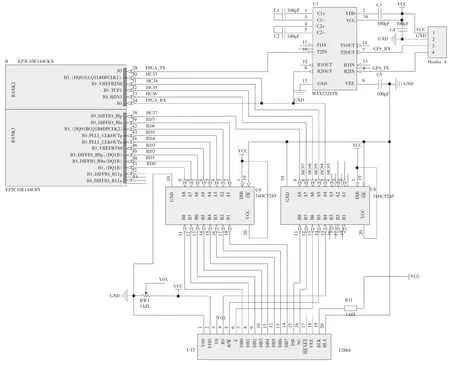

GPS OEM板输出电平为RS-232,而FPGA是TTL电平,因此需要电平转化,这里采用电平转换芯片为MAX232,此芯片是MAXIM公司生产的,包含两路接收器和驱动器的电平转换芯片,适用于各种RS-232通信接口,+5V电源供电,其内部有电压倍增电路和转换电路[5],与FPGA连接十分方便。显示定位数据是采用ST7920控制器液晶模块,此模块可以直接和FPGA连接,并且具有专门的指令,可以灵活的运用。GPS15L OEM板和液晶模块与FPGA连接的原理图如图1所示。

2.2 软件设计

图1 OEM板和液晶模块与FPGA连接电路原理图

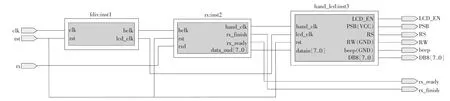

本设计选用可编程逻辑器件FPGA,采用硬件描述语言Verilog HDL按照自顶向下的设计方法设计GPS数据的采集和显示系统[6]。该软件系统主要包括时钟分频模块fdiv、串口模块rx和信息处理以及液晶显示模块hand_lcd,系统顶层文件方框图如图2所示。

图2 系统顶层文件方框图

2.2.1 fdiv分频模块

分频模块主要产生采集和显示GPS定位数据需要的时钟信号频率。FPGA的时钟频率为50MHz,而OEM板串口波特率为19200 b/s,为提高系统的容错性处理,要求分频器的输出时钟为实际串口数据波特率的 N 倍,N 的取值为 8,16,32,64 等[7]。本设计中N的取值为16,所以分频器的输出信号频率为19200×16=307200Hz,这样就需要对FPGA系统时钟进行162分频;液晶显示的时钟频率为2000Hz,同样需要分频,采用的分频方法是先将系统时钟分频为1MHz,再对1MHz进行500分频就可得到液晶显示的时钟频率。

2.2.2 rx串口模块

串口模块主要作用是采集GPS数据,并将采集到的串行数据转化为并行数据输出给数据处理模块,此程序采用状态机来实现,分别为s_idle,s_sample和s_stop 3种状态。

s_idle:此状态用于检测GPS接收机发送数据的起始信号。FPGA系统复位后,接收模块rx就处于空闲状态,在RS232串行通信中,在不发送数据时,串行总线保持逻辑“1”状态,当需要发送数据时,会首先发送一个起始位,其逻辑值为“0”,表示开始发送数据;因此,FPGA系统要不断检测发送过来的数据位是否从1跳变为0,如果发生跳变,状态机就进入到s_sample,采集GPS接收机发送的数据。

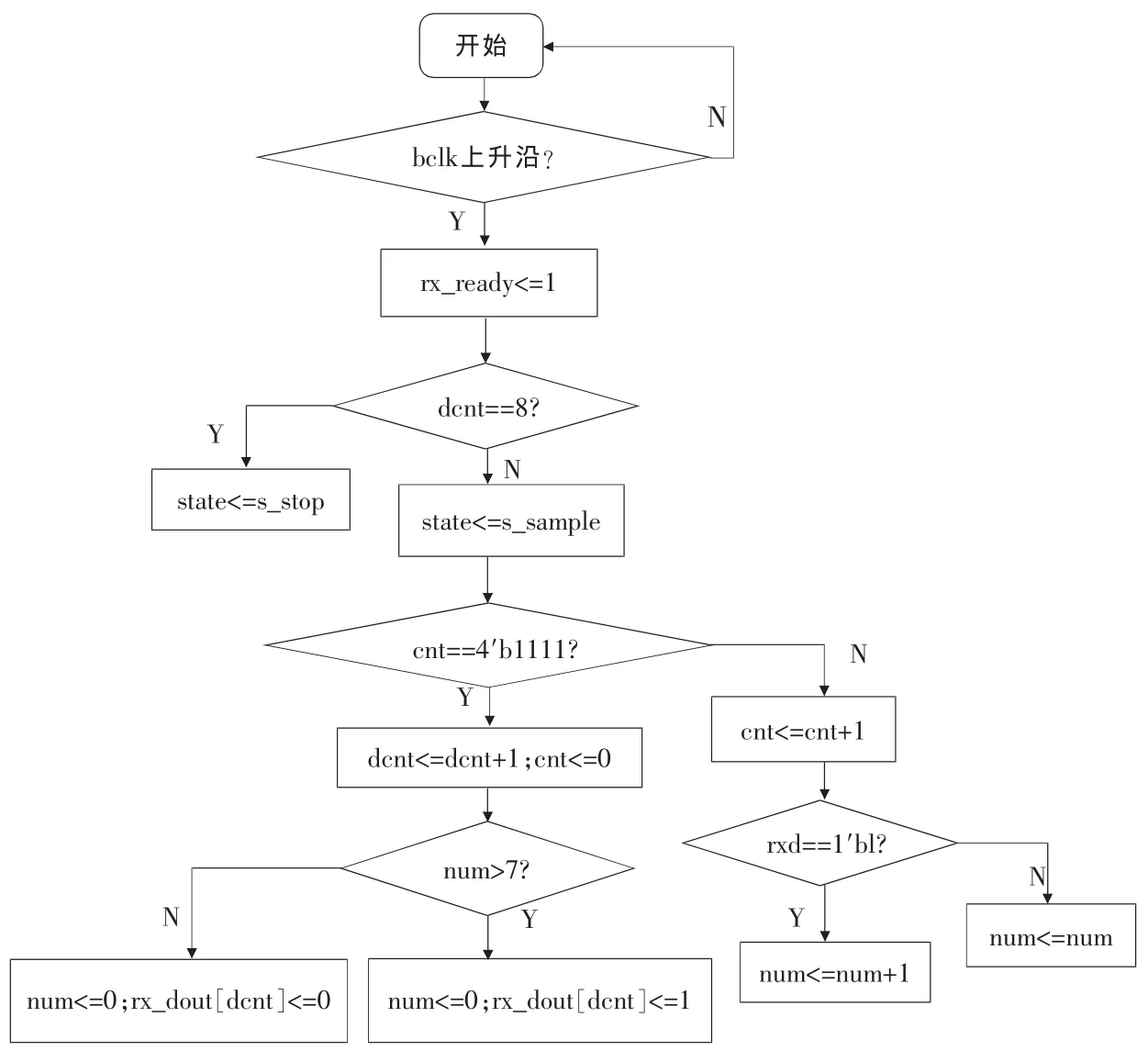

s_sample:这是数据采样状态,在这个状态中,接收模块rx连续采样GPS接收机发送过来的数据,并对每16个采样数据进行最大似然判断,得到相应的逻辑值。做这种判断的目的是得到有效的数据位,需要重复8次,才能接收完一个8位数据。接收时,先将接收到的每个数据位保存在一个8位寄存器中,接收完一个数据后,通过串并转换,将接收到的串行数据转换为并行数据输出。接收完8个数据比特后,就转为s_stop状态。s_sample状态程序的具体流程图如图3所示。

s_stop:这个状态是检测停止位,程序比较简单,只需要计数,计数值为15时就转为s_idle状态,继续接收下一帧数据。

2.2.3 hand_lcd信息处理与显示模块

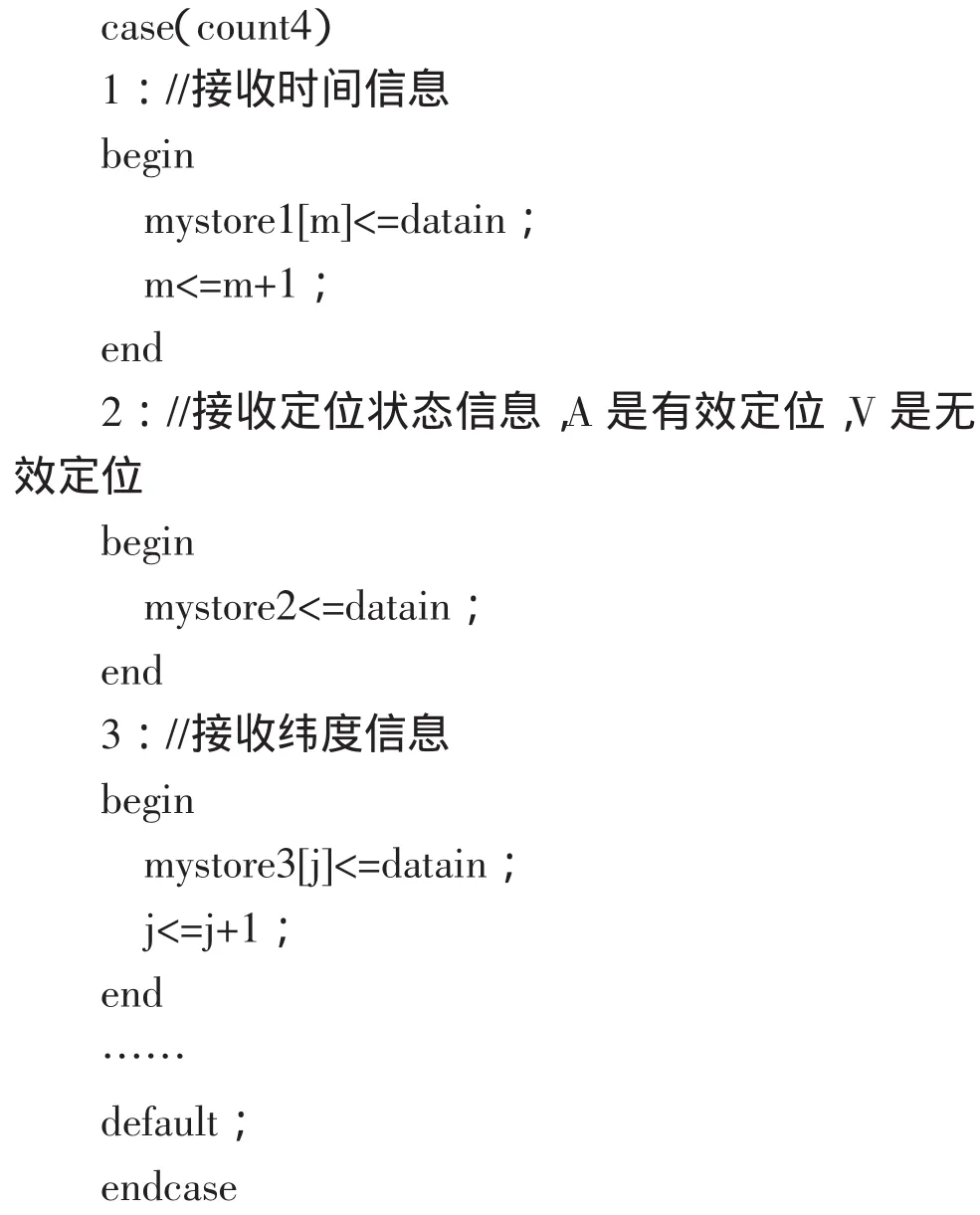

数据处理与显示模块主要是处理采集到的GPS数据,分离出需要的日期、时间、经度和纬度数据并保存,供液晶显示模块调用。处理定位信息时,由于GPS接收机输出的语句只有GPRMC一种,所以只需要对接收到的数据判断开头是不是“S”,再通过判断逗号数量的方法,就可以将需要的定位数据分离出来,接收到“*”后,停止接收。程序流程图如图4所示。

图3 s_sample流程图

图4 处理GPS定位信息流程图

利用逗号数量分离定位数据的程序为:

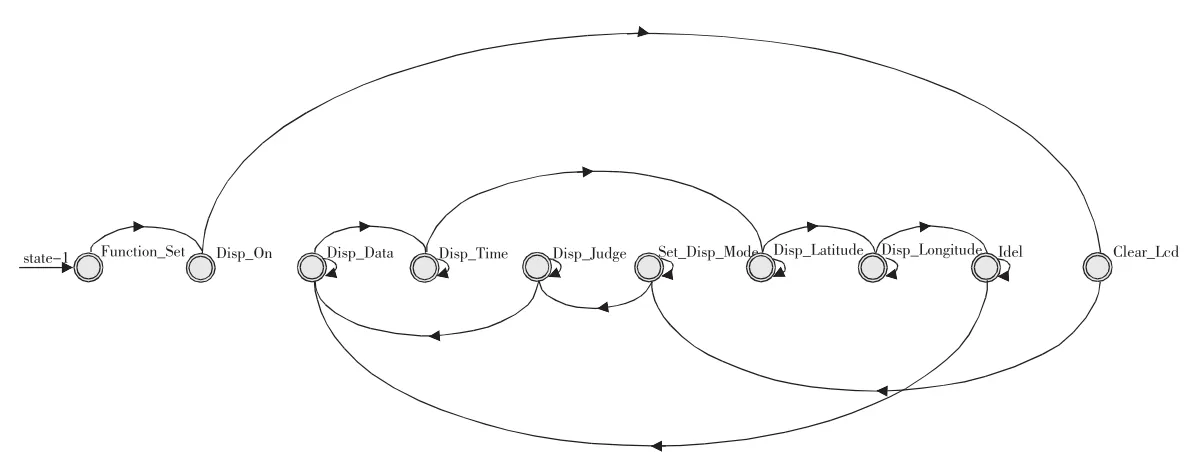

数据显示部分程序利用状态机来实现,同样采用编程语言来实现此状态机,最后在Quartus II中得到状态转移图[8],此液晶显示模块程序的状态图如图5所示。

使用液晶模块显示数据,首先需要对其进行初始化,设置显示方式以及清屏等操作,流程图如图6所示。

图5 液晶显示模块程序状态转移图

图6 液晶显示模块初始化流程图

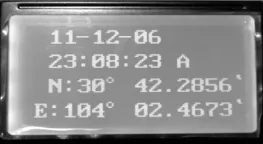

图7 GPS定位信息显示

液晶模块初始化完成之后,需要判断GPS数据处理是否完成,如果完成就分别显示各定位数据。显示日期和时间之前,需要对日期和时间进行转换,GPS接收机发送的是世界时间,转换为北京时间需要加上8h,如果超过24h,则已是第二天,需要对接收到的日期加1,同时对时间减去24h,就会得到准确的北京时间[9]。依次显示完各定位数据后,返回一个完成标志给数据处理程序,使其继续处理接收到的GPS数据。

本系统经过多次修改与调试,最终能够正确显示GPS定位信息,可以实现基本定位功能。图7显示了日期时间以及当地的位置信息:11年12月6号,23∶8∶23,北纬 30°42.2856′,东经 104°2.4673′。

3 结束语

本文给出了硬件电路原理图,论述GPS定位数据采集、处理以及显示的方法,在Quartus II开发平台下进行编译、仿真和下载,成功实现GPS定位信息显示。该系统与无线传输模块、电子地图等连接后,可以实现列车定位功能。也可以通过无线传输模块,将FPGA采集和处理后的时间、经纬度以及列车速度信息实时传输到电脑上,应用到高速列车检测中。

[1]刘美生.全球定位系统及其应用综述(二):GPS[J].中国测试技术,2006,32(6):5-11.

[2]许化龙,胡来红,曲从善,等.基于ARM的嵌入式GPS接收机设计与实现[J].战术导弹控制技术,2006(2):50-53.

[3]徐鑫.基于GPS的车辆定位监控系统的设计与实现[D].成都:电子科技大学,2005.

[4]李明光,陈国通,王莉静.C8051Fxxx单片机与GPS-OEM板数据通信的实现[J].河北工业科技,2009(4):243-245.

[5]刘晓,伍小东,姚军光,等.基于单片机采集GPS数据系统的设计[J].青岛科技大学学报,2005(2):172-175.

[6]陈忠平,高金定,高见芳.基于Quartus II的FPGA/CPLD设计与实践[M].北京:电子工业出版社,2010:75-127.

[7]云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2009:43-197.

[8]EDA先锋工作室,吴继华,蔡海宁,等.Altera FPGA/CPLD设计(基础篇)[M].2版.北京:人民邮电出版社,2011:65-216.

[9]赵志礼,孟庆辉,张松涛,等.基于单片机的GPS定位信息处理[J].电子测试,2009(10):45-48.