面阵CCD时序抗弥散方法研究

2012-10-11董龙李涛

董龙 李涛

(北京空间机电研究所,北京 100076)

1 引言

在遥感相机成像时,目标景物的对比度差别很大,比如地面目标和云层的亮度差别甚至可以达到1000倍以上,这样由云层造成的弥散现象,通常会影响四周的景物,特别是垂直方向上的目标景物。为了消除这种弥散现象,通常采用抗弥散技术。

CCD抗弥散通常采用硬件方式,包括了电极型侧面抗弥散(Lateral Anti blooming Gate)、植入型侧面抗弥散(Lateral Anti blooming Implant)和垂直抗弥散(Vertical Anti blooming)。前两种侧面抗弥散是在像元侧面制作电荷倾泻沟道,这样通常会降低像元的填充率,从而减小像元感光面积;而垂直抗弥散由于工艺问题,器件抗高能粒子辐射能力有限,通常不应用到航天相机上。另外,以上三种方法在工艺制作上都需要增加3~4道工序,会进一步降低器件成品率,增加器件成本。

时序抗弥散(Clock Anti blooming,CAB)技术是在不改变CCD硬件结构的前提下,充分利用面阵CCD的结构特点,通过成像区的时序控制,来实现抗弥散功能。该技术成本低,可操作性强,特别是对于航天相机器件无法更换的特点,通过该方法,可以使无抗弥散功能的CCD器件增加抗弥散功能。

2 时序抗弥散技术原理

时序抗弥散技术是通过在曝光时间执行特殊的时序驱动来实现的,同时所要求的高电平偏置和低电平偏置,与通常的时序偏置也不相同。该技术利用了CCD工艺制作上的若干特点,包括CCD表面态俘获、n沟道CCD电荷存储特性、饱和弥散的两种方式和低电平翻转态特点。

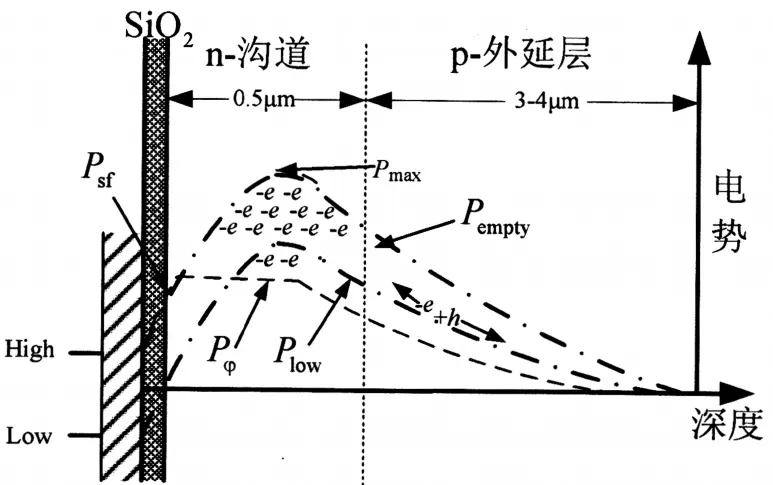

在表面型CCD上,时序电极与Si材料之间有一层绝缘的SiO2介质,这个氧化层对外呈阳性,光生电子会被吸附到表面上,这样在电荷转移的过程中,这些吸附电子就会滞留在CCD内,从而降低电荷的转移效率,另外这些吸附电子随着时间会慢慢释放出来,污染后续的成像过程,这种现象被称为量子效率延滞(QEH)。为了消除这种现象,埋沟型CCD技术被广泛采用,该技术是在P型Si衬底沉积一层N型半导体,如图1所示。当电极电压为高电平,未收集到电荷时,电势曲线Pempty如图2。

随着深度的不断深入,电势会在n沟道内达到电势最大值Pmax,之后由于P区耗尽区域的影响,电势逐渐降低到衬底电压。当光生电荷产生时,电子会根据电势分布的高低向电势最高的地方移动,收集到部分电荷时,电极降为Pφ所示曲线。这样电子就在n沟道内部收集和转移,避免了表面态俘获,从而降低了量子效率延滞现象。

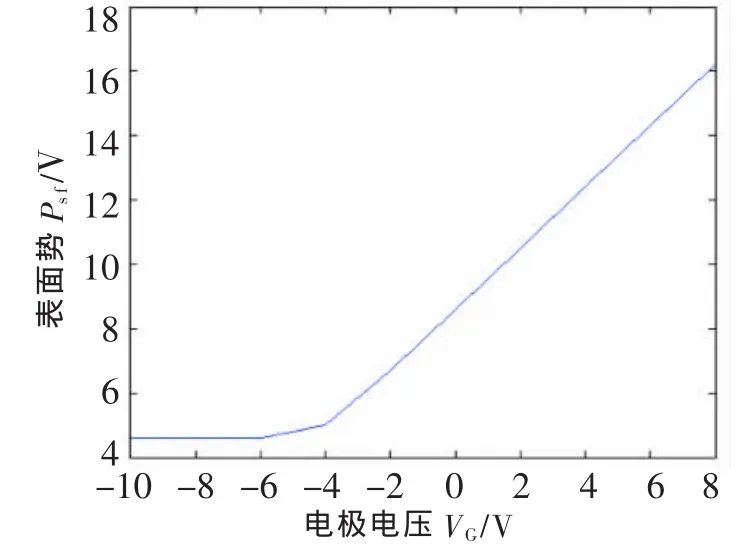

在图2中,当电极为低电平时,电势如图中Plow所示,Pφ与Plow之间的电势差构成电荷壁垒,阻止电荷在像元间移动。CCD表面电势Psf随着电极电压的降低而线形降低,但是,当表面势降到一个临界点的时候就不再随着电极电压的降低而降低,称这个电压临界点为翻转电压Vinv。表面势随电极电压变换曲线如图3所示。

图3 表面势随电极电压变化曲线Fig.3 Relation curves of surface potential vs electrode voltage

当电极电压VG<-4V时表面势基本保持不变,-4V电压就称为翻转电压Vinv。此时表面势Psf等于衬底电势,当电极电压继续降低时,会从面阵CCD列间沟阻中吸引出空穴,吸附在CCD的SiO2/Si分界面上,从而保持表面电势恒定。

光生电荷存储在n沟道电势最大处,随着光生电荷的增多,电势会逐渐降低,在势阱饱和之前会有两种状态,分别是:弥散型饱和(Bloomed FullWell,BFW)和表面型饱和(Surface FullWell,SFW)。

弥散型饱和状态如图4所示,当电极高电平比较低时,随着势阱内电荷的积累,电势逐渐降低,在电荷未接触表面时,已经达到隔离电极的最大电势,这时,电荷就会跨过隔离电极,弥散到周边像元。

图4 弥散型饱和Fig.4 Bloomed FullWell

表面型饱和状态如图5所示,在电荷弥散之前,已经接触到SiO2/Si表面,被表面所俘获。随着电荷的继续增加,弥散现象随后才会出现。CCD的饱和模式属于弥散型饱和还是表面型饱和,是由像元驱动时钟的高电平偏置所决定,高电平较低时属于弥散型饱和。

图5 表面型饱和Fig.5 Surface FullWell

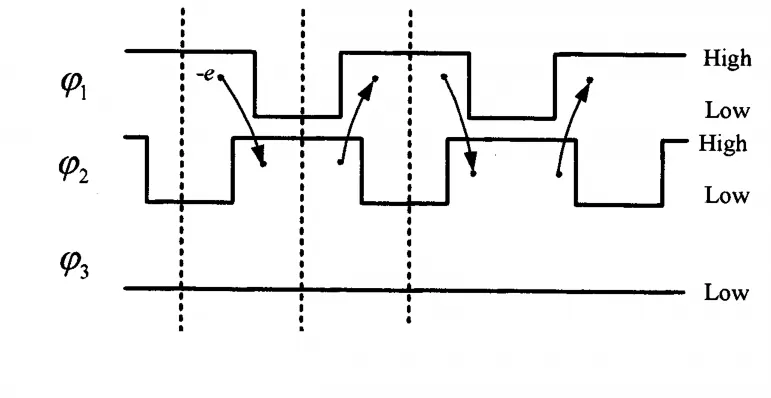

时序抗弥散就是利用CCD的以上特点,采用时序控制的方式实现抗弥散功能,其驱动时钟时序如图6所示:

图6 CAB技术时序Fig.6 CAB clocking setup

从以上描述可以看出,CAB实现依赖两个条件:1)偏置条件,高电平偏置必须保持在SFW区域内,从而使多余电子不是弥散到相邻像元而是吸附在SiO2/Si表面,低电平要保持在翻转电平之下,从而保证能从沟阻中吸引空穴,使电子-空穴复合;2)频率条件,必须保证足够的驱动时序频率从而使电子复合速度要大于光生电子速度,有效抑制弥散产生。

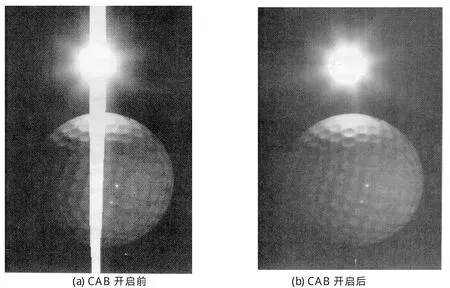

某公司研制CCD产品采用CAB后效果图如图7所示,由于高亮灯光造成的弥散,使得整个列方向的图像都达到饱和,见图7(a)。采用CAB技术后,弥散现象得到控制,见图7(b)。

图7 采用CAB前后效果对比Fig.7 Blooming characteristicsw ith and w ithoutCAB

3 CAB工作参数测试方法

为使CAB技术实现,需要确定CCD器件高电平处于SFW区域且低电平低于Vinv,以及在曝光周期中CAB时序的频率。

(1)高电平SFW区域标定测试

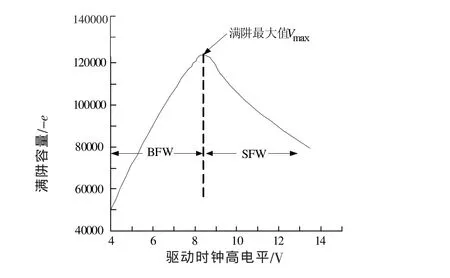

测试步骤如下:首先将CCD表面上半部分进行遮挡,然后采用均匀光照射CCD表面,采一帧图像,可以确定遮挡位置;然后调整均匀光的光照条件,如果某一帧图像遮挡位置上移,说明该光照条件下CCD产生了弥散。保持该光照条件,调整CCD驱动时钟的高电平,从低电平逐渐调高,CCD输出信号强度会随着驱动电平变化,见图8。

图8 满阱容量随驱动电平变化曲线Fig.8 Bloomed FullWell as a function of driving level

(2)低电平偏置标定测试

CAB要求时钟驱动低电平小于翻转电压Vinv,但是在器件封装后无法测量,因为需要测量CCD衬底材料的电压,所以只能在器件制造过程中由制造商进行测量。

如图9所示,由于输出电极(Output Transfer Gate,OTG)与驱动电极结构相同,所以其电气特性与驱动电极相同,而VREF受表面势限制,与表面势呈线性关系,所以曲线与电极电压-表面势曲线(图3)具有完全相同的结构特点,通过曲线的拐点可以确定出电极的翻转电压Vinv。

图9 CCD输出端结构Fig.9 The structure of CCD output

另一种更简单的方法,器件厂商给出的垂直转移时钟驱动低电平,通常采用公式计算得到,其中为垂直转移低电平,所以。

(3)CAB时序频率标定测试

CAB频率标定过程见图10。

图10 CAB频率标定过程图例Fig.10 Illustration for CAB frequecy calibration procedure

在图10中,首先将CCD面阵遮挡上半部分或下半部分,用于界定弥散是否发生。在时刻①CCD快门关闭,CCD匀速读出。时刻②打开快门,用均匀光照射CCD表面,光照强度保证CCD处于弥散状态,同时将CCD匀速读出,斜率表示光生电子速率(-e/s)。时刻③关闭快门,并清除CCD内残余电荷。时刻④加载CAB时序,并打开快门。时刻⑤正常读出CCD数据。时刻⑥从小到大调整CAB时序频率直到找到合适的频率为止,图10中当每个曝光周期进行2次时,仍然处于弥散状态,4次首先达到抗弥散要求,于是可以计算出每次消除电荷速率(-e/(s·次))。

在CCD曝光时,可以根据标定的电荷消除速率,计算曝光周期内CAB时序频率。

4 CAB使用范围及限制条件

时序抗弥散效果是由每个曝光时间内可运行CAB时序频率来决定。预实现抗弥散倍数根据实际需要决定CAB时序频率。

时序抗弥散技术可以在CCD器件无抗弥散功能时,通过时序控制来实现抗弥散功能,对于全帧CCD和帧转移CCD都可以使用;对于TDICCD,由于采用CAB后图像信号会发生前后移动,造成与延迟积分的二次图像的非同步问题,影响图像效果。该技术一定程度上增加了时序电路的复杂性,同时改变电平偏置,也容易产生器件氧化绝缘层的击穿,所以实验过程需要小心控制。

时序抗弥散技术适用于慢速扫描应用,并且在闪光灯照明情况下不起作用。同时,只有在垂直转移为三相或四相的情况下才能使用,而两相垂直转移,无法构成电荷壁垒,同时也无法驱动到表面满阱状态。

应该注意的是,时序抗弥散技术会降低CCD的满阱容量,图8所示,相对于器件正常工作的最大满阱容量而言,高电平偏置越大,抗弥散效果越好,同时满阱容量也越低,CCD的动态范围随之减小。

另外,采用CAB技术相当于提高了垂直转移信号频率,所以会进一步提高面阵垂直转移时序驱动信号的功率,增加系统功耗。同时垂直转移效率也会受到影响。

所以在采用CAB技术要综合评估抗弥散特性、动态范围、转移效率、功耗等因素,从而使系统性能得到进一步优化。

(References)

[1]Janesick JR.Scientific Charge-coupled Devices[M].Bellingham Washington USA:The International Society for Optical Engineering,2000:293-300.

[2]Janesick JR.Prevent blooming in CCD images[J].NASA Tech Briefs,1992,16(7):20.

[3]Hynecek J.Electron-hole Recombination Anti blooming for VirualOhase Imager[J].IEEETrans.Elec.Devices,1983,ED-30(8):4-30.

[4]Chatter jee P,Taylor G.Optimum Scaling of Buried ChannelCCDs[J].IEEETrans.Elec.Devices,1980,ED-27(3):122-125.

[5]KosonockyW,Carnes J,Kovac M,etal.Control of Blooming in Charge-coupled Imagers[J],RCA Review,1974,35:3-24.

[6]武利翻.CCD纵向抗晕结构设计与优化[J].现代电子技术,2010,33(16):172-174.WULifan.Design and Optimization of CCD Image Sensor with Vertical Anti- blooming Structure[J].Modern Electronics Technique,2010,33(16):172-174.(in Chinese)

[7]韩采芹,柳忠彬.科学级帧转移型CCD相机拖影问题的处理[J].科学技术与工程,2009,9(15):4336-4338.HAN Caiqin,LIU Zhongbin.Disposal of Smearing in Scientific Grade Frame-transfer Type CCD Camera[J].Science Technology And Engineering,2009,9(15):4336-4338.(in Chinese)

[8]米本和也.CCD/CMOS图像传感器基础与应用[M].陈榕庭,彭美桂.译.北京:科学出版社,2006:8-63.Kazuya Yonemoto.Fundamentals and Applications of CCD/CMOSImage Sensor[M].CHEN Rongting,PENG Meigui.Beijing:Science Press,2006:8-63.(in Chinese)

[9]王庆有.图像传感器应用技术[M].北京:电子工业出版社,2003:10-22.WANG Qingyou.Application Technology of Image Sensor[M].Beijing:Publishing House of Electronics Industry,2003:10-22.(in Chinese)

[10]陈榕庭.CMOS图像传感器封装与测试[M].北京:电子工业出版社,2006:25-32.CHEN Rongting.Packaging and Testof CMOS Image Sensor[M].Beijing:Publishing Houseof Electronics Industry,2006:25-32.(in Chinese)