SOC设计SI分析优化方法研究

2012-09-27李春伟

李春伟

(北京华大九天软件有限公司 北京 100102)

SOC设计SI分析优化方法研究

李春伟

(北京华大九天软件有限公司 北京 100102)

基于集成电路规模与设计工艺不断发展的现状,SI问题日益突出和严重。系统介绍了SOC设计SI的概念、分类及产生基理,根据电路工程设计经验,重点阐述了在SOC设计SI的设计、优化、分析方法,介绍了利用EDA设计工具在芯片设计过程中对SI进行阻止、优化、分析的流程及方法,并对各种设计优化方法进行了利弊的对比分析,对芯片设计提供了很好的指导,结合EDA工具及合理的设计流程方法能够有效的保证芯片设计的良率和性能。

信号完整性;双倍间距;功能噪声;延迟噪声;时序窗口

随着电子、通信技术的飞速发展,集成规模越来越大,I/O数越来越多;设计工艺尺寸不断减小,布线密度不断增加;时钟速率越来越高,所有这些因素导致信号完整性[1](SI)问题日益突出;也成为芯片设计一次性成功,性能稳定,达到设计要求的不能不考虑的重要因素之一,笔者对SI的概念,产生原因,及在工程设计中的方法进行了系统的阐述和分析,旨在为工程设计人员提供理论和设计指导。

1 SI概念

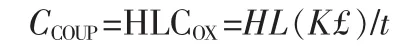

串扰噪声分析[2-3]是SI分析的关键,分析耦合引起的串扰噪声以同层相邻金属线为主,同层间的耦合电容可以通过下面的线间模型估算:

耦合电容=线厚度×耦合长度×单位面积耦合电容的大小

其中:£为真空电容率;k为相对介质相对介电常数;t为介质厚度,即线间距。异层间耦合电容较小,因为线宽减小和采用相邻正交布线的策略都减小了耦合面积。

从噪声角度,net分为入侵者与受侵者:

1)入侵者指对受侵者注入噪声的net;

2)受侵者指由其相邻一条或几条net通过交叉耦合电容对其产生噪声效应的net。

噪声效应分为2种:

1)延迟噪声;

2)功能噪声。

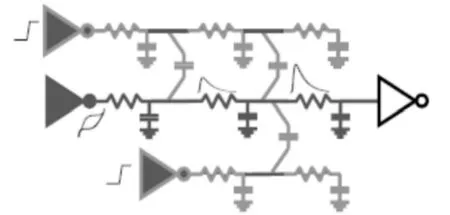

当入侵者与受侵者同时翻转时产生的噪声为延迟噪声,此种噪声改变受侵net的延迟和slew(即transition)值。

功能噪声产生情况为:受侵net为一稳态而施加于其上的噪声使其产生glitch。此种glitch能够传播到稳定元件,如锁存器,从而改变电路状态导致功能错误,图1为两种噪声产生原理图。

图1 噪声类型Fig.1 Noise class

2 芯片设计中prevent SI

SOC芯片设计分为几个阶段对SI效应进行优化。

1)floorplan phase

避免congestion区域,尤其对于有多总线之间互连的memory模块及BIST逻辑附近,比较容易产生拥塞,在进行布局规划时要进行考虑以避免SI的产生。

2)place phase

设置合理的transition约束值,做到SI与时序的trade off;

避免使用太小驱动类型的单元;

在高扇出端口设置max-fanout约束,例如scan_enable、reset端口,另对高扇出端口进行buffer tree设计;

在受侵net上增加其单元的驱动能力;

设置max-cap约束,以在实现时考虑耦合电容对SI的影响。

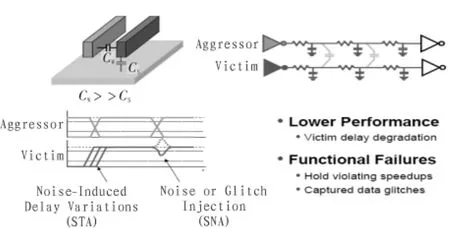

3)route phase

避免长平行线的产生及增大之间的距离,利用SI driven进行布线,以下为ICC命令

当使能crosstalk prevention时,为减小噪声,在trackassignment phase,会利用简化的串扰检查器尽量避免平行的长线来避免噪声的产生。

一般来讲,时钟线为高翻转线,容易产生SI,传统方法会为其设置double space及用地线屏蔽的方法,但如果route congestion比较严重的情况下,对所有这些线进行设置会占用很大的布线资源,所以可以先用PT-SI工具进行分析,只针对delta delay比较大的线进行约束设置。

3 芯片设计中fix SI

SOC设计包含以下几种fix SI方法。

1)驱动类型优化;

2)插入 buffer单元;

3)双倍间距;

4)屏蔽线。

如前面所述,噪声包含功能噪声和延迟噪声,首先应修复功能噪声,双倍间距对于功能噪声和延迟噪声都比较有效,并且比屏蔽线方法更容易实现,同时比另外两种方法具有更小的负面影响,因此利用此方法进行功能噪声的修复。

延迟噪声的修复,对于setup时间增大单元驱动类型比较有效,但要注意增大驱动类型可以使得比较弱的受侵net变成一条侵害net;对于hold时间插入buffer方法比较有效;双倍间距对两者都有效。

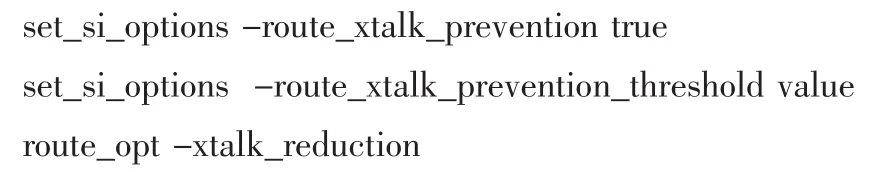

以下是ICC优化SI的参考脚本命令:

4 SI分析

对于噪声分析,两条net间串扰的影响很大程度上取决于它们timing-window的重合程度。例如,当入侵net翻转而受侵net不翻转,则对于受害net会产生一噪声bump;当入侵net翻转而受侵net也翻转,则对于受侵net会有可能变慢也有可能变快。如果在同一个timing-window中有多个入侵net翻转,则受侵net的噪声影响将是所有入侵net的叠加效应。对于一个pin的timing-window的计算是考虑所有到达该pin的path中到达时间最早和最晚的情况的综合。如果只有一条path到达该pin,则其timing-window会很窄。考虑timingwindow提高了分析的精度但可能会花费更长的时间。图2为噪声计算例图。

图2 噪声计算Fig.2 Noise pulse calculation

ICC命令如下,

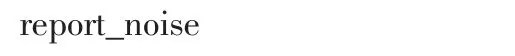

功能噪声分析包含两种:above-low;below-high(参考图3模型)。above-low noise发生的条件为,当受侵net处于逻辑低电平,而入侵net处于从低电平到高电平的转换状态;同理,below-high noise发生在当受侵net处于高电平而入侵net处于从高电平到低电平的转换状态。当噪声损害超过了工艺阈值则会引起逻辑错误从而导致电路不能正常工作。

图3 稳态驱动模型Fig.3 Steady state driver modeling

ICC噪声分析结果命令如下:

5 结 论

随着深亚微米设计的不断发展,SI[4-6]分析优化是芯片设计中不可缺少的设计步骤,尤其是最近几年,不断提高的创新逻辑设计使噪声新问题从模拟和混合信号领域蔓延到纯模拟和纯数字设计领域,特别是当一个敏感电路要接收弱信号,而它又位于进行着各种计算、控制逻辑和有频繁跳变信号的电路旁边时,会影响敏感电路的工作及性能,甚至可以毁掉整个芯片。因此,在混合信号芯片上处理噪声问题显得尤为重要。笔者根据工程设计经验,分析了在设计过程中的有效方法,SI的分析优化需要多次迭代才能满足最后的时序约束设计要求。首先要尽量避免SI的产生,然后在对产生的SI问题进行优化,最后用sign off分析工具例如PTSI进行最后的分析验证。

[1]孙加兴,叶青.串扰噪声及串扰噪声模型的分析[J].中国集成电路,2004(9): 46-52.

SUN Jia-xing,YE Qing.Model analysis of crosstalk noise and crosstalk noise[J].China Integrated Circuit,2004(9):46-52.

[2]周平,戴庆元.芯片设计中串扰噪声的分析与改善[J].半导体技术,2004(1): 56-59.

ZHOU Ping,DAI Qing-yuan.Analysis and avoidance of crosstalk in IC design[J].Semiconductor Technology,2004(1):56-59.

[3]吕霆,祝亮.高速时钟电路的信号完整性设计[J].电子工艺技术,2004(1):39-41.

LV Ting,ZHU Liang.Signal integrity of high-speed design[J].Electronics Process Techonology,2004(1):39-41.

[4]Shukla V.Signal Integrity for PCB Designers[M].Reference Designer,ISBN 0-9821-3690-0.

[5]Bogatin E.(2009).Signal and Power Integrity-Simplified[M].Second Edition.Upper Saddle River,New Jersey:Prentice Hall,ISBN 978-0-13-234979-6.

[6]Arunachalam R,Raiagopal K,Pileggi L T.TACO:Timing Analysis With Coupling[M].2000 doi:10.1145/337292.337415.

Research of SI analysis and optimization for SOC design

LI Chun-wei

(Huada Empyrean Software Co.,Ltd.Beijing100102,China)

As the continuous development of integrated circuit design and the design process,SI Issues have become increasingly prominent and serious.Introduce the concept、classes and generated reason of SI (signal integrity).In the base of circuit design experience, focus on the methods of prevent、fix and analysis during SOC design, analyze the disadvantage and advantage of every method.Can effectively guarantee the chip design and yield performance in the base of EDA tool and reasonable design method flow.

SI; double space; function noise; delay noise; timing window

TN492

A

1674-6236(2012)06-0026-03

2012-01-11稿件编号:201201043

李春伟(1981—),女,河北枣强人,硕士,工程师。研究方向:IC设计。