基于SPI总线的多路数据采集系统的设计

2012-09-26宋俊杰黄元峰雷元林

李 宁,宋俊杰,黄元峰,雷元林

(1.武汉工程大学 电气信息学院 湖北 武汉 430205;2.汉江丹江口铝业有限公司 湖北 丹江口 442700)

随着微处理器的发展及其在各领域的广泛应用,人们对电子测量技术和电子仪器系统提出越来越高的要求,对测试速度和精确度的要求也与日俱增。测试系统主要包括对实时数据的高速采集、现场显示和分析处理3部分,其中最重要的一环就是实时数据高速采集,因为它关系到能否真实反映被测对象的状态和性能。根据实际项目需要,文中基于80C51F040单片机的SPI总线和AD7891芯片,设计实现了多路数据的高速采集。文中给出了系统的主要硬件电路和对时序控制的软件编程。

1 系统的硬件实现

本数据采集系统功能是能对多路电压和电流进行高速采集和分析处理,其要求精度高,线性度好,采集电压要求以1 mV为单位,模拟信号输入范围为-10~+10 V。系统处理芯片采用Silicon Laboratories公司出品的C8051F040单片机是完全集成的混合信号系统级芯片(SOC),具有与MCS-51完全兼容的指令内核,该系列单片机采用流水线处理(pipe line)技术不再区分时钟周期和机器周期,能在执行指令期间预处理下一条指令,提高指令执行效率。而且大部分C8051F040单片机具备控制系统所需要的模拟和数字外设,包括看门狗、ADC、DAC、电压比较器、电压基准输出、定时器、PWM、定时器捕捉和方波输出等,并具备多种总线接口,包括UART、SPI、SMBUS(与 IC 兼容)总线以及 CAN 总线。 C8051F系类单片机采用Flash ROM技术,集成JTAG,支持在线编程。C8051F系列单片机诸多特点和优越性,使其广受单片机系统设计工程师青昧,成为很多测控系统设计的首选机型[1]。虽然C8051F040内部提供A/D转换器,但在实时高速采集中易受干扰,性噪比比较低,A/D转换速度不能满足高速数据采集系统的要求,为了满足系统的指标、提高数据的精确性采样和系统的抗干扰能力,本数据采集系统根据实际情况采用外扩的A/D转换芯片[2]。

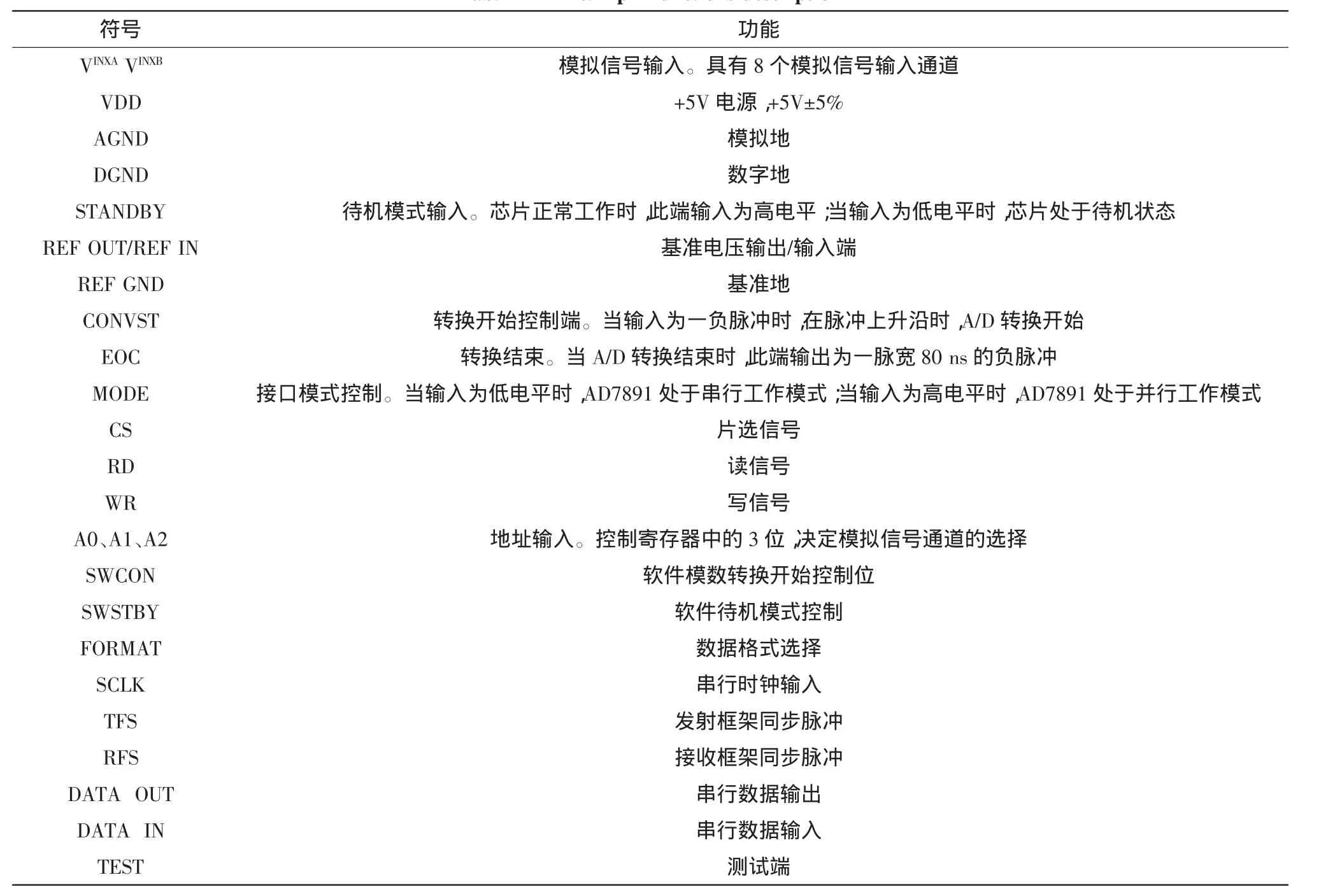

本数据采集系统采用的A/D芯片是美国ADI公司推出的一种AD7891 12位数据采集系统(DAS),它具有并行和串行两种工作模式,适合各种微处理器、控制器以及数字信号处理机接口。AD7891内含有多路转换器、采样保持放大器、12位高速ADC、+2.5 V基准电压源和高速接口电路,并有8个具有过压保护的模拟信号通道,AD7891-1可承受的过压为±17 V。AD7891的模数转换时间是1.6 μs,采样时间为1.4 μs。当只对一个通道信号采样时,采样率为500 kSPS;当对8个通道信号逐个采样时,采样率为62.5 kSPS,AD7891-1使用硬件或软件方法控制转换开始得数据采样时间分别为0.6 μs和 0.7 μs,相应的数据采集率分别为 454.5 kSPS和435 kSPS。AD7891采用单电源工作,功耗低,可选择输入信号的范围,也可并行或串行工作,非常适合用于数据采集系统、电机控制、移动通信系统和测试设备等方面的应用[3]。AD7891管脚功能说明如表1所示。

通常在高速数据采集系统中,AD7891和单片机之间的接口有串行和并行两种方式,采用软件控制数据线的方式来满足系统所要求得采集速度。由于C80C51F040单片机具有SPI总线接口功能,所以本数据采集系统采用串行工作方式,数据的读取通过单片机的SPI总线来传输,不仅能够满足采集系统的快速性要求,在硬件上也较易实现[4]。图1是AD7891与80C51F040单片机的接口电路。

表1 AD7891管脚功能说明Tab.1 AD7891 pin functions description

2 系统的软件实现

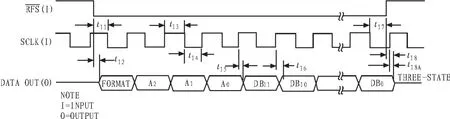

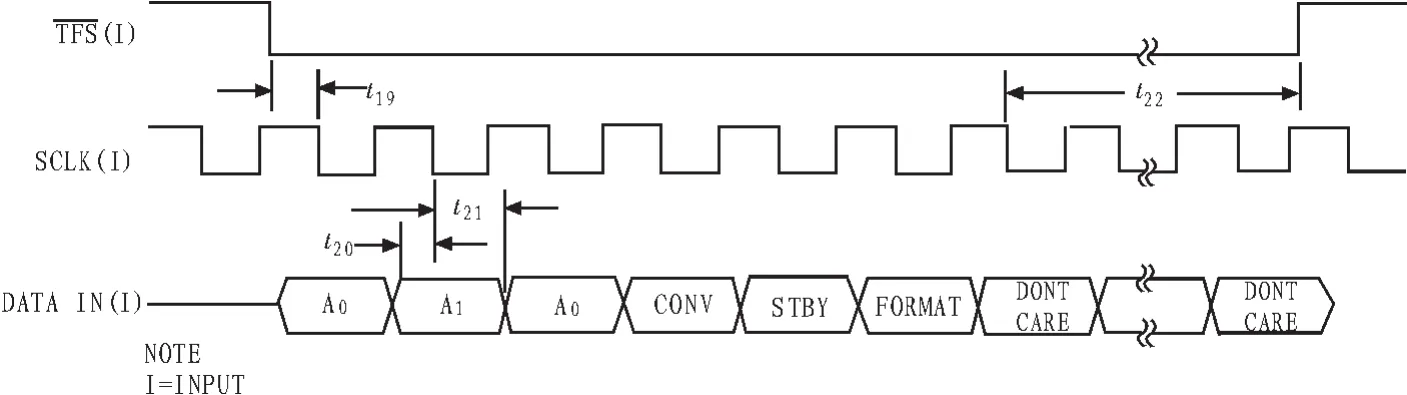

为了实现对模拟量的高速采样,首先要对AD7891的时序进行分析,图2为AD7891的串行读操作时序图,图3为AD7891的串行写操作时序图。

图1 AD7891与C8051F040单片机接口电路Fig.1 AD7891 and C8051F040 MCU interface circuit

图2 AD7891的串行读操作时序图Fig.2 AD7891 serial read operation sequence diagram

图2为AD7891的串行读操作时序图,从图2中可以看出,当单片机要从AD7891中读取数据时,必须先将置低,串行数据时一位一位的接收的。在整个数据传输过程中,必须一直保持低电平。传输的数据格式是一次传输16位数据,数据的传输是以FORMAT位开始的,紧接着是3位地址位,接下来是12位数据位,存放的是12位AD转换的值,每一位数据都是在时钟的上升沿开始发送的,16位数据发送完成后,DATA OUT线一直保持高阻态直到和SCLK其中任意一个有一个上升沿的脉冲出现[5]。

图3 AD7891的串行写操作时序图Fig.3 AD7891 serial write operation sequence diagram

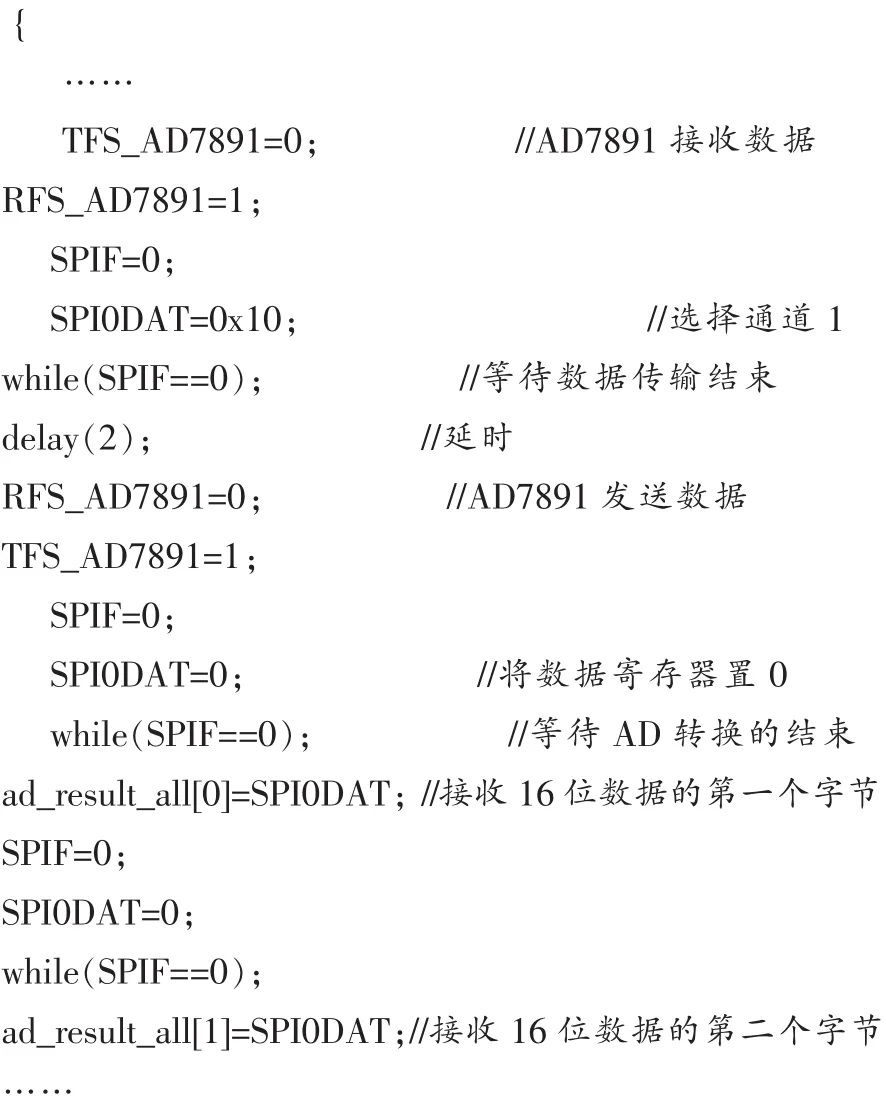

图3为AD7891的串行写操作时序图,从图3中可以看出,当单片机向AD7891中写数据时,必须先将置低,AD7891的控制寄存器只接收前6位数据,前三位A0、A1、A2用于配置AD采样通道,在接收完前6位数据之后不再接收数据,数据的接收都是在时钟的下降沿进行的[6]。下面给出通道1采集的主要程序代码(C语言)

3 结束语

文中基于串行SPI通信方式,设计了一个高速数据采集系统,用SPI总线来实现数据的读取,能够满足数据采集系统的要求,具有硬件结构简单,软件编程容易的特点。

[1]童长飞.C8051F系列单片机开发与C语言编程[M].北京航空航天大学出版社,2005.

[2]潘琢金.C8051F040/1/2/3/4/5/6/7混合信号ISP FLASH处理器数据手册[Z].新华龙电子有限公司.

[3]徐爱均,彭秀华.单片机高级语言C51 Windows环境编程与应用[M].北京:电子工业出版社,2003.

[4]陈劲超.利用增强型并口设计12位数据采集系统[J].电子工程师,2001,27(7):1-3.CHEN Jing-chao.Use of enhanced parallel port design of 12 bit data acquisition system[J].Electronic Engineer,2001,27(7):1-3.

[5]刘春生,游志刚,李晓波.AD7891高速数据采集系统的原理与应用[J].电子工程师,2001(3):6-9.

LIU Chun-sheng,YOU Zhi-gang,LI Xiao-bo.AD7891 high speed data acquisition system principle and Application[J].Electronic Engineer,2001(3):6-9.

[6]张迎新,雷文,姚静波.C8051F系列SOC单片机原理及其应用[M].北京:国防工业出版社,2005.