基于LPC2132数字信号源的设计与实现

2012-09-26郭志俊

郭志俊

(浙江水利水电专科学校 浙江 杭州 310018)

在计算机控制技术、通信技术飞速发展的今天,信号源作为现代电子产品设计和生产中的重要工具,其应用越来越广泛,对信号源的频率范围、稳定度、幅值与频率微调等提出较高的要求,普通的信号源己经不能满足现代电子技术的要求,因此,低成本高精度信号源的设计,在高校教学和产品开发中的推广使用具有非常重要的意义。本设计以PHILIPS公司生产的LPC2132微控制器为主控芯片,采用专用的直接数字合成 (DDS)芯片AD9850产生正弦波和方波,的采用LPC2132+CPLD(EPM7128AETC100)方案产生三角波,设计了模拟信号放大与增益控制电路。可以实现多种波形输出,输出信号频率和电压峰-峰值步进可调,是一款新型的数字可调信号源。

1 系统原理与硬件设计

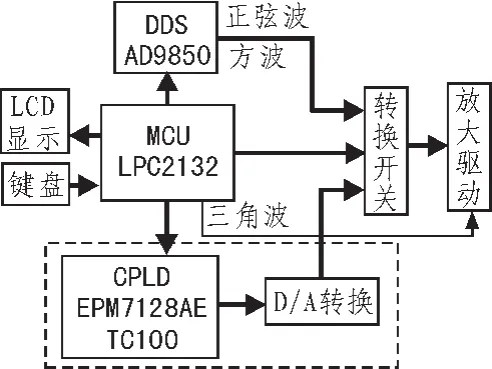

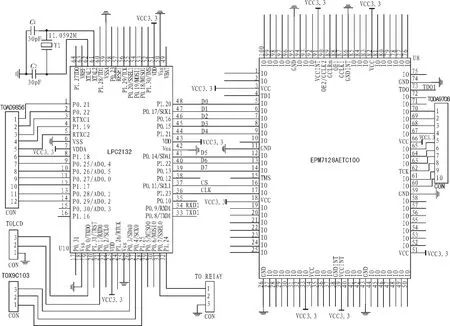

信号源的硬件整体结构如图1所示。以单片机LPC2132为控制核心,主要由键盘与LCD显示模块、正弦波和方波发生模块(DDS)、三角波发生模块(CPLD与高速D/A)、增益控制和放大模块组成。系统设计方案是根据信号源连续可调多波形输出的要求,采用MCU发送频率控制字给DDS芯片AD9850来实现的正弦波和方波的连续输出,而三角波的实现是由MCU发送频率控制字给CPLD和D/A产生。同时,单片机可以控制模拟转换开关选择输出波形,通过对放大驱动电路的数字电位器控制改变输出增益。信号的类型、幅度和频率的设置及显示,由键盘和LCD显示器实现。

图1 系统整体结构框图Fig.1 Whole system structure diagram

1.1 直接数字频率合成的原理

直接数字合成技术 DDS(Direct Digital Synthesizer)是应用十分广泛的频率合成技术,用数字的方法获得一个正弦信号原理如下:设单频正弦信号表达式为:

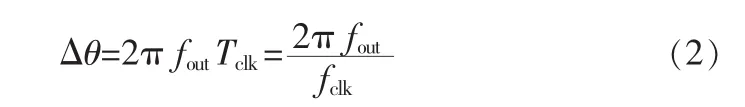

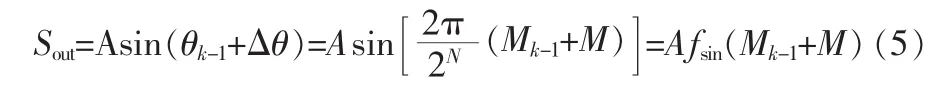

为了便于采用数字技术,对连续的正弦信号进行离散化处理,即把相位和幅值均转化为数字量。用频率为fclk的基准时钟对正弦信号进行抽样,在一个基准时钟周期Tclk内,相位θ的变化量为:

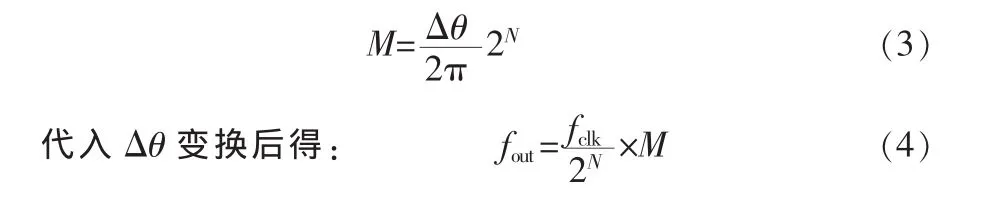

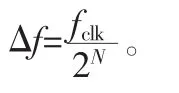

Δθ为模拟量,为了把Δθ转化成数字量,将2π切割成2N等份作为最小量化单位,从而得到Δθ的数字量M为:

其中Mk-1指前一个基准时钟周期的相位值。

由此可知,只要用频率控制字M进行简单的累加运算,就可以得到正弦函数的当前相位值。而正弦信号的幅值就是当前相位值的函数。获得正弦信号的方法如图2所示:先构建一个N位的相位累加器,在每一个时钟周期内,将相位累加器中的值与频率控制字相加,得到当前相位值。将当前相位值作为ROM的地址,读出ROM中的正弦波数据,再通过D/A转换成模拟信号。只需改变频率控制字,就可以一个频率和相位都可编程控制的模拟正弦波输出,此正弦波可直接经过比较器可转换为方波输出。

将相位转化为数字量以后,正弦信号描述为如下形式:

图2 正弦信号发生器原理框图Fig.2 Sine signal generator principle diagram

1.2 AD9850电路设计

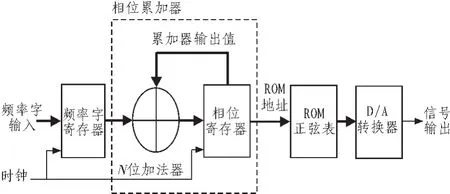

信号产生采用单片机LPC2132和专用DDS芯片AD9850组成,电路原理如图3所示,单片机与AD9850的数据传送采用并行接入方式,电路通过J1接口与LPC2132相连,其中,D0~D7与单片机系统的数据总线相连,RESET、FQ_UD、W_CLK分别与单片机的I/O口线相连。AD9850内部DAC为电流输出,其满量程输出电流可通过外接电阻R1调节,IOUT和IONTB为DAC输出的电流信号。通过外接电阻R3和R4将电流信号转换为电压信号。由DAC输出的电压信号经过低通滤波,目的在于滤除高频杂散和谐波,设计中采用了一片集成集成开关电容低通滤波器LT6600,截止频率为10 MHz,内部带有全差分放大器,通过改变R7和R8的阻值可获得不同的放大倍数。AD9850内部设有高速电压比较器,将低通滤波器的输出信号和一固定的直流电平 (来自LT6600的第2脚和第7脚)送到比较器的输入端,可得两路与正弦信号频率相同且互为反相的方波信号。

图3 AD9850电路原理图Fig.3 AD9850 circuit principle diagram

主要技术参数分析:1)具有极高的频率分辨率和相位分辨率,且相对频带很宽。这是DDS最主要的优点。因为DDS的频率分辨率决定于相位累加器的位数和参考时钟频率,只要相位累加器的位数足够长,DDS的频率分辨率可以达到足够高,所以说频率分辨率和相位分辨率是传统的频率合成方法无法比拟的。2)杂散抑制差,也是DDS的主要缺点。DDS在寻址波形表时,都采用了相位截断技术,它的直接后果是给DDS输出引入了杂散。同时波形存储器中的波形幅度量化引起有效字长效应,还有DAC的非理想特性,都导致DDS的杂散抑制性能差。3)不能够获得很高的相位噪性能指标。DDS的相位噪声主要由参考时钟信号的性质、参考时钟的频率与输出频率之间的关系以及器件本身的噪声决定。在实际工程中,必须考虑包括相位累加器、ROM、和DAC等各部件噪声特性对DDS相位噪声性能的影响。

1.3LPC2132+CPLD电路设计

由于DDS技术的实现依赖于高速、高性能数字器件,控制方式也比较固定,专用DDS芯片一般只能产生正弦波和方波。三角波的产生尽管可将方波信号经积分电路进行积分转换来实现,但很难满足不同频段对积分电容的要求,因此用DDS芯片产生方波实现三角波信号的输出频率范围十分有限。

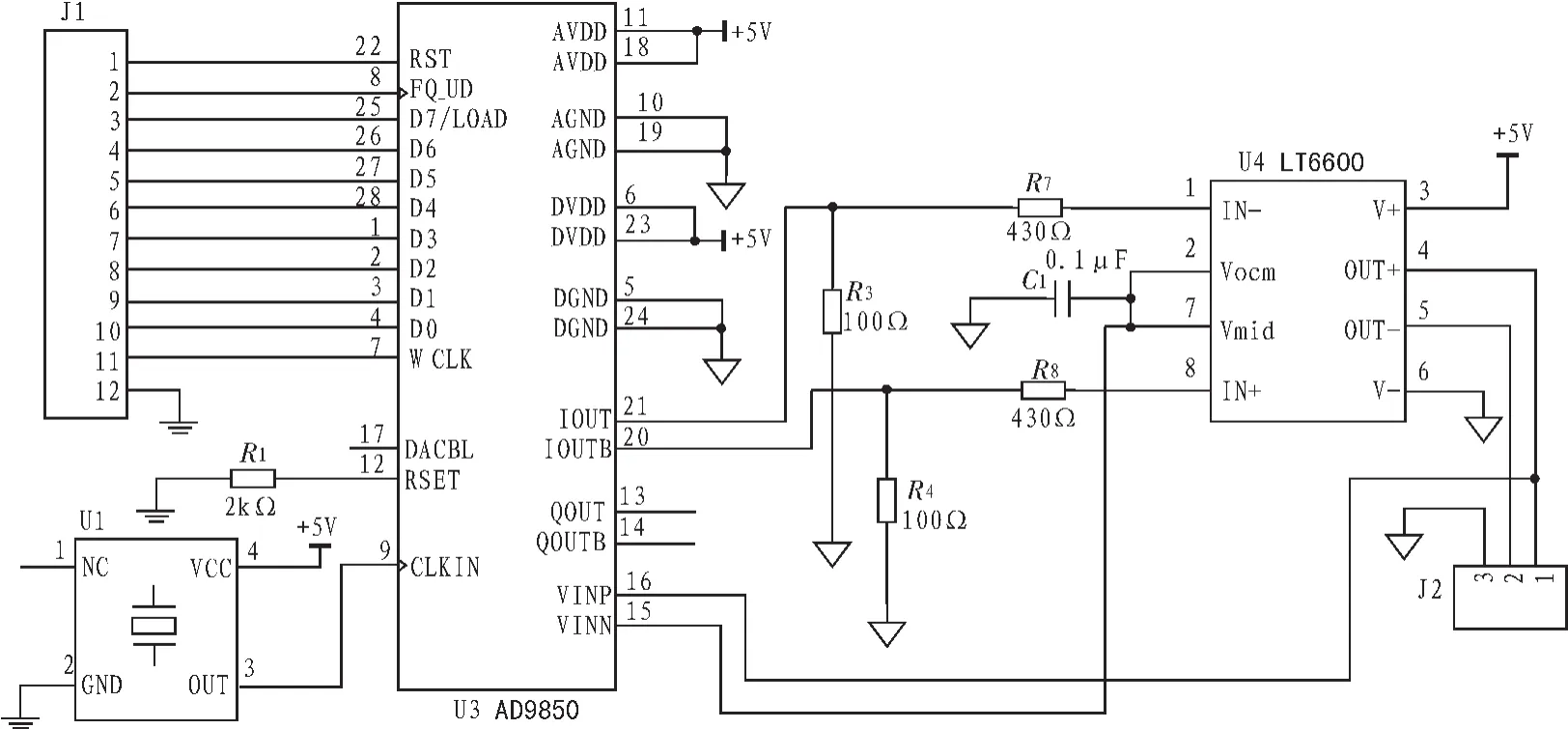

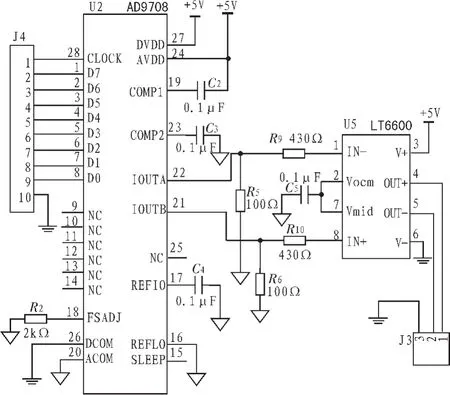

三角波信号发生电路的设计由两部分组成,第一部分是单片机和 CPLD(EPM7128AETC100)接口电路设计,如图 4所示,单片机LPC2132通过并行接口向CPLD中的频率字寄存器发送频率字,向CPLD中的双口RAM传送波形点阵数据。并行接口信号线包括:8位数据线,读信号、写信号、片选信号、地址锁存信号、地址信号。低8位地址线通过CPLD内部的锁存器产生,这样可以减少并行接口信号的数量。第二部分是用于三角波波形重建,由高速D/A转换器AD9708和单片集成滤波器LT6600组成如图5所示,AD9708由CPLD直接控制,AD9708的数据线和时钟线与的I/O脚相连,设计中将模拟电源输入端串接一磁珠再与数字电源连在一起抑制杂散噪声。为了获得相对纯净的波形信号,D/A转换器的输出的应加低通滤波器,以滤去镜像频率分量和谐波分量。低通滤波器的设计采用单片集成滤波器LT6600,输出带宽大于2 MHz,通带增益为12 dB,LT6600采用单端输入、双端输出的形式,来自AD9708的模拟输入信号,送LT6600的V+输入端,通过J3口输出差分三角波信号。

图4 LCP2132与CPLD接口电路图Fig.4 LCP2132 and CPLD interface diagram

1.4 放大与驱动电路的设计

单片机LPC2132通过控制模拟转换开关使得输出波形在正弦波、方波和三角波之间转换,其信号都是滤波器输出的差分模拟信号,该模拟信号除了交流分量外,同时还含有2.5 V的直流分量。

因此,在放大电路之前加一级差分电路去除直流分量,将差分模拟信号提取出来如图5所示。设计放大电路时,考虑到放大倍数和转换速率这两个因素,这里选择了增益带宽相对较高双运放MAX4016,信号增益调整是通过单片机控制数字电位器X9C103(反馈)来实现。功率驱动由高速电流反馈双运放THS3092完成,输出电压的范围可达到±10 V,输出电流最大值为400 mA。

2 主程序设计

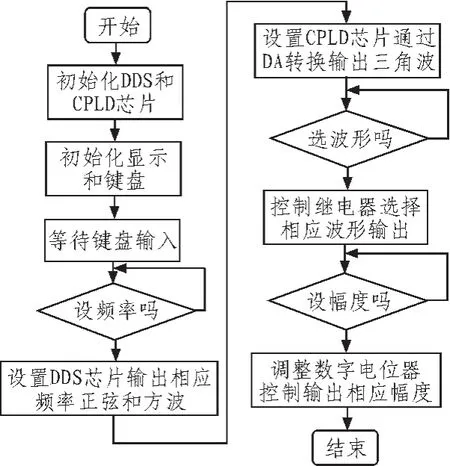

主程序完成堆栈指针设置,定时器常数设置,中断控制字设置,对CPLD的配置,LCD模块初始化等功能。完成配置以后,就进入波形选择模式,等待键盘输入。主程序流程图如图6所示。

图5 D/A转换与滤波电路Fig.5 D/A transformation and filter circuit

图6 主程序流程图Fig.6 Main program flow chart

3 结束语

经测试表明,所设计的信号源,可以实现多种波形输出。输出信号频率在1 Hz~2 MHz范围,可通过键盘进行设置分段调节,频率步进间隔可达10 Hz。可灵活设置输出信号的电压值,在50 Ω负载条件下,信号的电压峰-峰值Vopp在0~5 V范围内可调,调节步进间隔为0.1 V。系统同时可实时显示输出信号的类型、幅度、频率和频率步进值,具有较高应用价值。

[1]贾立新.电子系统设计与实践[M].北京:清华大学出版社,2007.

[2]周立功.ARM嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2005.

[3]徐柳娟.基于PIC的高精度矩形脉冲信号发生器的设计与实现[J].浙江水利水电专科学校学报,2007(4):18-19.

XU Liu-juan.Based on the PIC of high precision rectangular pulse signal generator of design and implementation[J].Zhejiang WaterConservancy and HydropowerCollege journal,2007(4):18-19.

[4]缪欣,唐慧强.基于ARM的数字信号发生器的设计与实现[J].微计算机信息,2007,23(10-2):129-130.

MIU Xin,TANG Hui-qiang.Based on ARM digital signal generator of design and implementation[J].Microcomputer Information,2007,23(10-2):129-130.

[5]吴海超,邢斯瑞.基于AD9850的嵌入式信号源设计与实现[J].现代电子技术,2009,16(303):47-49.

WU Hai-chao,XING Si-rui.Based on the AD9850 embedded signal source design and implementation[J].Modern Electronics Technique,2009,16(303):47-49.

[6]刘雁飞,郝建国,郑燕.一种基于DDS技术的信号源及其CPLD实现[J].西安邮电学院学报,2005,10(1):51-52.

LIU Yan-fei,HAO Jian-guo,ZHENG Yan.A signal generator based on DDS and its implementation on CPLD[J].Journal of Xi’an University of Posts and Telecommunications,2005,10(1):51-52.

[7]张洋.基于CPLD的简易数字频率计的设计[J].现代电子技术,2011(19):183-186.

ZHANG Yang.Design of simple digital frequency meter based on CPLD[J].Modern Electronic Technique,2011(19):183-186.

[8]何敏,王道平.基于CPLD的线阵CCD驱动电路设计[J].电子科技,2011(9):73-75.

HE Min,WANG Dao-ping.The design of iinear CCD driving circuit[J].Electronic Science and Technology,2011(9):73-75.

[9]史小斌,宋思盛,黄根全.PCI总线从设备接口的CPLD实现[J].电子科技,2011(11):59-62.

SHI Xiao-bin,SONG Si-sheng,HUANG Gen-quan.Implementation of PCI slave interface using CPLD[J].Electronic Science and Technology,2011(11):59-62.