110~240 VAC交流数字信号输入接口电路分析与软件实现

2012-09-19邓志刚

孙 伟 , 邓志刚

(1.施耐德电气(中国)有限公司上海分公司 上海 201203;2.东华大学 上海 201620;3.上海海事大学 上海 201306)

随着智能技术的发展,工业用电子产品通常需要有很多的逻辑输入接口,实现产品和外界之间的通信,对产品进行智能控制。通常交流逻辑接口通常使用电阻分压的方式实现,电阻上损耗的能量大,一般情况下都会有多个逻辑输入接口,因此产品整体功耗就非常大;另外在传统的输入信号识别方法是通过判断隔离输出的高低电平来确定输入的高低,这就导致再有一个小的脉冲的时候就会引起误判,导致了产品的抗干扰能力差。基于以上问题在输入端提出了一种阻容分压的采样方式,来降低产品功耗,隔离输出端通过判断0脉冲的宽度来判断输入的状态,保证产品的可靠性。

1 硬件设计

1.1 110~240VAC交流输入接口定义

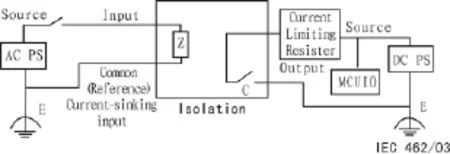

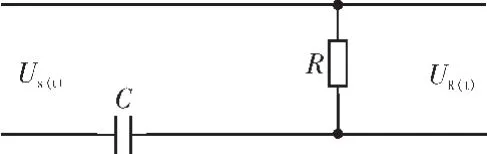

图1描述了一种交流数字信号输入接口电路实现的原理。

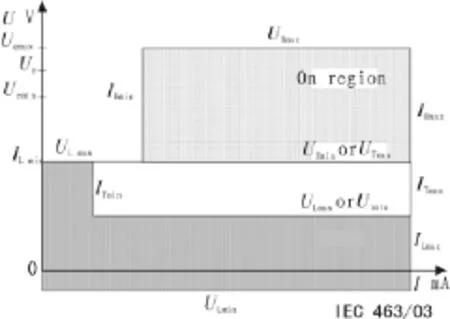

根据IEC61131-2[1]中的规定,逻辑输入要满足下面的波形。即:其实现的脉冲电压-电流操作如图2所示。

图1 I/O口定义Fig.1 I/O definition

图2 U/I工作域Fig.2 U/I operation regions

上图用图形的方式描述了交流输入电压和电流关系。在工作区包含3个状态:ON、Transition和OFF。必须同时超过最小UT和IT,并且先大于最小IH,然后大于最小UH,才能离开OFF状态进入到ON状态:所有的输入U-I曲线应该位于ON区域内。电压小于零的区域仅仅对DC有效。

在IEC61131-2中同时也规定了各个区域的临界值。本文讲述的是交流数字信号输入接口的设计与分析,满足的电压要求为100~240 V,因为要同时满足这两种等级,所以门限值的选择如表1所示。

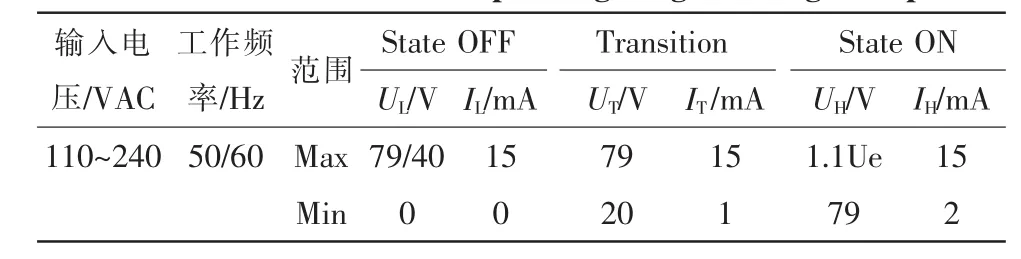

表1 110~220 VAC I/O的工作范围定义Tab.1 110~220 VAC operating ranges for digital inputs

1.2 电路实现

交流输入范围相对来说非常的宽,这就意味着开和关的电压水平之间的误差比固定输入电压的要窄。考虑到电源频率的误差范围通常为47~63 Hz,因此在79VAC@47 Hz时,输入必须为‘ON’,在 40VAC,63 Hz时必须为‘OFF’。 同时,根据标准中的类型 1规定,在‘ON’时输入电流须大于等于2 mA,在‘OFF’时的输入电流小于15 mA。通常情况下在120 VAC输入的时候电流应该为2.6 mA左右,在240 VAC时,输入电流为1.3 mA左右。

关键问题是如何减少交流数字信号输入对能量的消耗。一个阻性输入在120V/2.6 mA时产生312 mW的功率。同样电路负载下,把电压提高一倍到240 V,那么消耗的功率为增大4倍,将达到到1.248 W。在最大的线电压输入时消耗的功率达到了1.5 W。这对于有多个输入逻辑的产品,如果不在功率消耗或者工作温度范围上妥协,阻性输入结构是不能用在100~240VAC的供电信号上的。因此,本文中介绍的AC输入结构使用阻容分压代替电阻分压方法。

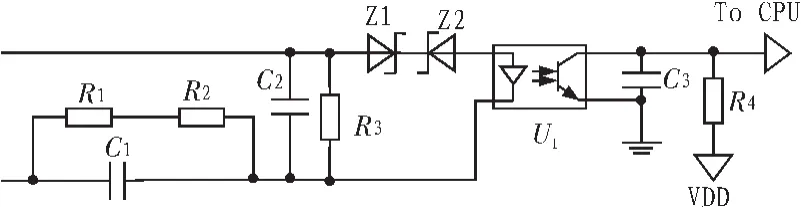

其电路如图3所示。

图3 I/O电路图实现Fig.3 Application circuit of I/O

不使用传统的电阻分压方法,此电路初级阻抗分压使用电容和电阻分压的方法实现,根据电阻和电容的阻抗设定电压和电流阈值。考虑到误差,工作频率在47~63 Hz之间,让电容的阻抗大约为阻的阻抗的10倍。这就意味着90%的输入降压是在电容上,大大地降低了逻辑输入的功耗。

输入断开的时候,输入分压电容上可能会残留有一个高电压。如果不小心接触到输入端子,这个电压可能会导致潜在的危害。因此用2.6Meg的电阻R1、R2并联在分压电容的两端,在输入断开后快速的放掉电容的残留电荷。电容在一秒钟内放电,而且这个阻值对测量电路没有影响,因为它的阻抗比电容容抗大两个数量级。

一个小电容C2与4.99 kΩ分压电阻R3并联来滤除高频噪声。考虑这个电容的积累误差,因此确定其值为100 nF。由于跨接在这个电容两端的最大的电压是光耦二极管正向相电压加上齐纳二极管的门限和正向导通电压,因此25 V电压等级的电容完全够用了。

电压阈值是由阻容分压比和齐纳二极管的阈值电压决定的。一旦流过电阻的电压超过了齐纳二极管Z2的稳压电压加上光耦U1和Z1的正向导通电压,那么就会有电流从光耦中流过。当流过光耦二极管的电流足够大,使得光耦输出的三极管导通的时候,那么就能看到逻辑0电平了。因为这是交流输入的交流光耦,逻辑0电平每半个周期出现一次。此处选择的齐纳二极管为6.8 V稳压。

1.3 电路分析

仅仅考虑RC分压电路[2],那么上面的电路图可以简化图4所示的电路。

图4 电路简化图Fig.4 Simplified circuit

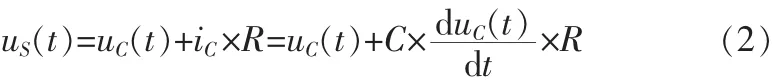

其中 uS(t)=Vm×sinωt,有很多方法可以求出电阻两端的电压[3],此处利用解微分方程的方法[4],公式如下:

即:

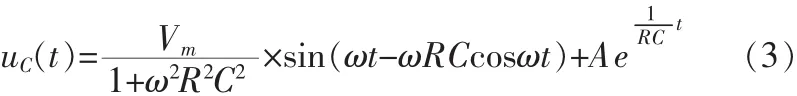

解这个微分方程可得:

其中第二项为暂态量,A为任意常数,把U|t=0时的电压值代入就可以求出A的值,因为此处考虑电路的稳定状态,所以忽略第二项。因此进一步化简后可得:

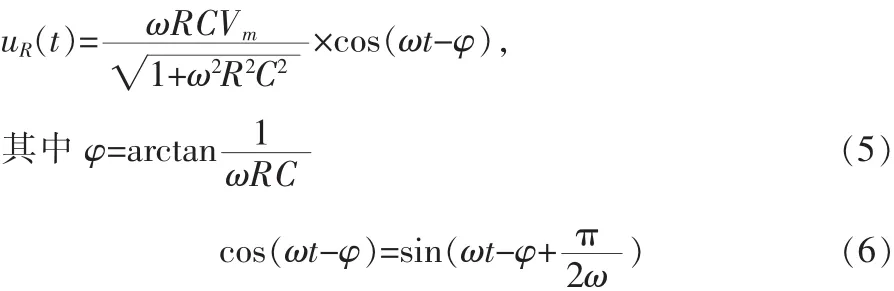

由此可以推出电路稳定状态下的电阻上的输出电压函数为:

通过此公式,然后在考虑两个齐纳二极管的和光耦的工作情况就能分析电阻上的分压和流过光耦的电流,由此就能推导出光耦的输出波形。

1.4 pSpice仿真

用 pSpice[5]仿真 79 VAC@47 Hz和 40 VAC@63 Hz的波形如图5所示。

图5 仿真图( 40VAC, 79VAC)Fig.5 Simulation( 40VAC, 79VAC)

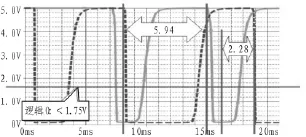

根据MCU的特性,当光耦脉冲输出低于1.75 V时为逻辑0,逻辑1则为高于3.25 V,因此根据仿真结果就可以得出在79VAC@47Hz时,逻辑0的宽度为5.94ms,在40VAC@63Hz时的逻辑0为2.28 ms。考虑一个10%的误差,则选取连接和断开的值为6.5 ms和2.5 ms。

2 软件实现

此输入接口是使用交流光耦的实现的,因此0脉冲每半个周期就会出现一次。由0脉冲的宽度决定输入的状态:如果这个脉冲足够宽,那么输入为ON状态。如果脉冲不够宽,则为OFF状态。所以当0脉冲出现时,必须检查其宽度,然后确定其0脉冲的宽度是否足够长。文中通过两级测量实现对AC数字输入状态的判断。

第1级是一个100 μs的中断,读取的输入引脚状态并且对两个计数器进行累加,其中一个逻辑1计数,另一个为逻辑0计数。这个中断只做计数,以保证对CPU的开销最小。

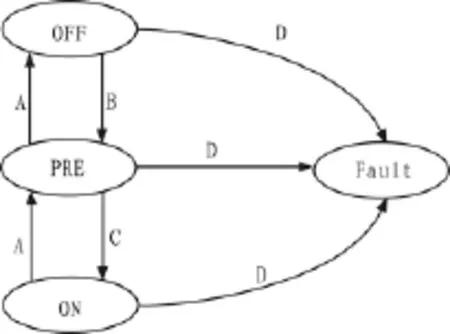

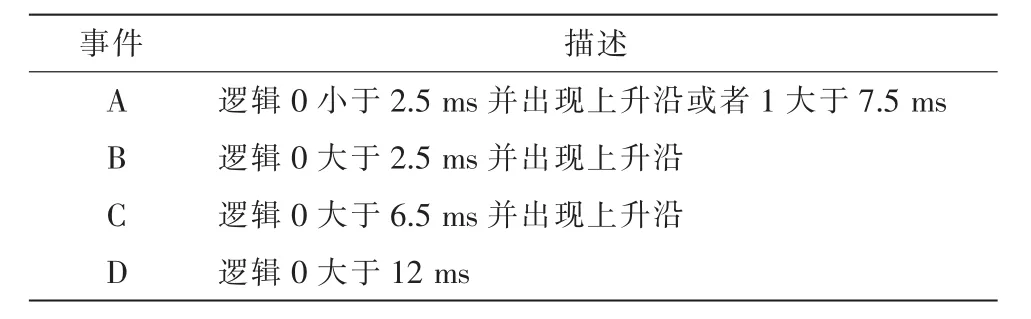

第2级是一个状态机[5],每毫秒检测一次状态。该状态机定义有3个状态:OFF,PRE和ON。

输入状态由状态机[6]的状态确定,在ON态时为开,OFF态时为关,PRE定义为保持原来的输入状态。当设备复位的时候,输入设为初始状态OFF。状态机读取输入计数器并且把它复位为0,然后使用读取的值去跟踪输入处在逻辑0或者1的时间长度,并且检查在最后的1 ms中是否出现上升沿,即:从逻辑0变为逻辑1。状态机如图6所示。

图6 状态机Fig.6 State machine

表2 事件列表Tab.2 Events list

基于时间的输入,状态转换出现在逻辑1和逻辑0并有一个上升沿。在每一个状态转换后,状态机把逻辑1和逻辑题0的定时器复位为零。如果逻辑1的时间超过7.5 ms,并且上升沿是在最后1 ms出现;和输入逻辑为0的时间小于3.7 ms,状态机往下转换,也就是从ON转到PRE或者从PRE到OFF。如果状态机处于OFF状态,逻辑1和逻辑0定时器会被复位为0,也不会发生状态转换。如果在最后1 ms出现上升沿并且输入逻辑0保持了2.5 ms或者更久,那么状态机向上转换,也就是:从OFF转到PRE,在PRE状态下,逻辑0的保持时间大于6.5 ms,则从PRE跳转转到ON。如果状态机处于ON状态,逻辑1和0定时器被复位变为0,但是此时不会发生状态转变。如果逻辑0超过12 ms,状态机会发出内部故障的标识,因为半个脉冲的最大值为10.68 ms,考虑误差阈值选为12 ms。对于逻辑0持续时间超过12 ms的唯一解释就是输入电路出现了故障。PRE状态定义为输入有个小的干扰脉冲,而不至于导致状态变化的一个保持状态。

3 结束语

此设计的优点主要是把传统的电阻分压实现采样转换成了阻容分压的方式实现,通过判断逻辑0的宽度来决定确定输入的状态,有效提高了干扰能力。这样产品在使用中大大减少了功率,提高了抗干扰能力,达到了设计要求,多年的使用中也证明了其低功耗和可靠性的特点。

[1]IEC 61131-2 Programmable controllers-Part2:Equipment requirements and tests[C]//Second edition,2003:31-35.

[2](美)尼尔森(Nilsson,J.W.)等著,张民 改编 电路分析基础[M].北京:电子工业出版社,2007.

[3]郑君里,应启珩,杨为理.信号与系统[M].2版.北京,高等教育出版社, 2000(2001重印).

[4]同济大学应用数学系.高等数学[M].5版(下册).北京:高度教育出版社,2002.

[5]李世琼,宗伟.基于PSpice的电路计算机辅助分析[M].北京:中国电力出版社,2007.

[6]杨刚.基于状态机的嵌入式系统开发[M].北京:清华大学出版社,2010.