视频信号低压差分转换的实现

2012-09-17柏化春朱晓青彭传伟

柏化春,朱晓青,彭传伟,邱 丽

(湖南工业大学 电气与信息工程学院,湖南 株洲 412007)

随着视频技术的发展,特别是高清视频技术的突飞猛进,使得视频数据信息量不断增大,同时,在高速率视频数据信号处理的要求下,视频传输变得日益关键。目前,大多数视频传输的是基于RS-232/422标准的信号,这类信号在传输时存在工作电平较高、功率损耗较大、传输速率较慢、对噪声的抗干扰性较弱等不足之处,而低压差分信号传输(low voltage differential signaling,LVDS),信号在传输中正好解决了这些不足之处[1]。因此,视频信号的低压差分转换研究就非常有意义。

1 LVDS的工作原理和特点

1.1 LVDS简介

LVDS是一种低压差分信号接口技术[2],传输数字形式的低压差分信号。它是美国国家半导体公司为解决以TTL电平方式传输宽带、高速率数据时功耗大、EMI大等难点而研制的一种数字视频信号传输方式。

LVDS输出接口利用电压摆幅(约350 mV)非常低的数字信号在2条PCB走线或1对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。采用LVDS传输数据,可以使信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输。又由于这种信号传输方式采用了低压和低电流驱动方式,因此它实现了信号数据传输的低噪声和低功耗。目前,LVDS输出接口在17英寸及以上液晶显示器中得到了广泛的应用。

1.2 LVDS工作原理

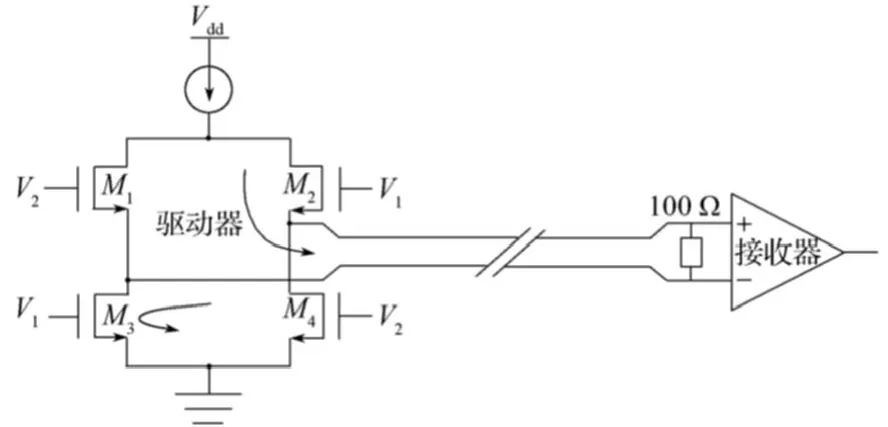

LVDS的工作原理图[3]如图1所示,它由驱动器、双绞导线和接收器3部分构成。驱动器中含有1个标称值为3.5 mA的电流源,而接收器则在接收端口匹配1个阻值为100的终端电阻[4]。当低压差分信号传输时,由于接收器的收入阻抗很高,故整个电流实际上全部流经100 Ω终端电阻,于是在接收器的匹配电阻两端产生了350 mV标称值的电压[5-6]。接收器输入端的阈值可以确保为100 mV或更低,可在0~2.4 V的共模范围内保持这样的灵敏度水平。这种组合的噪声抗干扰能力出色,对驱动器和接收器之间共模信号漂移的容忍度也会增强。当驱动器翻转时,改变流经电阻的电流方向便可在接收器输入端形成幅值大小相等而极性相反的电压,因此,以这种方式来产生逻辑1和0,从而形成低压差分信号。

图1 LVDS工作原理图Fig.1 The operating principle of LVDS

1.3 LVDS工作特点

LVDS传输250~450 mV范围内的低压差分信号,是一种低摆幅的差分信号技术。该技术使信号能在差分PCB线对或平衡电缆上以几百Mb/s的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗[7]。同时,由于LVDS驱动器和接收器不依赖于特定的供电电压,因此很容易应用到低压供电的系统中去,并保持稳定性能。LVDS的低摆幅驱动信号实现了高速信号传输并减小了传输设备的功率消耗,差分信号的低压摆幅能够使得信号噪声边缘和功率消耗大幅减少。功率消耗的大幅降低允许在单个集成电路上集成多个接口驱动器或接收器。故LVDS为当今和未来的高带宽数据传输应用提供毫瓦每千兆位的方案。它在提供高数据传输率的同时会有很低的功耗,另外它还有许多其他的优势:

1)信号低噪声;

2)对低电压电源具有好的兼容性;

3)对高噪声有很强的抑制能力;

4)信号传输的可靠性高;

5)能够很好地集成到系统及IC内。

2 系统设计方案

2.1 视频信号的数字化处理

由于LVDS传输的是数字信号,而系统输入的是PAL制视频模拟信号,因而需要对模拟信号进行数字化处理。本方案选择PHILIPS公司生产的增强型视频输入处理芯片SAA7111A。SAA7111A是两通道模拟处理电路的组合,其功能包括信号的选择,假频滤波器,模拟和数字转换器,自动钳位以及增益和增益控制,时钟发生器,视频多标准解码器,亮度、对比度、饱和度控制电路,颜色空间矩阵以及27 MHz的场消隐间隙数据分流。SAA7111A是纯3.3 V工作电压的CMOS电路集成芯片,输入模拟信号,输出数字信号,是一款用于桌面式视频的高度集成芯片。其主要特点如下:

1)能自动检测50 Hz/60 Hz场频,并支持NTSC和PAL制自动转换,还可对输入视频信号的亮度和色度进行处理;

2)拥有4路复合视频(CVBS)或2路S视频(Y/C)模拟输入,能够对内部信号源进行选择;

3)具有I2C总线控制功能,能对27 MHz场消隐间隙数据分流进行调整;

4)对于不同的视频格式,都要求芯片外部有一个24.576 MHz的晶振;

5)支持4:2:2(16位)、4:2:2(8位)、4:1:1(12位)YUV输出格式,或8:8:8(24位)、5:6:5(16位)RGB输出格式;

6)64引脚的LQFP封装,功耗小于0.5W。

本系统选用了1路视频输入,16位RGB565格式的数字视频信号输出。

2.2 SAA7111A的寄存器配置

视频专用解码芯片SAA7111A提供了I2C总线接口标准,其写地址为48H,读地址为49H。SAA7111A内部有32个控制寄存器,其中22个可编程设置。系统中使用单片机AT89C51通过I2C总线对SAA7111A芯片内部的32个寄存器进行设置,从而完成对SAA7111A的初始化配置,以实现模拟输入、颜色空间模式、固定增益、行同步、场同步、亮度、对比度等控制功能。

2.3 LVDS编码模块设计

LVDS编码模块选用美国National Semiconductor公司生产的LVDS编码芯片DS90C383。DS90C383是一款功能强大的并串转换发送芯片,能将最多24位的并行视频数据转换为符合LVDS接口标准的串行差分信号输出。DS90C383支持20~65 MHz的像素时钟,每秒传输数据量高达1.8 Gb/s,所传输数据符合TIA/EIA-644 LVDS标准。因其抗干扰力强、传输距离远,被广泛应用于工业、通信、军事等领域。本方案中选用27 MHz,16位的并行视频数据输入。需要注意的是,根据VESA标准,在实际应用过程中,只有当有数据需要传输时才能给DE高电平使能,而没有数据传输时要使DE保持低电平,这样才能使传输的视频信号在液晶显示器上正常显示。

3 硬件电路的实现

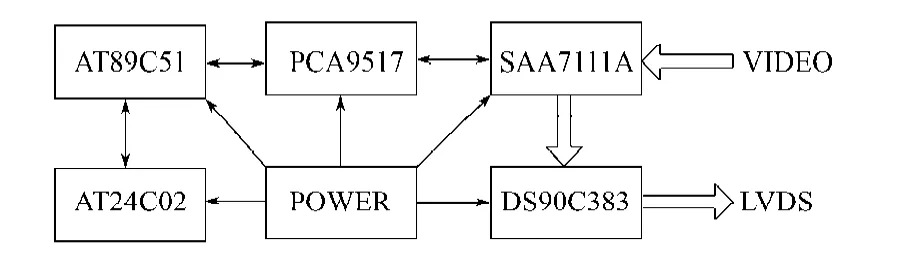

本系统的硬件结构框架如图2所示。其中SAA7111A是信号转换单元,它将输入PAL制模拟视频信号转换成RGB565格式的数字视频信号,传输给DS90C383,通过DS90C383进行并窜转换,最后编码成低压差分信号。由于SAA7111A需要根据不同的视频信号源配置寄存器参数来调节数字信号的产生,故本系统采用了AT89C51对SAA7111A进行参数配置。同时,考虑到视频信号属于高频信号,所以在AT89C51和SAA7111A之间加入1个缓冲器PCA9517。为了使系统在掉电后再上电能立马进入稳定的工作状态,在AT89C51之前加入了一个EEPROM芯片AT24C02,对配置参数起到了存储保护作用。

图2 系统硬件结构框图Fig.2 The structure of system hardware

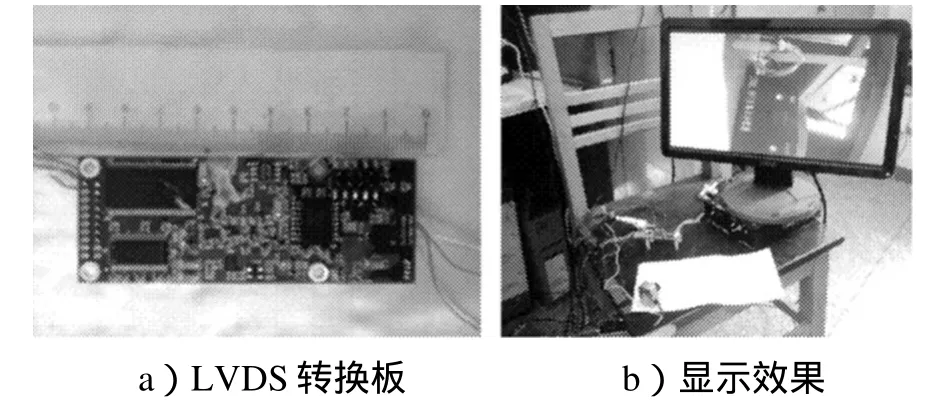

通过对开发的硬件电路进行调试,排除硬件电路故障后,对编写的各个程序进行了实验验证。实验过程中,为了查看实际显示效果,使用了长沙景佳微公司提供的LVDS-DVI视频转接盒,从而将LVDS视频信号转换成DVI数字视频信号后通过带有DVI接口的显示器输入显示。图3给出了开发的硬件电路和实验结果,其中a图为开发的视频信号LVDS转换板,b图为经调试的实际显示效果。

图3 硬件电路和实验结果Fig.3 The hardware circuit and experimental results

4 结语

LVDS技术作为一种新颖、有效的接口技术,其高速、低功耗、低噪声、低成本等优良特性,为解决当下数据传输的瓶颈问题提供了可能,特别是在视频图像传输中的应用得到了广泛的发展。本系统已在某航空研究所的视频传输中得到应用,并且获得了理想的传输效果。

[1]Xu Jian,Wang Zhigong,Niu Xiaokang. Design of High Speed LVDS Transceiver Ics[J]. Journal of Semiconductors,2010,31(7):075014.1-075014.5.

[2] 李 宏,李 蒙,哈 乐,等.基于FPGA的高速链路通信系统实现[J].电子测量技术,2006,29(5):118-121.Li Hong,Li Meng,Ha Le,et al. High-Speed Link Communication System Implementation Based on FPGA[J]. Electronic Measurement Technology,2006, 29(5):118-121.

[3]National Semiconductor,LVDS Group. LVDS Owner,s Manual[S]. National Semiconductor Corp., 1997:107-109.

[4] Thaddeus J. On-Chip Terminating Resistors for High Speed ECL CMOS Interfaces[J]. IEEE Journal of Solid States Circuits, 1992, 20(4):292-295.

[5]Ahn Seungyoung, Lu A C W, Wei fan, et al. Solution Space Analysis of Interconnects for LVDS Applications[J]. Electrical Performance of Electronic Packaging, 2001, 2 (42):327-330.

[6]Boni A, Pierazzi A, Vecchi D. LVDS I/O Interface for Gb/-Per-Pin Operation in 0.35 CMOS[J]. IEEE Journal of Solid State Circuits, 2001, 36(4):706-711.

[7] Mechaik M M. An Evaluation of Single Ended and Differential Impedance in PCBs[C]//International Symposium on Quality Electronic Design.SanJose :conference publicafions, 2001:301-306.