一种基于FPGA的通用雷达回波实时模拟器

2012-09-15孟庆虎陶青长梁志恒

孟庆虎,陶青长,梁志恒,朱 宁

(1.凯迈(洛阳)测控有限公司,河南 洛阳 471009 2.清华大学 精密仪器与机械学系,北京100084 3.清华大学 精密测试技术及仪器国家重点实验室,北京100084)

一种基于FPGA的通用雷达回波实时模拟器

孟庆虎1,陶青长2,3,梁志恒2,3,朱 宁2,3

(1.凯迈(洛阳)测控有限公司,河南 洛阳 471009 2.清华大学 精密仪器与机械学系,北京100084 3.清华大学 精密测试技术及仪器国家重点实验室,北京100084)

提出了一种基于FPGA的雷达回波实时模拟器的实现方法。该模拟器采用cPCI标准总线,以FPGA为核心计算单元,配有高速数模、模数转换模块,可实现雷达回波信号实时在线注入模拟。该模拟器可实现多种体制下复杂回波的模拟,具有很好的工程应用价值。

雷达回波模拟器;FPGA;并行处理

雷达回波模拟器能够在实验室环境下模拟产生雷达实际工作中所接收到的回波信号,在雷达系统设计、调试、测试、训练和维护等工作中发挥着不可替代的作用[1-3]。随着电子技术的日益进步,雷达系统正在向多模式、多通道、高分辨等方向发展,对模拟器的通用性、实时性等指标提出了更高的要求[4]。

模拟器通常可以分为软件模拟、硬件模拟及软硬结合等三种实现方式。软件模拟具有成本低、灵活性强等优点,但实时性差,一般不能直接用于雷达系统的实时调试和测试[5]。硬件模拟通常采用波存储回放技术,实时性好,但通用性差,不能满足参数复杂多变的情况[6-7]。软硬结合方式以通用计算机为主控平台,以高性能嵌入式处理器为运算单元,在具有良好实时性的同时,能够适应复杂的仿真环境,是应用最为广泛的模拟方式[5,8]。

FPGA作为高性能数字信号处理系统中的关键器件,在雷达信号模拟中有着巨大的开发潜能[9-11]。然而,受制于开发难度与开发周期,在传统的模拟器中,FPGA多用于逻辑功能、时序信号和对外接口的控制,其强大的并行处理能力没有得到充分利用。

本文以FPGA为核心构建了一种通用的雷达回波信号实时模拟系统。该系统采用FPGA作为回波信号模拟的运算单元,充分利用了FPGA资源丰富、并行处理能力强的特点,提高了系统的实时性;采用System Generator开发回波模拟程序,大大降低了开发难度,并显著缩短了研制周期。采用标准工业总线及模块化设计,通用性、兼容性和可扩展性强,可以应用于不同体制、不同规模的雷达系统模拟中。

1 系统方案

通用雷达回波实时模拟器(以下简称“模拟器”)由上位机、微波链路和回波模拟单元组成,系统框图如图1所示。上位机实现人机交互、系统控制、状态监视等功能。微波链路包括下变频和上变频模块,用于实现射频信号与中频信号的转换。回波模拟单元完成中频信号采集、数字下变频(DDC)、目标模拟、杂波模拟、干扰模拟、数字上变频(DUC)和数模转换等操作,是整个系统的核心模块。

图1 模拟器系统框图

模拟器遵循标准结构规范,采用cPCI标准总线,可根据实际需求扩展系统规模,为工程应用提供了便利。为了适应不同速率、不同类型的信号传输,系统内部采用多种互联方式。PCI总线用于传输控制命令及慢速信号,自定义总线用于高速数据流的传输,同步定时总线用于系统的时序控制,如图2所示。

图2 模拟器内部互联方式

作为模拟器的重要组成部分,回波模拟单元以高性能FPGA为核心构建,用于实现DDC、回波模拟、DUC等功能;同时配以高速A/D和D/A芯片,用于信号采集与回波信号的播放。回波模拟单元由多块信号处理板组成,单板的逻辑框图如图3所示,FPGA采用2片Xilinx公司的XC6VLX240T。芯片采用40 nm技术,密度高、功耗小,片上具有丰富的逻辑和I/O资源,并集成了大量的信号处理单元(DSP48E),能够满足复杂的回波模拟运算及对外接口的需求。两片FPGA通过自定义互联接口实现高速数据通信,用于传输中间结果。ADC采用ADC08D1500,最高采样率可达1.5 GHz,可以满足中频宽带信号的采样要求。DAC采用ADI公司的AD9736,最高时钟频率为1.2 GHz,具有良好的输出信号性能。

2 FPGA模拟软件设计与实现

雷达回波信号是目标回波、杂波、干扰以及噪声等叠加后的结果。不同的雷达体制,对目标、杂波、噪声及干扰的建模方法有所不同。对于雷达导引头,可以仅考虑单点目标,只需模拟目标的速度、加速度、距离和功率等信息即可。对于复杂的高分辨雷达系统,则要求模拟器能够更为细致地模拟目标回波信号,如动目标、一维距离像及面目标等。

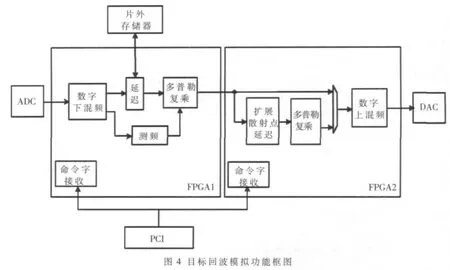

图4给出了目标回波模拟软件的功能框图。该软件可以模拟点目标以及扩展目标的回波信号。中频输入信号在完成DDC后作为回波模拟的基带基准数据,同时用于确定波门和载频。多普勒计算模块根据设定的目标运动信息及测频结果计算每个目标的多普勒频率。波门信息与目标延迟信息相结合,用于确定回波信号的位置。复乘模块在基准数据上加入延迟、多普勒调制和幅度调制后得到基带回波数据,再经过DUC后通过DAC播放,即可得到中频回波数据。

由于信号处理板卡具有2片FPGA,因此需要将上述各运算模块分别映射到相应的FPGA中。如图4所示,第一个FPGA实现数字下混频、测频、延迟复乘等功能,第二个FPGA实现扩展散射点延迟、各点相对多普勒复乘、数字上混频等功能,产生一个简单目标或一个扩展目标。为了降低开发难度、缩短开发周期,运算模块均采用System Generator开发。

图3 信号处理板组成框图

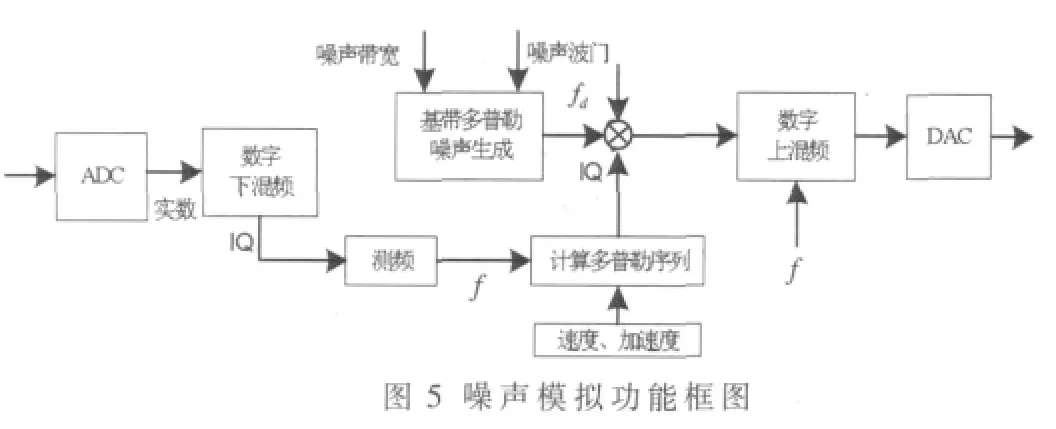

噪声模拟的实现方法如图5所示。首先产生高斯白噪声随机序列,FFT后根据噪声带宽进行加窗,得到噪声序列的频谱,然后做IFFT,得到时域模板序列。对这个模板序列进行随机移位叠加,最后根据测频结果进行DUC,将噪声移到一定的载频上。根据实际噪声带宽的需求,可以选择不同宽度的窗函数,控制调频噪声的带宽。

杂波/箔条干扰信号模拟采用发射脉冲与杂波/箔条干扰数据卷积的方法进行模拟。杂波/箔条干扰数据模型由上位机计算,然后下载到海量存储板。仿真时,信号处理模块从海量存储板读取杂波/箔条干扰数据,与发射信号进行卷积,得到杂波/箔条干扰回波信号。杂波/箔条干扰信号模拟实现原理框图如图6所示。杂波/箔条干扰信号模拟通常采用3块信号处理板,配合3路微波上变频,完成和通道、方位差通道、俯仰差通道的杂波模拟。

将上述运算过程生成的目标回波、噪声、杂波和干扰信号叠加后,即可得到最终的雷达回波信号。

3 系统验证

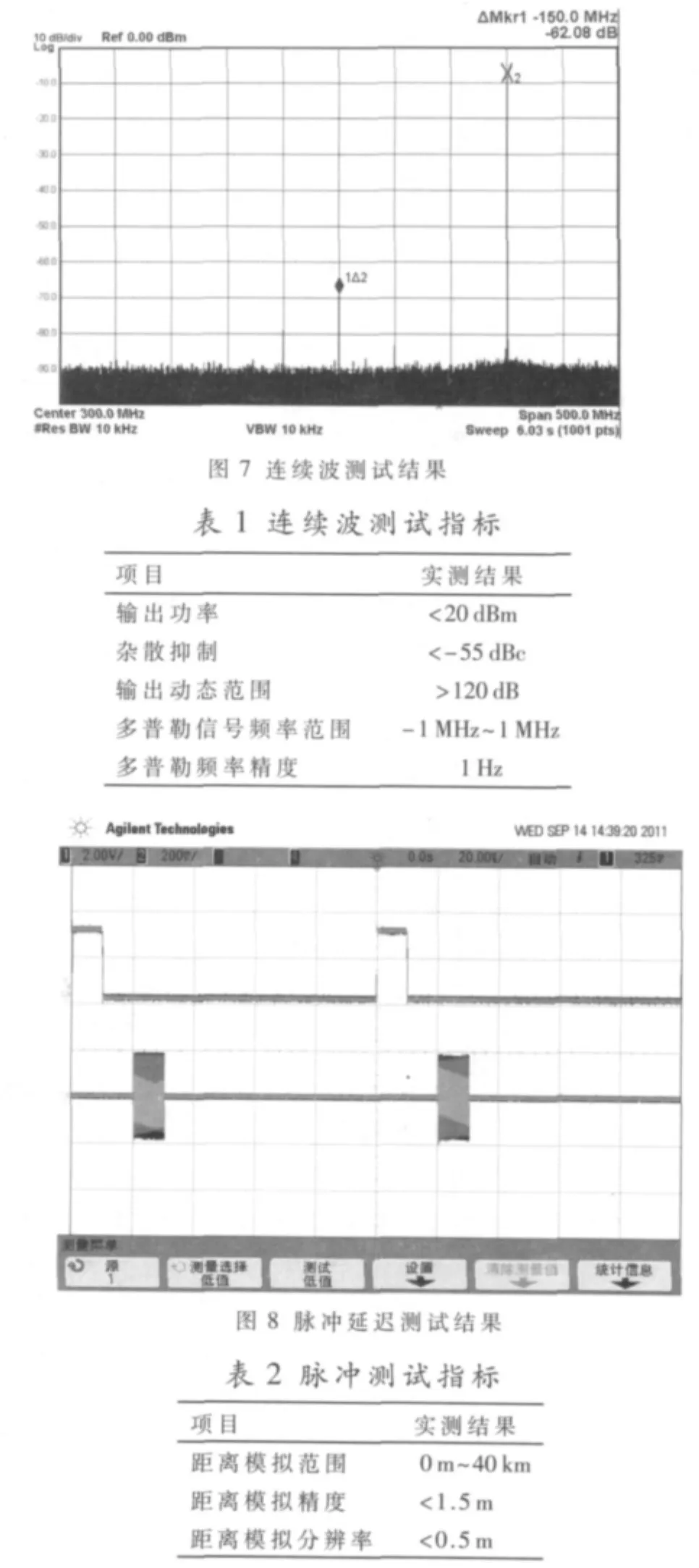

分别采用连续波信号和脉冲信号对系统的功能和性能进行测试。连续波状态下,需要测试模拟器的输出功率、杂散抑制、动态范围、多普勒信号控制性能等指标。脉冲状态下,需要测试模拟器的模拟精度、多目标及干扰模拟能力等指标。

图7给出了连续波状态下某典型频率的输出信号实测结果。可以看出,输出点频信号的频率与输入信号相差所设定的多普勒频率,杂散电平很低,满足一般雷达系统的要求。表1给出了主要指标的实测结果,包括输出功率、、杂散抑制、输出动态范围、多普勒信号频率范围与多普勒频率精度等。

图8给出了脉冲状态下的输出信号,表2给出了主要指标的实测结果。

本文介绍了一种基于FPGA嵌入式系统的雷达回波实时模拟器。利用FPGA资源丰富、并行运算能力强的优点,提高了系统的集成度与实时性;采用System Generator开发FPGA软件,大大降低了开发难度与开发周期;通过灵活配置FPGA软件,可以实现不同体制雷达回波的模拟,具有较强的通用性和扩展性。实验结果表明,该模拟器能够满足雷达系统半实物仿真的需求,其相关技术代表了雷达回波模拟器未来发展的一个方向,并可应用于其他类型的回波模拟中。

[1]MITCHELL R L.Radar signal simulation[M].Norwood:Artech House,1976.

[2]GEORGE L.Airborne radar simulation[M].Dallas:Camber Corporation,1996.

[3]ESKELINEN P,RUOSKANEN J.A baseband Doppler simulator for radar system development[J].IEEE Aerospace and Electronic Systems Magazine,2006,21(1):8-11.

[4]李世雯.雷达多目标模拟器[D].南京:南京理工大学,2005.

[5]徐安林.在线注入式相控阵雷达目标模拟器关键技术研究[D].长沙:国防科学技术大学,2009.

[6]王超,李毅,袁乃昌.高分辨雷达目标回波模拟器设计[J].系统工程与电子技术,2007,29(8):1268-1270.

[7]王江展,白雪,潘志明,等.DRFM在机载PD雷达宽带目标模拟器设计中的应用研究[J].信息化技术,2010,36(12):16-19.

[8]陈志伟.基于FPGA的线性调频脉冲压缩雷达目标视频信号模拟[D].南京:南京理工大学,2007.

[9]苗旺.基于 FPGA的雷达信号模拟器设计[D].北京:北京理工大学,2008.

[10]李俊杰,何友,宋杰.基于FPGA嵌入式系统的雷达信号模拟器[J].嵌入式技术,2009,35(10):45-52.

[11]马魁勇,于长军,位寅生.基于FPGA的雷达目标模拟器的设计与实现[J].仪器仪表学报,2006,27(6):870-872.

General real-time radar signal simulator based on FPGA

Meng Qinghu1,Tao Qingchang2,3,Liang Zhiheng2,3,Zhu Ning2,3

(1.CAMA(Luoyang)Measurements&Controls Co.,Ltd.,Luoyang 471009,China;2.Department of Precision Instrument and Mechanology,Tsinghua University,Beijing 100084,China;3.State Key Lab Precision Measurement Technology and Instrument,Tsinghua University,Beijing 100084,China)

A new method of real-time radar echo simulator is put forward.The structure is based on the standard cPCI bus with FPGA as the core computation blocks and high speed ADCs and DACs.The system is highly integrated with several function and interface blocks.It can simulate complicated echoes of different radar.The test results prove its validity and value in engineering applications.

radar signal simulator;FPGA;parallel processing

TN955

A

0258-7998(2012)03-0082-03

2011-10-31)

孟庆虎,男,1970年生,硕士,高级工程师,主要研究方向:测试与仿真。

陶青长,男,1979年生,博士后,主要研究方向:雷达信号处理。

梁志恒,男,1969年生,博士,副研究员,主要研究方向:雷达系统仿真。