一种低功耗多核心系统处理单元的自动化设计方法

2012-08-26徐术力

席 娜,徐术力

XI Na, XU Shu-li

(江西经济管理干部学院 计算机系,南昌 330088)

0 引言

随着手持型终端的普及化,多媒体应用对系统的运算需求也越来越高。传统上主要依靠提高芯片主频频率来增大运算速度,但会带来高热量,大功率的问题,相对于追求高频率的作法,多核心系统能在提升运算能力下,有效地解决功率消耗的问题,所以成为越来越普遍的设计趋势[1]。

对单一处理单元设计来说,除了处理单元本身的硬件架构设计外,还包含对应的工具链、编译器、模拟器等相关软件,这些工作往往需要耗费很长的设计和验证时间,如何快速设计一个处理单元并且能够弹性地修改,以便提供系统的架构,这是本文的探索重点。本文采用LISA的自动化处理器设计流程,快速地设计一了多核心系统的处理单元及其相关的工具,并且可提供电子系统层级(Electronic System Level;ESL)的架构探索,以符合各项不同的开发需求[2]。

1 LISA自动化设计方法和PACDSP

图1 LISA自动化设计流程

Synopsys CoWare LISATek[3]处理器的自动化设计方法基于LISA 2.0(Language for Instruction Set Architecture;LISA)架构描述语言[4],LISA 2.0提供的一正规的描述语言,对于处理器的发展,可缩减设计初期的指令集描述和后期RTL设计之间的距离障碍。除此之外,也可以支持多种不同抽象层级的描述以便提供不同发展需求使用,比如指令层级的处理器提供快速程序开发,而周期层级的描述提供架构探索使用。如图1所示,完成LISA的指令架构描述后,可经由Processor Designer及Compiler Designer的自动化开发工具产生该处理器的工具链、编译器、模拟器,并且配合应用软件进行除错和分析,进一步探讨是否符合设计规格和目标,若未能符合,则可返回到LISA描述快速地修改并且自动化产生对应的设计,保有设计上的高度弹性;反之,若设计已达到目标,则可再产生对应的相关设计提供发展,像是系统层级模型或是RTL设计继续后续的系统整合。

PACDSP (Parallel Architecture Core DSP)是台湾的工研院资通所开发的数字信号处理器,在设计上采用高性能的VLIW架构,并且支持强大且多元的指令集,可满足各种高阶多媒体应用需求。除了以PACDSP为基础,继续发展双核心甚至四核心的SoC平台外,本计划也朝低功率消耗的处理单元(PAC-Lite)设计的目标前进,期望借助这一个轻量化的处理单元实现多核心的系统架构发展。

2 PAC-Lite的自动化设计

本节,我们将说明如何利用LISA的自动化流程设计一个PAC-Lite处理单元及其工具链,并且在设计中,采用两种不同抽象层级的描述,进行周期层级精准(Cycle-Accurate ;CA)和指令层级精准(Instruction-Accurate;IA)的模型设计,以便供不同需求使用。

2.1 处理单元架构设计

PAC-Lite基于PACDSP的scalar单元,修改为一个32位处理单元,采用常见的5级管线架构,并且根据PACDSP的多媒体应用分析,支持常用的42个基本指令和6个乘法相关的指令,运算上可支持32个一般用途的寄存器,并且搭配8个预测寄存器作程控用。接下来将介绍如何使用LISA设计该一个处理单元。

首先,LISA描述设计可以分成两个部分,资源部分和运算部分。在资源描述中,必须描述处理单元的各种储存装置,包含寄存器、内存、管线内存和内部状态等,如图2所示,在资源描述中,描述设计PAC-Lite 的一般寄存器(R0~R31)、预测寄存器(P0~P7)、管线寄存器和内部状态等。除此之外,在资源描述部分还需有内存等其他的设计描述,如此才可提供下列运算部分使用。

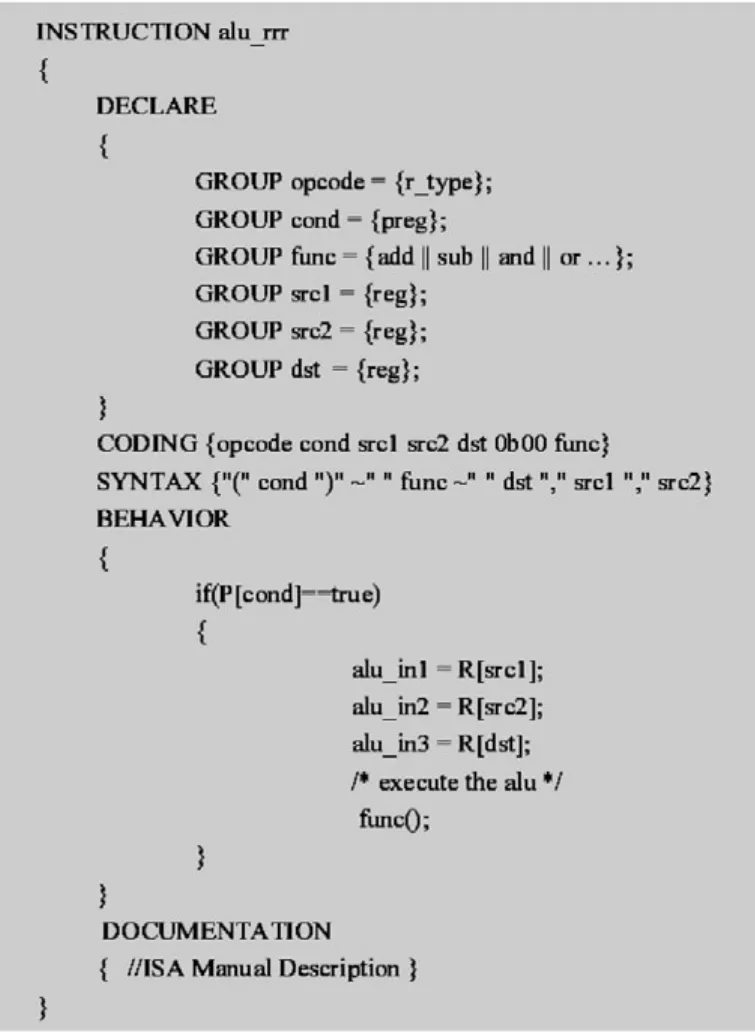

除了上述资源描述外,接下来将介绍运算部分,该部分的目的是针对指令集的相关信息进行描述,如图3所示,以ALU的指令为例,LISA描 述 包 含 DECLEARE 、CODING、SYNTAX、BEHAVIOR和DOCUMENT五个项目,CODING和SYNTAX中表示该指令的编码和指令语法,作为编译器产生的用,在此PAC-Lite采用固定长度的32位编码,语法上也和常见的组合语言格式相似,通过该种描述方法,可快速地由开发者进行任意的编码尝试达到探索的目的。接着,DECLEARE和BEHAVIOR中描述指令的实际运作行为,包含数据搬移或是逻辑数学运算,这一项目的描述可作为模拟器和高阶模型产生使用,BEHAVIOR指令行为描述可通过以C/C++为基础的描述语言,轻易地完成各种复杂指令的行为以符合各种应用软件开发需求,借助快速的增减指令达到性能评估的目的。最后则是DOCUMENT的描述,用以产生ISA指令集手册。

图2 LISA设计描述(Resources)

图3 LISA设计描述(IA-based Operations)

上文介绍了LISA在运算部分的描述方法,属于IA的设计介绍,用以产生IA的模拟器和高阶模型,适合软件快速开发使用。除此之外,本次设计中也使用CA的设计以符合架构探索的使用,如图4所示,同样以一个ALU运算指令为例,相对IA的描述,在CA的LISA设计上就显得复杂许多,首先必须将该指令所经过的管线一一描述,分别独立设计将该级管线内的行为,以该例来说,分别描述解码、执行和写回三级管线的运作行为,并且通过ACTIVATION中的描述将其指令在管线的顺序串连起来,如此便可完成一个CA的LISA设计模型。

完成的LISA模型通过Processor Designer工具自动化产生Assembler、Linker和Simulator,同时也可通过Software Package Generator工具自动化将指令模拟器整合一个SystemC Wrapper的高阶模拟模型,可供ESL开发分析使用。

图4 LISA设计描述(CA-based Operations)

2.2 C Compiler设计

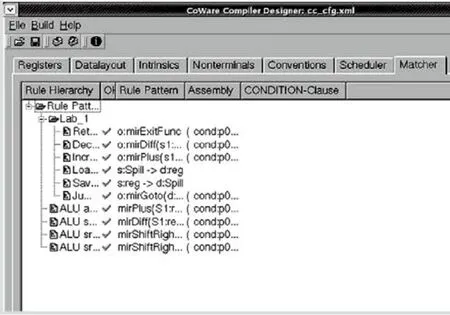

除上述介绍的处理器架构设计外,LISATek还包含另一个自动化工具,称为Compiler Designer。该工具主要是让用户在设计处理器架构的LISA描述后,快速地辅助设计对应的C Compiler,并且进行各项高阶编程语言的开发验证。Compiler Designer的设计分成两步,首先,必须将PACLite架构设计的寄存器、支持的数据形态、排序时的延迟以及基本内部函数一一填入工具的对应格式中,该设计描述辅助Compiler了解并支持可使用的各种资源和排序根据。接着进行比对器设计,可以视为Compiler的核心,包含程序设计中的各项比对规则,负责在C程序转换为组合语言的过程中选取对应的指令编码及算子。

图5为PAC-Lite的比对器的设计实例,在此例中,我们填入的规则包括堆栈指标的操作规则、函数调用时寄存器的备份规则、以及部分ALU运算的指令规则。完成描述设计后可通过完整性检查先行测试填入的规则是否有语法的错误,若无则可开始自动化构造C Compiler。

图5 Compiler Designer - Matcher规则设计

借助该工具,可帮助开发者快速地开发一个新处理单元的C Compiler,和传统手动修改GCC的方法相比,可大幅地缩短开发时程及减少相关人力。再者,若配合应用软件的开发模拟未能达到需求的性能目标,也可快速地新增指令并加入对应的比对规则就可以构建新的C Compiler。但是,使用该工具必须熟悉Compiler Designer的操作及描述语法,且部分对应的周边未能提供自动化产生,必须手动修改,

3 结论

本文介绍如何使用LISA的自动化设计流程,设计并自动化产生一个PAC-Lite的处理单元的相关工具链、编译器、模拟器和高阶模型等,并且配合不同抽象层级的设计,提供不同阶段的开发需求。并应用PAC-Lite的处理单元整合一个CIS视频传感系统,搭配互连架构及各项周边设计,在高阶电子系统层级达到软件开发和架构探索的目的,探索的结果将辅助将来快速且有效地设计一个低功耗的多核心系统。

[1]刘培生, 缪小勇. 一种多芯片封装(MCP)的热仿真设计[J]. 计算机工程与科学, 2012, 34(4): 2278-2282.

[2]王伟, 高晶晶, 等. 一种针对3D芯片的BIST设计方法 [J].电子测量与仪器学报, 2012, 26(3): 2278-2282.

[3]李政, 张盛, 等. 一个低功耗1G-samples/s,6-bit折叠插值ADC芯片设计[J]. 电路与系统学报, 2011, 22(8): 1699-1713.

[4]张琰, 等. 一种高集成度基于PCI总线的AM80486CPU设计与实现[J]. 电子技术, 2011, 12(2): 384-387.