“电工学”课程中FPGA内容的教学探索

2012-08-23范秋华

范秋华,宫 玥

(青岛大学自动化学院,山东青岛 266071)

数字化是信息社会中电子产业发展的必然趋势,数字电子技术在电工学中占有重要地位,近年来FPGA(Field Programable Gate Array)技术作为数字电子技术的现代部分,已经引入到电气信息类本科教学中。FPGA具有高度的灵活性、并行性、开发周期短等特点,与ASIC相比有极大的优势,而且大量IP核的使用,缩短了产品的开发周期,使得企业更加具有市场竞争力,FPGA技术在未来会有极大的作为。目前,为满足高等学校本科非电类各专业学生学习的需要,应该在电工学课程加入FPGA内容。

1 FPGA硬件原理

理解FPGA硬件原理,要先理解可编程逻辑器件PLD(Programable Logic Device)的原理,最基本的可编程逻辑器件的就是PROM,任何一个逻辑函数都可以写成最小项的和的形式,PROM中的地址端当做输入变量,那么地址译码器的输出就是输入变量的所有最小项,通过或阵列编程就可实现任意组合逻辑函数,加上触发器即可实现时序逻辑函数。PROM是只有或阵列编程,与阵列、或阵列同时编程就是PLA(Programmable Logic Array),只有与阵列编程、或阵列不编程叫 PAL(Programmable Array Logic),这些都还没有实际产品。GAL通用逻辑阵列(Generic Array Logic)是从PAL发展过来的,是一种电擦除可重复编程的可编程逻辑器件,具有灵活的可编程输出结构,使得为数不多的几种GAL器件几乎能够代替所有PAL器件和数百种中小规模标准器件。而且,GAL器件采 用先进的EECMOS工艺,可以在几秒钟内完成对芯片的擦除和写入,并允许反复改写,为研制开发新的逻辑 系统提供方便,因此,GAL器件得到了广泛的应用。EPLD(Erasable Programmable Logic Device)的基本结构与GAL并无本质区别,但其集成密度比 GAL高得多,使其在一块芯片内实现更多的逻辑功能 ,CPLD(Complex Programmable Logic Device),增加了内部连线,改进了内部结构体系,因而比EPLD性能更好,设计更加灵活,其发展也非常迅速。所有这些都是基于乘积项技术,EEPROM(或Flash)工艺的称为PLD。

FPGA是可编程逻辑器件的一种。基于查找表技术,SRAM工艺的称为FPGA查找表简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

FPGA的基本原理,发展历程,可放到半导体存储器这章,结合ROM实现函数的内容讲解,占用时间不超过0.5个学时。

2 编程语言软件环境

要用FPGA实现数字系统,就是在一定环境下使用硬件描述语言编写程序,经编译、仿真正确后下载到可编程逻辑器件上去实现。硬件描述语言有两种标准VHDL和Virlog-HDL,作为IEEE的工业标准,在电子工程领域,已成为事实上的通用硬件描述语言。有专家认为,在新的世纪中,VHDL与Verilog语言将承担起大部分的数字系统设计任务。介绍语言就是介绍基本语法规则,VHDL和Verilog两种介绍一种即可,大约花3到4个学时即可,可以放在门电路后讲解。

可编程逻辑器件目前主要是Altera、Xilinx、Lattice三大公司。三个公司使用的软件环境是不同的,Altera公司使用QuartusII软件,Xilinx使用ISE开发环境,Lattice是Isplever软件。可以分别从各自公司网站下载学生版免费使用。各软件环境都支持原理图、VHDL语言和Verilog语言文本文件,以及波形EDIF等格式化的文件作为设计输入。

3 使用举例

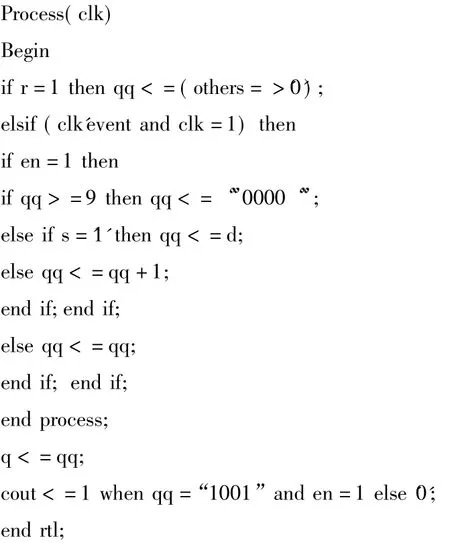

1)在传统数字技术中设计一基于触发器的十进制计数器,要用四个触发器,化状态转换图,写卡诺图,用触发器实现出来,非常麻烦,而用VHDL语言可以来写就格外简单其结构体程序如下:r异步清零端,s端,en同步使能端都是高电平有效 ,d数据输入端 ,q数据输出端,cout:进位输出端

从图1所示的仿真波形上可以看到:r异步清零端有效时输出q为0(左边第一条红线处);r无效时,s同步置数端,en同步使能端有效进行置数先是置零(左边第二条红线处),接着置3.开始计数(左边第三条红线处)。当r,s都无效时开始计数从0到9循环,每到9时,进位输出端输出一个时钟周期的高电平。上面程序简单,但稍加修改就可以改为任意进制计数器。

图1 异步清零同步置数的10进制计数器仿真波形

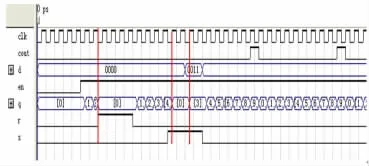

2)各软件环境都支持原理图设计,凡是涉及数字电子的芯片都有。如设计一个30进制计数器,用中规模芯片两片160可以实现,仿真如图2所示。

图2 用74160级联构成30进制计数器原理图

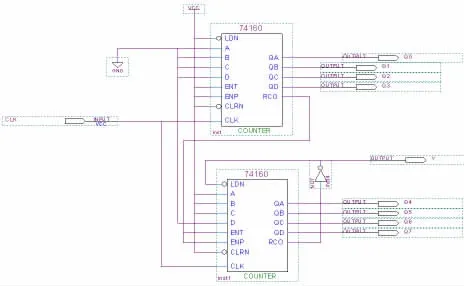

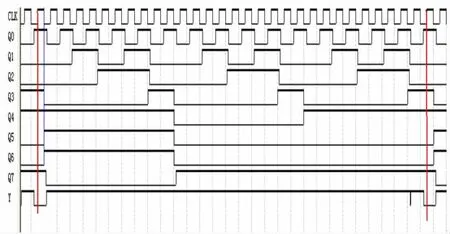

图3仿真与图1仿真有些区别,图1用的是功能仿真,不考虑器件延时,图3用的是时序仿真,考虑到具体器件的延时。

图3 30进制计数器仿真波形

通过观察可以看出,该仿真波形完全符合30进制计数器的逻辑功能。在软件下进行综合,可以得到该计数器的逻辑符号,当其他的设计工作中需要用到计数器时,可以直接调用此元器件,不必重新设计,简化了设计工作。其实也是可编程逻辑器件中的IP核及参数可设的宏功能器件的应用。

4 结语

使用FPGA技术设计数字系统时将数字电子技术中难以实现的硬件设计转换为软件设计,学生应用EDA技术除了可以实现小规模的电子电路设计,还可以通过对CPLD,FPGA编程,设计复杂的电路系统。用软件代替硬件通过FPGA技术实现数字电路设计,实现了硬件电路软件化。

在日常生活中,数字电路随处可见,这就要求理论教学必须与实践教学相结合,达到理论联系实际的目的。学生并不能很好地将理论与实际联系起来,特别是当学生设计好电路进行实验时,经常出现与他们自己分析的理论结果不一致的现象。如果单纯的进行理论讲解,难以让学生理解清楚。通过对仿真波形的分析,学生能够比较形象地理解“异步清零”的工作过程,也能够解释在实验过程中所观察到的实验现象。

“数字电子技术”课程是一门实践性很强的课程,它主要是为学生今后从事电子设计打好基础。如果学生没有机会进行实际操作,就无法进行电子设计,更谈不上设计好电路。

使用FPGA技术,相当于将数字电子技术实验箱搬移到电脑上,学生可以根自身的情况,依托软件平台,结合所学习的内容,及时地进行接近于实际电路的设计、仿真和分析,加深对理论的理解。若仿真结果不正确,学生可以在电脑上修改电路,不会造成硬件资源的浪费。当仿真结果完全正确时,学生就可以非常放心地进行实际电路的搭接和使用,这一过程可以将理论与实际真正联系起来。通过这个开放的随身的数字电子技术实验室,可以提高学生的创新能力和综合素质。

可以使学生不拘泥于只有靠“芯片+连线”才能设计数字电路的想法,开阔了学生的设计思路。通过EDA工具对电路进行仿真,教师可以对学生难以理解的电路现象进行直观的讲解,加深学生对理论知识的掌握。同时,引入EDA技术,可以使学生有更多的机会动手设计电路,验证自己的想法,激发了学生的热情,为设计复杂的数字系统打下基础。

[1] 潘松等.EDA技术实用教程(第三版)[M]北京:科学出版社,2006