一种积分时间可调型线阵CCD的改进驱动方案*

2012-08-15付天舒王立刚

付天舒,刘 强,王立刚

(1.东北石油大学 电子科学学院,黑龙江 大庆 163318;2.哈尔滨工程大学 理学院,黑龙江 哈尔滨 150001)

引 言

线阵CCD是一种自扫描成像器件,其在非接触测量方面应用十分广泛。线阵CCD的驱动是整个测量系统的基础,其涉及到系统的稳定性。线阵CCD的驱动方案有很多种,其中最具优势的是FPGA/CPLD(field programmable gate array现场可编程门阵列/complex programmable logic device复杂可编程逻辑器件)驱动方式,现在FPGA和CPLD的开发成本不断下降,技术指标和芯片内部资源不断提升,无论是对于实验室科研,还是工业专用集成电路的前期设计,都是合适的驱动方式[1-2]。

以往对这种积分时间可调型线阵CCD进行驱动,在输入方式上大多使用原理图输入法,在驱动时序上通常是使用芯片供应商所提供芯片手册上的两种驱动时序。采用原理图输入方式有两个缺点:一是当测量系统预先要求电路时序精度非常高时,原理图输入方式很难满足精度要求,必须进行反复的调试才有可能达到设计要求;二是当测量环境等因素改变或测量目标改变时,使用原理图输入方式进行时序调整会很繁琐,不利于程序移植。在驱动时序上使用传统的两种驱动时序也有各自的缺点,第一种驱动时序的积分时间是同行扫描周期关联的,当行扫描周期确定时,积分时间就不能再进行调整,减少了时序控制的灵活性;第二种驱动时序虽然解决了第一种驱动时序的问题,但时序计算比较复杂,并且在光积分电极的低电平区,转移脉冲有严格的时序要求,这又给程序移植带来了麻烦。现根据线阵CCD光积分控制栅的工作原理,提出了一种新的时序工作方式,在光积分电极的低电平区附近,对转移脉冲的时序加以改进,并在输入方式上采用硬件描述语言方式,解决了以上传统方法的缺点,达到了时序控制灵活性好、方便移植的目的。对于该方案采用了第三方验证工具modelsim进行功能验证,并进行了硬件实测。

1 驱动方案分析

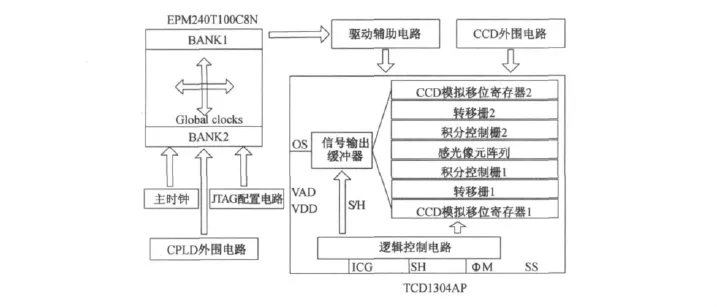

文中采用的线阵CCD是东芝公司的TCD1304AP,它是一种双沟道线阵CCD,具有高响应度、低暗电流的特点,包括3 648个像敏单元,像敏单元尺寸为8μm×200μm,并且带有电子快门和采样保持电路,另外还集成了逻辑控制器,这给电路驱动的时序控制提供了方便,但同时也带来了不确定性。驱动电路的设计框图如图1所示,现采用的CPLD芯片是ALTERA公司MAXⅡ系列的EPM240,逻辑单元240个,典型等价宏单元192个,最大输出输入管脚80个,用户闪存比特数是8 192,引脚至引脚延时间4.7ns[3]。其实对于驱动而言只要基本单元够用即可,驱动芯片的内部资源多少可以根据系统外扩的情况来决定。

图1 设计框图Fig.1 The block diagram of the design

TCD1304AP比普通CCD芯片多了一个光积分控制栅,它是由驱动脉冲ICG控制的,只有当ICG为高电平时,积分栅才能使感光像元阵列产生的光电流在积分栅形成的存储阵列中积累,所以通过控制ICG就能控制曝光时间。转移栅控制脉冲SH的作用同普通CCD的转移栅控制脉冲没有区别,因此如果在一个扫描周期里把ICG常置高,这样也可以利用SH的时序来控制曝光时间,相当于在一个扫描周期里把SH最后一对高低电平之前的信号电荷倒掉,只留下最后一段时间积累的电荷,这就启用了芯片的快门功能[4-5]。

一般对于这种芯片的时序控制有两种方法:

第一种时序驱动关系如图2所示,这种驱动方法优点是实现起来比较简单,但这种工作方式属于传统CCD芯片的工作方式,没有体现出电子快门的优势,不能把积分时间控制得非常短。并且这种驱动方法会对某些非接触测量系统的实时测量产生影响,如果想增大或减小积分时间,需要增加或减小行扫描周期。通常情况下,在实时的高精度非接触测量系统中调整积分时间时,扫描周期最好不要变化,否则后续的信号处理和算法部分就要加入对应于积分时间调整的自适应算法,会增加算法设计和系统调试的复杂程度。

第二种时序驱动关系如图3所示,这种驱动方法弥补了第一种方法的不足,可以在行扫描周期不变的情况下改变积分时间,但改变积分时间会导致ICG在低电平期间内同SH的时序对应关系发生变化,这样就需要重新计算SH同ICG的时序,来保证SH同ICG的时序对应关系。在积分时间改变或驱动程序移植时会增加设计者的计算量,影响了开发效率[6-7]。

图2 第一种驱动方法的时序Fig.2 The first driving sequence

图3 第二种驱动方法的时序Fig.3 The second driving sequence

2 驱动方案改进

文中根据芯片的工作原理采用了一种新的时序驱动方式,先设计主时钟计数器,确定一个扫描周期的长短,CPLD的输入时钟为50MHz,所以计数器是每20ns计数1次。然后确定光积分控制栅的时序ICG,ICG同SH的时序关系设定如图4所示,让ICG在一个周期里只有t2为低电平,其余为高电平,在前面的预留的t1是为了方便对SH脉冲编程,所以写ICG的Verilog程序时从t1段脉冲开始,SH的第1段为t3低电平,ICG同SH在t3和t1的起始端同时开始工作,SH的第2段为t4高电平,这两段脉冲的作用是确保积分时间之前多余的信号电荷被移除,第3段为t5低电平,第4段为t6高电平,t3、t4和t5的总脉冲长度要超过t1,要让ICG在t2期间只对应有SH一段高电平t6,要让t6的下降沿也落在t2内,t5和t6之和就是一个扫描周期的积分时间,第5段为t7低电平,这一段是确保积分时间结束。逻辑控制器主时钟ΦM的时序在ICG上升沿处的前20ns和后20ns都为高电平。时序控制框图如图5所示。

图4 改进方案的驱动时序Fig.4 The driving sequence of the improved scheme

图5 改进方案的时序控制框图Fig.5 The sequence block diagram of the improved scheme

在应用这种驱动方法时,可以根据自己的需要调整电路时序,以达到预期的设计目标。调整转移脉冲SH的t5和t6,就可以控制积分时间,调整主时钟计数器clk_50M_cunter,就可以控制扫描周期。

下面提供了部分主要的时序程序。

主时钟计数程序:

积分控制栅脉冲ICG程序:

转移脉冲SH程序:

逻辑控制器主时钟ΦM程序:

这里调整ΦM周期时,可以通过上面程序中的参数a来控制,实验中a设置为5,程序中M即为逻辑控制器主时钟ΦM。

3 仿真与实测结果

首先使用通用的第三方验证工具Mentor公司的Modelsim来进行功能验证,由Modelsim软件生成的仿真时序图如图6所示,利用软件的标尺工具对图6中的ΦM、SH和ICG进行了测量,仿真结果和Verilog程序设定的时序完全一致。

然后采用RIGOL公司的DS5062M示波器进行硬件电路的实测,其带宽60M,事实采样频率500MSa/s,波形刷新率1 000wfms/s。

逻辑控制主时钟ΦM在高低电平的起始端有不规则的尖峰出现,但其作为输入脉冲并不影响CCD芯片的工作。实测得到了ΦM的各项参数,峰峰值为7.36V,最高电压为5.28V,最低电压为-2.08V,平均电压为1.72V,周期为1.280μs,上升时间小于50.0ns,下降时间小于50ns,见图7。

图6 仿真验证时序图Fig.6 The sequence diagram of simulation

在图8中,上面为光积分控制脉冲ICG,下面为转移栅控制脉冲SH,驱动脉冲波形同驱动程序的预期一致。实测得到了ICG的各项参数,峰峰值为3.64V,最大电压为3.48V,最小电压为-160mV,平均电压为2.85V,上升时间小于200ns,下降时间小于200ns。实测得到了SH的各项参数,峰峰值电压为3.60V,最大电压为3.52V,最小电压-80.0mV,平均电压1.33V,上升时间小于4.00μm,下降时间小于小于4.00μm。

图7 逻辑控制主时钟ΦMFig.7 Master clock pulse of logic controlΦM

图8 实测转移栅控制脉冲SH与光积分控制脉冲ICGFig.8 Shift Gate pulse SH and integration clear gate pulse ICG

图9 实测输出信号Fig.9 The output signal of actual measurement

TCD1304AP输出的是负极性信号,在实测时用不透光的薄片遮挡CCD玻璃窗的两端,可以看出输出信号低电平的宽度随透光宽度的变化而变化,说明CCD芯片工作正常。图9为一副实测截图,其中峰峰值为1.48V,最大电压为2.36V,最小电压为880mV,平均电压2.14V,上升时间3.30ms,下降时间2.30ms,上升时间和下降时间比较大是由于通过CCD玻璃窗的光线的散射和在边缘处光线的衍射造成的。另外利用这套硬件电路还做了平行光成像法的测径实验,待测物的直径为1.964mm,实验的光源是LS650-5半导体激光器,它的波长为650nm,功率为5mW,实验得到的测量相对误差为0.39%。

4 结 论

通过实验和仿真两方面检验,该设计方案成功驱动了积分时间可调型线阵CCD芯片。硬件设计采用Verilog语言,根据CCD芯片的工作原理,重新设计了工作时序。这种驱动方法相比传统的驱动方法有很多优势,可以在不改变扫描周期的情况下方便地增加或减少积分时间,在改变积分时间时,也不用重新计算各驱动脉冲的关联关系。这对于CCD积分时间的调整十分有利。另外这种方法没有利用CPLD宏单元模块,并且CPLD芯片的设计输入只采用硬件描述语言的输入方式,从而达到了方便移植的目的。这样在工程开发上,可以很好地提高开发效率,减小开发成本。方案对于CPLD的各项优化设置为均衡设置,当有速度或面积特殊需求时,在此基础上可以方便调整,以达到更高的技术指标。

[1]王庆有.图像传感器应用技术[M].北京:电子工业出版,2003:90-99.

[2]张化朋.用单片机驱动线阵CCD的探讨[J].光学技术,2000,26(4):342-347.

[3]王 诚.AlteraFPGA/CPLD设计[M].北京:人民邮电出版,2005:63-68.

[4]彭晓钧,何平安,袁炳夏.基于CPLD的线阵 CCD驱动电路设计与实现[J].光电子·激光,2007,18(7):803-807.

[5]XU T X.Design of FPGA based on linear array CCD driver circuit[C]∥Proceedings of 9th International Conference on Electronic Measurement and Instruments.Piscataway:IEEE Computer Society,2009:2766-2769.

[6]顾 一,叶 炜,许 煜.基于CPLD的面阵 CCD驱动时序发生器设计[J].光学仪器,2008,30(6):54-59.

[7]付天舒,赵春晖.基于 Verilog的线阵CCD驱动时序设计[J].光学技术,2010,36(5):740-743.