超高频RFID阅读器电荷泵锁相环设计

2012-08-13于洋

于 洋

(天津大学 电子信息工程学院,天津 300072)

锁相环是在模拟/数字电路设计中的一种非常重要和实用的电路结构[1]。 锁相环[2-3]由鉴频鉴相器、电荷泵、滤波器、压控振荡器以及分频器等构成,在具体电路设计中还可能涉及到基准(PTAT)电路和一些简单的数字电路。由于锁相环正常工作时能通过内部电路中精准的负反馈机制提供稳定的输出频率作为本振信号,因此,该结构广泛应用于数字及模拟电路设计之中。

1 电荷泵锁相环电路设计

1.1 电荷泵锁相环原理与整体结构

图1所示为电荷泵锁相环[4]的系统结构图。

锁相环系统的基本原理为:最初外部参考信号与分频器输出信号同时输入给系统,送入鉴频鉴相器;鉴频鉴相器检测ωout与ωin两路信号的相位差和频率差以及上升沿和下降沿,并随时根据它们的上升、下降变化决定电荷泵的开启和关断状态;电荷泵的输出电压Ud经过滤波器滤波, 产生输出电压Vctrl,Vctrl作用在压控振荡器上,产生输出频率;压控振荡器的作用是使输出频率随输入控制电压的变化按照一定比例变化,分频比为N的分频器保证:fvco=fref×N, 其中 fvco为 VCO的输出频率,fref为参考频率。锁相环内部负反馈机制使整个系统达到锁定状态。

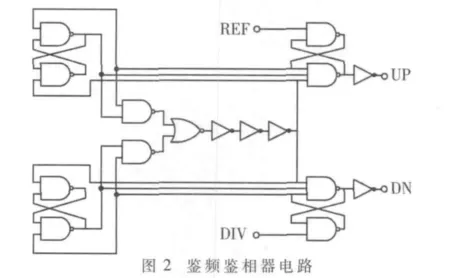

1.2 鉴频鉴相器电路

图2为本锁相环设计中采用的鉴频鉴相器电路[5]。PFD具有鉴相和鉴频的功能。参考信号和分频器输出信号被送入鉴频鉴相器,初始相位差使环路无法锁定,经过一段时间的相位积累就能达到频率捕获。

针对死区问题,本设计所采用的去死区的方法是增加延时单元,延时单元应用串联连接的反相器链。增加延时单元可以使up和dn信号同时为高的时间延长,保证有充分的时间对MOS管的输入电容进行充电,从而达到去死区的作用。同时,时间的延迟要适宜,过大或者过小都会对锁相环的系统造成影响。因此,采用了3级反相器串联的反相器链作为延时单元,实现了合理的延迟时间。

1.3 电荷泵电路

电荷泵[6]实质上就是一个带开关的电流源。鉴频鉴相器的两路输出信号(up、down)通过反相器分别控制电荷泵电路中的4个MOS管,实现对电流源的控制。

针对电荷泵设计中常见的电荷分享、电流不匹配的问题,设计中给出了优化方案。

电流不匹配主要是因为沟道长度调制效应,致使漏电流ID不完全受 VGS控制,使得上、下两路电流源对电荷泵进行充放电时无法达到完全匹配,故采用共源共栅的电流源结构来抑制沟道长度调制效应。但是采用共源共栅的电流源结构会使得电压额度变小,故用宽摆幅电流镜结构给电流源提供偏置电流。

电荷分享问题是在开关MOS管和电流源相接的地方出现的问题。解决方法是采用dummy电路,即不使用单独的两个MOS作为充放电开关管,而是再增加UP_bar和DOWN_bar两个开关管同时控制电容的充放电,使得电流源和后级滤波器电容间总保持连通状态,从而消除电荷分享。

实际设计中采用了dummy电路结构,但这会使图3中左端开关管UP和DOWN_bar之间没有与输出电容相连,进入一种悬空的状态,即两管之间的电压不可知,这是不允许的。解决方法是加入一个用二级运放做成的电压跟随器,使得左端电压跟随右端电压变化。优化后的电荷泵电路图如图3所示。

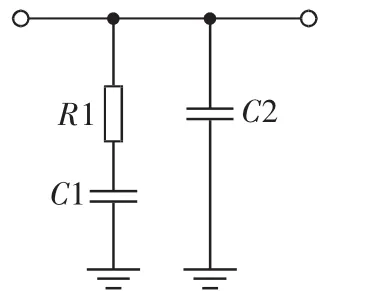

1.4 环路滤波器电路

滤波器[7]采用由两个电容和一个电阻构成的二阶无源低通滤波器,如图4所示。C1主要决定了电荷泵锁相环系统的稳定性;R1主要决定了环路的带宽;C2在环路上增加了一个极点,有助于压控振荡器更好地控制电压中的高频成分。通过系统设计,得出C1=58.62 pF,R1=8.2 kΩ,C2=6.51 pF。

1.5 环形压控振荡器

压控振荡器的设计是锁相环系统设计中的核心,它从根本上决定了锁相环系统性能的好坏。环形振荡器的突出优点是具有较小的功耗,同时又能达到很高的振荡频率。环形振荡器是由3~5级的反相单元(Delay_cell)构成的,其控制电压通过改变电流的大小来实现对延迟时间的控制,进而改变频率。

图5是环形振荡器整体电路结构,采用3级反相单元连接。环形振荡器的总功耗为7.02 mW。

图6所示是通过Cadence仿真得出的环形振荡器的频率-控制电压曲线。该曲线在0.5 V~1.1 V的电压范围内显示出比较好的线性特性,经计算得出VCO的增益Kvco=300 MHz/V。

图4 滤波器电路

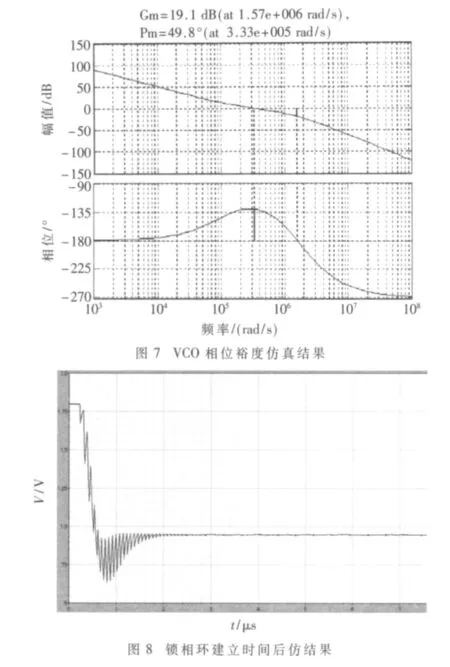

2 后仿真结果与版图

2.1 相位裕度的仿真

在进行系统设计时,将电荷泵的电流Icp设为 60 μA,环路带宽为1 MHz,压缩振荡器VCO的增益为300 MHz/V。采用Matlab进行建模仿真,可得系统的相位裕度为49.8°,如图7所示。

2.2 建立时间的仿真

图8所示为锁相环建立时间通过Cadence后仿真得出的结果。从图中可以看出,建立时间为2 μs。当输入参考信号(REF)与分频器的输出信号之间相位差过大时,鉴频鉴相器会做出相反的误判,把参考信号超前误认为是落后,这样就会产生图8中的尖峰,称之为cycle-slip现象。该现象在锁相环建立的过程中无法避免,但可以通过复位和去死区延时的方法削弱尖峰。

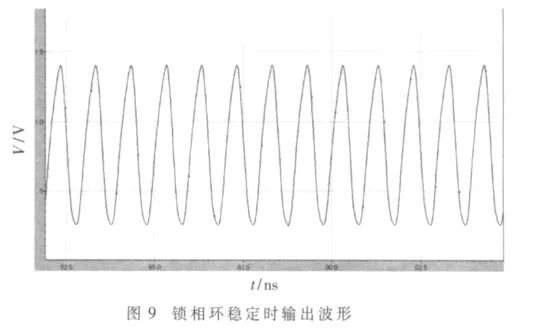

2.3 输出信号波形仿真

图9为锁相环稳定时通过Cadence后仿真得出的输出波形。锁相环锁定时输出频率为966 MHz,输出信号电压幅度为1.4 V,整个系统的功耗为12 mW。

本文设计了一个整数型电荷泵锁相环,并在SMIC工艺下完成了版图和后仿真。其输入参考频率(REF)采用片外独立有源13 MHz晶振,整个锁相环系统稳定时后仿输出信号频率为966 MHz,功耗为12 mW,芯片面积为 880 μm×750 μm。

[1]CHARLES C T,ALLSTOT D J.A buffered charge pump with zero charge sharing[C].Seattle:ISCAS,2008:2633-2636.

[2]SHU K,SINENCIO E S,MARTINEZ J S,et al.A 2.4-GHz monolithic fractional-N frequency synthesizer with robust phase-switching prescaler and loop capacitance multiplier[J].IEEE Journal of Solid-State Circuits,2003,38(6):866-874.

[3]SAYFULLAH M.Jitter analysis of mixed PLL-DLL architecture in DRAM environment[C].MIXDES′09.MIXDES-16th,Lodz,2009:445-449.

[4]FERRISS M A.A 14 mW fractional-N PLL modulator with a digital phase detector and frequency switching scheme[J].IEEE Journal of Solid-State Circuits,2008,43(11):2464-2471.

[5]KIM C,HWANG I C,KANG S M.Low-power small-area±7.28 ps jitter 1 GHz DLL-based clock generator[C].Solid-State Circuits Conference,2002,1:142-453.

[6]Zhou Yunfang.Design of low phase noise LC VCO for UHF RFID reader[C].15th Asia-Pacific Conference on APCC 2009,Shanghai,2009:414-417.

[7]YOUNG I A,GREASON J K,WONG K L.A PLL clock generator with 5 to 110 MHz of lock range for microprocessors[J].IEEE Journal of Solid-State Circuits,1992,27(11):1599-1607.