基于USB和FPGA的多功能等效器设计

2012-08-10苏虎平沈三民刘文怡

苏虎平,沈三民,刘文怡,叶 勇,张 昊

(中北大学电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西 太原 030051)

责任编辑:时 雯

等效器是一种自动测试系统,是用以产生各种模拟、正弦、串行数字、时间指令脉冲等控制和测试信号,并进行事后数据分析和处理的自动测试平台。等效器由计算机进行整体控制,由上位机下发命令到等效器的等效功能模块产生所需要的各种测试信号,并将需要检测的数据读回来存储、分析、处理,本文设计的等效器的多功能性体现在它不仅可以提供控制和测试信号给遥测设备的地面系统测试中,还可以对被测设备(遥测系统)进行实时监控、功能检测和故障定位诊断等。

传统的通信接口通常采用PCI总线或者是RS-232总线。PCI总线有较高的传输速率,可达132 Mbit/s,也可以即插即用,但是其扩展槽有限且插拔不方便;RS-232连接比较方便,但是传输速率太低。由于USB具有有传输速度快、占用资源少、真正的即插即用,且与PC产业的一致性和成本低廉等优点,使其迅速在市场中流行。FT245RL是FTDI公司的快速USB通信接口解决方案之一,它无需编写片内固件程序,PC机使用FTDI公司提供的官方驱动程序D2XXDRIVER,FT245RL芯片的主要功能是在内部硬件逻辑的作用下实现USB串行数据与并行数据的双向转换。因此,基于FT245RL的USB设备在测试系统中有很大的优越性。本文上位机通过USB接口与FT245RL进行数据交换,FT245RL则通过并行方式与等效器主控 FPGA 通信[1-2]。

1 系统整体设计思路和结构简介

设计采用FT245RL和FPGA实现数据的通信,FPGA作为主控制器,FT245RL作为与PC机的USB通信接口。FPGA通过FT245RL接收上位机传输的命令、数据,然后根据上层通信协议判断命令和数据类型,转发上位机命令、数据到各功能模块以实现不同的功能。为了匹配USB读数速率和422异步串行通信发送数据速率的不同,采用FPGA内部实现FIFO缓存通信数据。本设计尽量进行模块化设计、弹性设计,可随时对系统进行升级改进,扩大如图1中所示的等效模块,系统整体架构见图1。

2 硬件模块设计

2.1 基于FT245的USB接口部分设计

图2为FT245RL的USB接口电路。FT245RL 内含两个FIFO数据缓冲区。一个是128 byte的接收缓冲区,另一个是384 byte的发送缓冲区,它们用作USB数据与并行I/O口数据的交换缓冲区。FIFO主要是通过8根数据线DO~D7、读写控制线RD和WR、FIFO发送缓冲区空标志TXE和FIFO接收缓冲区非空标志RXF的配合来完成数据的交互。本设计采用自供电方式,上电复位,采用内部晶振。图中ACM-2012-900-2P共模电感和磁珠是为了减少主机和设备的干扰,PWREN管脚用于判断USB总线是处于挂起状态还是正常状态,D0~D7是8根数据线,、WR是FT245与FPGA相连的控制线。

图1 等效器系统整体结构图

图2 等效器系统USB接口电路

2.2 直流量部分设计

系统设计了16路模拟信号的输出电路,对于不同电压值可调的直流量信号,最好的选择就是用D/A转换电路产生小幅值电压,然后运用信号调理电路产生所需要的电压值。对于如此多路直流信号,如单独实现每一路直流信号则会造成太大的浪费和成本的提高,因为各直流量信号的变化速度相对有限,因此本设计用模拟开关分时切换进行多路信号的输出,这样只需运用一片D/A转换电路就可产生多路模拟直流信号。本设计由D/A转换电路、运算调理电路、模拟电子开关、电压保持电路组成。其具体电路如图3所示。

DAC电路的设计需要考虑主要因素主要有转换精度、转换速度、电源要求等。此外温度特性、数据耦合、焊接毛刺和非线性误差的影响也不容忽视。本设计选用ADI公司的AD7945作为DAC芯片,它是12位乘法型并行输入、单通道的电流输出型低功耗数模转换芯片,具有低温漂、良好线性度的特性,采样速率可达l.7 MSample/s,转换时间最大值为760 ns,可直接与TTL或CMOS逻辑电平进行连接,本设计由REF0205输出稳定的5 V电压来作为基准电压,分辨力约为0.00122 V,精准度高。

图3 D/A转换电路

因为要输出模拟电压值,需将AD7945的输出电流转换为电压。设计时输出经两级反相运放转换为需要的电流。前一级I/U转换,后一级为利用反相比例放大电路设计的一阶低通滤波器,输入阻抗较小。由运算放大电路的运算公式可知

式中:Uout为AD7945转换输出并调理后的模拟量采样幅值电准电压;D为模拟电平的量化值。

如上文所述,任务要求产生多路模拟直流信号,因此本设计将D/A转换电路调理输出的电压值经过模拟开关分时输出以“同时”产生多路直流信号。系统采用ADI公司的模拟开关ADG506,其具有16路模拟数据通道,电压输出范围宽泛、功耗低,并且兼容CMOS/TTL电平标准,最大导通时间400 ns,开启时间为50 ns,导通电阻一般为280~600Ω。因为要保证各通道独立持续输出模拟量,所以使用存储芯片SRAM对各通道要转换的数字量进行存储。FPGA的进程触发后,从SRAM中一次读取数字量,并控制模拟开关切换到相应的通道。模拟开关的A0~A3值与SRAM的地址线是同一数字线,这样不同的SRAM存储单元对应不同的通道号。

2.3 正弦信号部分设计

AD558是电压输出型的D/A转换器,输出电压范围为0~10 V,再经过由运算放大器构成的差动减法电路,实现电压范围从0~10 V到-5~+5 V的转换,这个差动减法电路还具有电压放大的功能,将转换的电压放大两倍,实现-5~+5 V到-10~+10 V范围的电压输出;再经过其后由RC和电压跟随器电路构成的简易有源低通滤波器,实现电压平滑输出,使用电压跟随器是因为其输入阻抗很大,输出阻抗很小,实现前后电路阻抗的匹配,电压的完整输出。首先上位机软件将所需要产生的一定频率、幅值的正弦波形量化,采样256个点,计算出每个点的电压;然后通过USB接口将量化数据传送给主控FPGA,主控FPGA将这些数据写入正弦波形存储RAM;再由FPGA根据接收到的正弦波形的频率等参数计算出正弦波形的周期以及每两个点的时间间隔,将时钟分频到所需的周期,按照频率参数读取RAM中的数据送往D/A转换电路输出,从而产生所需正弦交流信号,图4为正弦信号产生电路。

图4 正弦信号产生电路

2.4 特定帧结构的异步串行通信部分设计

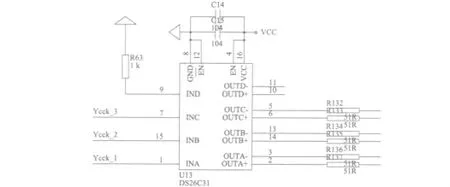

设计选用DS26C31作为RS-422发送控制器,用FPGA控制产生所要求帧结构的异步串行数据。硬件电路如5图所示,在发送端分别串联50Ω的限流保护电阻,为了防止大电流对输入端的影响。DS26C31的作用是将输入端TTL/CMOS电平转换为RS-422电平,具体的异步串行通信的数据发送波特率、时序和帧结构等特性都由FPGA来实现。对于异步串行通信来说,数据的传送涉及众多的参数:对于每一字节数据设计的参数有:波特率、数据位的数量、停止位的数量、奇偶校验位等;对于数据帧来说涉及的参数有:帧类型、一帧数据的数量、帧数据的组织方式等。本设计按照任务要求的RS422异步串行通信数据帧格式为:波特率可变(可选择为4800,9600,19200,38400,115200,1152000),数据字节校验方式可变(可选择为奇校验、偶校验),停止位数量可变(1位停止位或2位停止位);帧结构类型可选择(信息帧、确认帧、否认帧),信息帧组织形式可变(递增数据、递减数据、固定数据),信息帧数据数量可变,信息帧起始字节可设置等[3]。

图5 RS-422电平转换电路

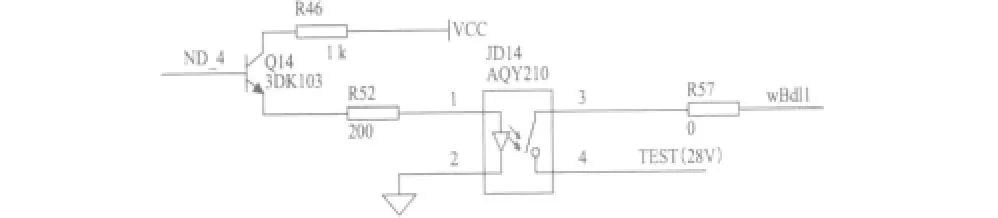

2.5 时间指令脉冲信号部分设计

本设计由FPGA控制光耦AQY210来实现所需的时间指令(包括带点指令和不带点指令)。带电不带电时间指令信号电路设计类似,只不过带电指令信号的供电电压由等效器提供;而不带电指令信号的供电由测量系统来提供。AQY210具有噪声低、速度快、体积小、寿命长、触发电压低等优点,常用于信号的传递、电器隔离的场合。本设计采用此电路实现了时间指令信号。用FPGA管脚接到三极管3DK103的基极来控制三极管的通断:当FPGA输出“0”电平时,三极管工作在截止状态,发射极输出低电压低电流,这样AQY210不导通,信号输出端口工作在高阻态;当FPGA输出“1”电平时,三极管工作导通,发射极输出高电压高电流,驱动AQY210导通。时间指令信号的设计就是在上述开关电路的基础上,FPGA收到上位机发来的命令后,判断命令类型,确定通道号,之后启动计数器来实现规定时间的开关电路的通断来实现的,如图6为时间指令脉冲硬件电路部分设计。

图6 时间指令脉冲电路

3 等效器应用层通信协议

等效器产生的信号类型和数量众多,且这些信号模块都必须受上位机的控制,为便于对这些信号控制模块进行统一管理,本文设计了统一的等效器应用层协议,此协议包括各类信号帧结构的设计和协调一致的工作流程。

本设计中一帧有10 byte,其中帧头2 byte,命令域、模块选择、子模块选择、命令类型、校验域和帧尾各占1 byte,设置参数占2 byte。命令域包括包括自检和握手命令、停止命令、各功能模块接收信号命令;模块选择和子模块选择代表不同功能模块的逻辑地址;设置参数包括直流信号、时间指令脉冲信号、422异步串行输出信号、正弦信号、模拟信号清零复位信号;校验域采用奇校验,通过校验域来保证命令和数据传输的可靠性[4]。应用层通信协议帧结构的设计如图7所示。

图7 应用层通信协议帧结构

4 系统软件设计

4.1 USB读写时序

接收数据时序图如图8所示。接收数据的过程是外控制器(本设计为FPGA)不断查询FT245RL的RXF引脚状态,如果RXF引脚为高电平,说明芯片正处于接收数据状态;当RXF为低电平,则说明芯片已经接收完成一字节数据并存储到FT245RL的接收缓冲区(接收FIFO);外控制器随即驱动RD引脚由高变低产生读控制时序,即可读取接收FIFO中数据到外控制器的数据缓冲区。重复上述接收数据步骤即可实现一帧数据的接收,然后即可进行帧处理,实现既定的功能。

图8 接收数据时序图

RT245RL发送数据时序图见图9。发送数据到上位机的过程主要是外控制器(FPGA)不断查询FT245RL的TXE引脚电平,当其为高电平说明上一次写入数据的过程还未完成;当其变为低电平表明FT245RL发送逻辑空闲,外控制器将所需发送数据准备好后,驱动WR引脚由高到低产生下降沿即可将缓冲区内数据写入FT245RL的发送FIFO,随后FT245RL在适当的时候自动将数据发送给上位机,重复上述发送数据步骤即可实现上传数据给上位机。

图9 发送数据时序图

4.2 VB上位机软件设计

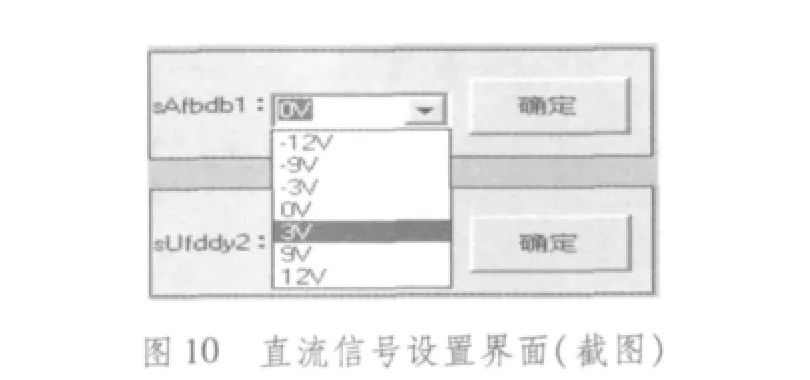

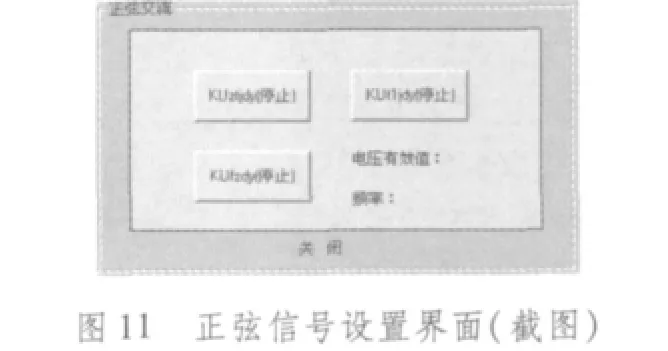

设计由各硬件电路模块实现任务要求的具体功能,由上位机对整个等效器的工作进行整体控制,上位机通过发送启动命令、设置参数与等效器进行数据交互。上位机与等效器通过USB总线接口进行通信,通信协议参见“等效器应用层协议”。其中每一类信号的命令信息帧根据“等效器统一帧结构”的格式而制定,上位机与等效器硬件电路的数据通信流程严格按照“上位机向主控模块发送命令通信协议”的规定执行,具体见图10~图13。

5 测试结果

图14为按照图10的设置测试一路直流信号的结果;本文设计的是多路固定频率和固定幅值的正弦信号,图15为按照图11测试的一路峰峰值为9 V、频率为18 kHz的正弦信号的结果;图16为按照图12的设置测试了异步串行通信数据帧的结果数据(确认帧和否认帧与此类似);图17为按照图13的设置测试了一路幅值是28 V的100 ms时间指令脉冲信号,由此可见本文设计的等效器能很好地提供遥测设备在系统地面测试对外系统控制和测量参数的要求。

图14 直流信号测试结果(截图)

6 结束语

本文提出一种外系统等效器的设计及实现方案,利用模块化工程设计思想,将整个等效器任务按照功能要求分为各个子模块单独实现,在实现功能的基础上充分保留设计裕量,以备对系统进行升级改进,进行弹性设计,可以很好地测试外系统遥测设备的可靠性和监测功能。此方案实现的等效器已成功应用于某型号航天器遥测设备的地面测试系统中,经调试和测试后,该等效器工作稳定,满足工业现场的要求,达到设计目的。

[1]李娜,孟令军.用FT245BM实现FPGA与PC机的数据无缝传输[J].重庆工学院学报:自然科学版,2009,23(5):80-83.

[2]孙立辉,刘院英,和志强.基于FT245BM和FPGA的USB接口设计[J].微计算机信息,2006(2):183-185.

[3]高世杰,竺晓山,吴志勇,等.基于USB2.0的多路异步串行系统设计[J].电视技术,2005,29(7):91-93.

[4]陈志良,曾浩.基于DSP+FPGA视频信号处理器的USB扩展及应用[J]. 电视技术,2011,35(23):44-47.