遥控副载波数字化解调器技术研究

2012-08-09司莹莹

司莹莹

(滨州医学院信息系统教研室,山东 烟台 264003)

随着通信技术迅猛发展,遥控技术作为通讯领域的一个分支,正向数字化、集成化、小型化、系列化方向发展。集成电路规模的扩大和生产工艺进一步提高,使遥控单元的数字化、软件化成为可能,并替代现有的遥控单元,完成多模式解调功能。

与模拟解调器相比,数字化解调器有以下特点:(1)数字化解调器可编程能力强,对于相同的硬件平台,通过软件编程或参数的设置可以对载波频率、码速率、码型等参数进行操作和控制;(2)抗干扰能力强,具有数字信号处理能力,易于仿真分析,便于多路复用、生产制造和调试[1]。

1 解调器原理

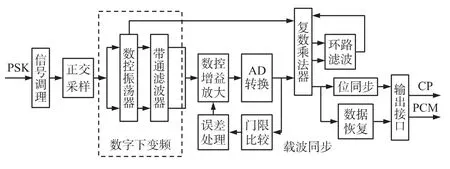

解调器由四个部分组成:数字下变频模块、载波同步模块、位同步模块和数据恢复模块[2]。其结构如图1所示。

图1 解调器原理图

输入PSK 信号经过放大滤波等信号调理后,用模数转换器直接进行正交采样,产生两路正交信号;将正交信号送入数字下变频模块(数字下变频模块由数字混频器、数控振荡器和带通滤波器组成),信号与数控振荡器产生的数字正交信号相乘,得到的两路信号通过带通滤波器,此带通滤波器的带宽恰好使信号的有用频谱通过并阻止带外的噪声通过,经过带通滤波和抽取后输出为采样速率较低的基带数字信号I和Q;两路基带数字信号经过AGC(Automatic Gain Control),使其电压增益自动地随信号强度而调整,以达到自动增益控制的目的;输出信号到载波同步模块,载波同步模块由复数乘法器、环路滤波器和数控振荡器组成,使用科斯塔斯环[3]实现对副载波相位和频率的跟踪捕获,以保证调制副载波和解调副载波的同频同相;位同步模块使用自同步法实现,信号经过位同步模块后,实现符号定时的捕获与同步,以保证本地估算采样判决时刻始终与最佳采样时刻一致;数据恢复模块完成对原始调制信号的恢复,经过上述过程后得到脉码调制数据PCM和时钟CP,实现解调过程。

1.1 原理算法

输入的PSK 信号序列的表达式为:

其中,m(t)∈[-1,1]是二进制单极性随机振幅,f0为接收信号的载波频率,ψ为载波的瞬时相位[4]。

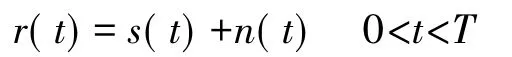

设在一个码元持续时间T 内,经过带通滤波后的接收信号和噪声电压为:

其中,n(t)为高斯白噪声,根据随机过程的理论,噪声电压可以表示为:

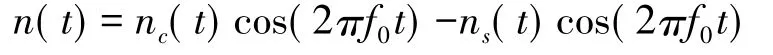

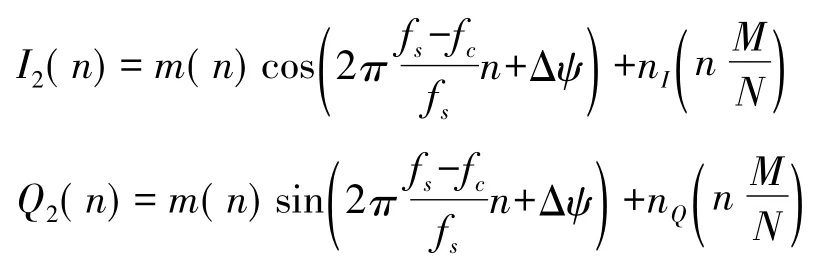

两路正交信号通过数字下变频后,高频分量被去掉,得到的信号分量表示为:

令Δf=fs-f为接收信号的频率差,Δψ=ψ-φ为接收信号的瞬时相位差。输出频率fs接近于fc,使得Δf 接近与零,通过自动增益控制,放大电路的增益随控制电压而改变,此时得到的信号为:

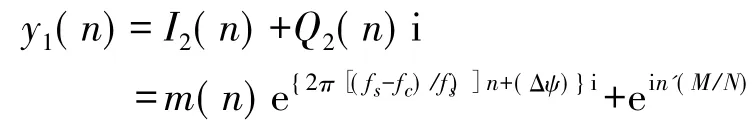

选取适合的M、N值(M≥N),使不同载波和码速率输入下保持解调环路的结构不变。两路信号经过复数乘法器后输出的信号为:

通过设置频率控制字和初始相位,数字控制振荡器可生成所需的正余弦输出序列,送入复数乘法器后得到的输出信号为:

令σ=Δψ-φ,则当载波跟踪环路设为锁定状态时,σ、Δf≈0,可将噪声忽略,此时输出信号则为:

将输出的信号进行位同步,由于信号包含调制信息,即可得到解调信号。

1.2 载波同步

同步是调制系统十分重要的问题,只有收发两端协调工作,系统才能真正实现解调功能。在相干解调中,相乘电路需要有相干载波,该载波必须要从接收信号中获取,并且要求与接收信号具有相同的频率和相位。载波同步就是在相干解调时,在接收设备中产生一个与接收信号的载波同频同相的本地相干载波信号的过程,它是实现相干解调的基础。本文介绍的解调器使用的载波同步环是改进的科斯塔斯环,它对传统科斯塔斯环的改进是首先对两路信号相乘获得相位误差信号,再对每个载波频率进行π/2 相移。改进型的科斯塔斯环克服了传统科斯塔斯环相位模糊的缺点[5],有利于提高信号的捕获能力,适合于载波频率经常变化时信号的提取。

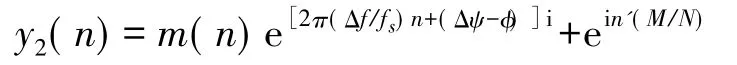

环路滤波器是一种低通滤波器,主要作用是建立环路的动态特性,在鉴相器的输出端衰减高频误差分量,以提高抗干扰性能[6]。当环路在跳出锁定状态时,可以提高环路以短期存储,确保环路迅速重新捕获信号。环路滤波器是实现载波同步的关键,在该解调器中使用环路滤波器目的是减弱由于输入信号噪声引起的相位误差和高频分量,以便在输出端对原始输入信号进行有效估计。环路滤波器对信号的动态响应程度取决于环路滤波器的阶数,本文采用二阶二型环,环路滤波器的传递函数可表示为:

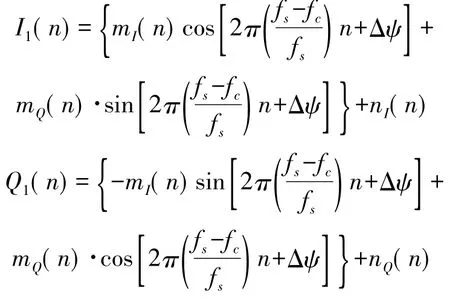

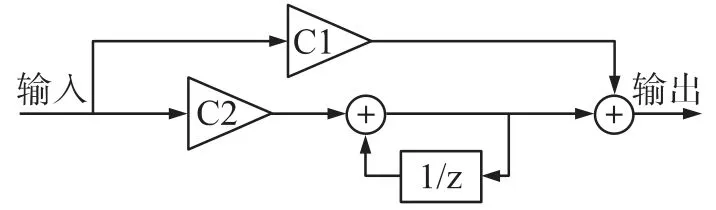

环路滤波器[7]的结构如图2所示。

图2 环路滤波器结构图

图中C1为滤波器的比例通路的增益系数,C2为积分通路的增益系数,系数C1是无量纲的,C2必须有时间的量纲。C1和C2的值与选择的环路参数(固有频率ωn和无量纲的阻尼系数ξ)以及环路增益、采样等均有关,C1、C2计算公式如下:

阻尼系数ξ 的值不宜过高,一般在0.5~1 的范围内较好,大于1 的阻尼系数没有过冲,阻尼系数小于0.5 的环路瞬态响应动态特性较差,过冲过大,在这里阻尼系数常取临界阻尼系数0.707。ωn的取值范围很宽,根据需要其范围从10-5~108rad/s。Kd为鉴相器的增益系数,Ko为数控振荡器灵敏度增益常量。

1.3 位同步

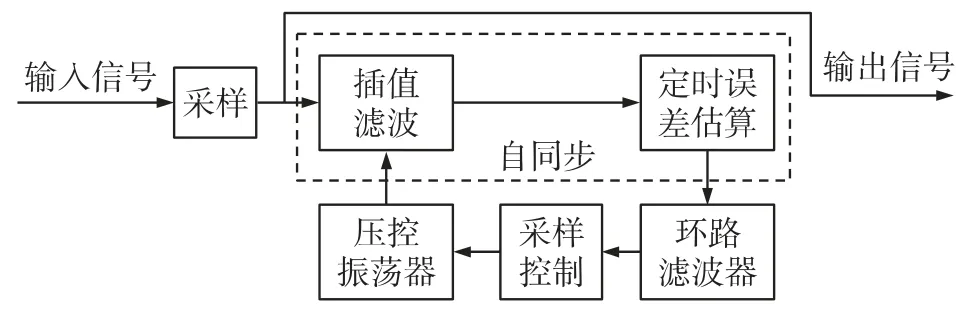

位同步是指接收端根据发送端发送数据的起止时间和时钟频率,产生一个时间基准相同、采样判决时刻与最佳采样时刻一致的定时脉冲序列。位同步又称为码元同步,其实现结构如图3所示。

图3 位同步实现结构图

解调器中的位同步模块通过自同步法[8]实现。解调器的位同步模块通过相位误差估算[9]输出脉冲序列的采样时钟相位与最佳采样时刻之间的相位差,然后产生一个频率与定时误差成比例的误差脉冲,误差脉冲经过环路滤波器滤除高频成分和噪声,进行低通滤波,得到频率控制信号,通过数控振荡器对频率控制信号的频率和相位进行调整。如果输出脉冲序列提前于理想采样信码脉冲序列时刻,则使输出脉冲序列扣除一个误差脉冲,输出的脉冲相位后退,实现采样时刻滞后;反之则将输出脉冲序列附加一个误差脉冲,使输出脉冲相位提前,实现采样时刻提前,从而达到码元同步的目的。这种自同步方法不需要改变时钟相位,具有更好的稳定性,适用于对系统时钟稳定性要求较高的场合。

2 数字解调器仿真

为了便于仿真,本文选用MATLAB 作为仿真工具。仿真数据源中的高斯白噪声采用函数变换法产生,先生成(0,1)区间均匀分布的随机数,再经过函数变换,利用瑞丽分布函数得到具有高斯噪声特性的随机数。

仿真前需要先运行配置初始化仿真参数,运行误码率自动仿真程序,用不同Eb/No 下误比特数和总比特数相比,得到各信噪比下的误码率曲线。由于计算机直接生成仿真数据源,并且除加入高斯白噪声外,不受其它噪声影响,则不存在量化误差。但是,较高的误码率需要很长的测试时间(如对1 kbit/s 在12 dB 时的误码率,一个点的测试大约需要10 h)。

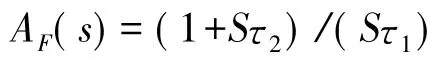

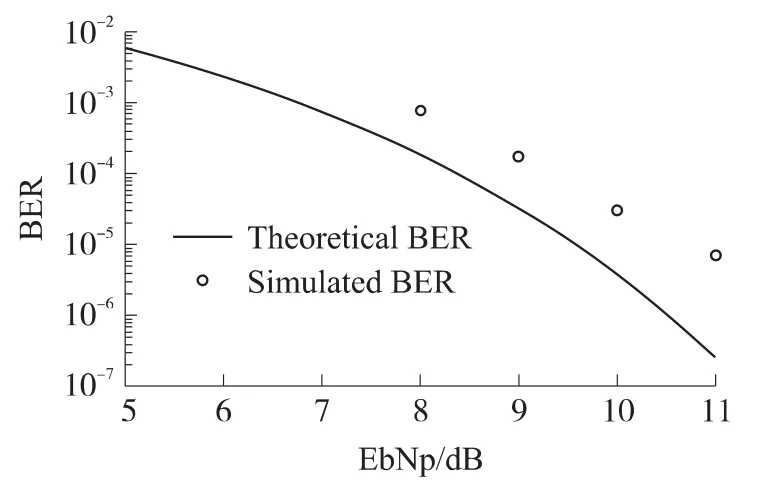

文件运行结束后,绘制误码率曲线。1 kbit/s 误码率仿真结果如图4所示。

图4 1 kbit/s 误码率

利用图1所示解调器,根据文中的算法仿真解调的误码率与理论误码率的比较如图4所示,实线为理论误码率,圆点为仿真误码率。

3 结束语

本文介绍的解调器其优势表现在:便于仿真分析、硬件设计实现;解调过程延迟少、抗干扰能力强、解调过程更稳定;载波同步、位同步响应速度快,跟踪性能好,该解调器可以应用在低信噪比、较大频率偏移范围内工作。目前该解调器已得到工程化的应用。

[1]冯传岗.论现代数字调制技术[J].有线电视技术,2003,(4):69-76.

[2]高翠东,赵琦,陆国雷,等.遥控副载波信号的软件解调方法[J].信息安全与通信保密,2009,(12):50-52.

[3]张欣.扩频通信数字基带信号处理算法及VILI 实现[M].北京:科学出版社,2004:67-69.

[4]赵国栋,徐建良.基于多相滤波的正交采样零中频数字化接收及QPSK 高速解调的FPGA 实现[J].电路与系统学报,2010,(15):134-138.

[5]庄锡荣,焦会.改进型科斯塔斯(Costas)环探讨[J].湖北成人教育学院学报,2009,15(1):121-123.

[6]时瑞瑞.中频数字解调器的载波同步算法研究[D].硕士论文,2010,6:12-15.

[7]蒋毅凯,李国通,杨根庆.基于定点DSP 的软件锁相环的设计和实现[J].电子技术应用,2004,(4):51-53.

[8]孙海洋,刘杰.数字调制信号接收技术[J].现代电子技术,2008,(15):171-173.

[9]Gardner F M.A BPSK/QPSK Timing-Error Detector For Sampled Receivers[J].IEEE Trans.on Common,1986,34(5):423-429.