基于DSP和CPLD的图像采集系统驱动设计*

2012-08-08钟升红康文雄梁永峰

钟升红,康文雄,梁永峰

(华南理工大学 自动化科学与工程学院,广东 广州 510000)

CMOS图像传感器利用感光二极管(Photodiode)进行光电转换,将图像转换为数字数据,每个像素都会连接一个放大器及A/D转换电路,用类似内存电路的方式将数据输出。由于其灵敏度较高、曝光时间较短、像素尺寸小以及成本低、功耗低、整合度高的特点[1],已经广泛应用于工业图像处理系统和面向消费的图像捕获系统中。但通常这些系统获取的图像数据量很大,导致系统效率变低。

复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)[2]是一种用户根据自己需要而自行构造逻辑功能的数字集成电路。CPLD基于Quartus II平台并采用Verilog HDL语言进行编程,因而设计过程简单、灵活和高效,而且可直接通过检测CMOS传感器的帧、行、点这些有效信号来获取图像数据。

数字信号处理器 DSP(Digital Signal Processing)具有强大的数据处理能力和较高的运行速度,已广泛应用于图像处理领域。TMS320C64x系列芯片的EDMA支持外围设备传输模式(PDT)[3],从而提供了一种在外围设备和外部存储器设备之间进行大量数据传输的有效方式。当PDT被激活时,数据直接被外部源驱动,并通过统一数据线写入,在没有CPU参与下完成大量数据转移,减少了总线周期数,大大提高了传输效率。

图像采集系统的速度是决定其广泛应用的因素之一,比如在生物特征识别系统中,采集速度是其评价标准之一。C64x系列芯片的运算速度比C5000系列有了大幅度提高,而其新增的PDT传输功能也恰好解决了大量数据传输的速度问题,使其数据处理能力得到了进一步提升。

1 硬件电路设计

1.1 CMOS传感器设计

CMOS是图像采集系统中的核心器件,本系统采用Aptina公司的MT9V032C12STM (1/3英寸的Wide-VGA黑白CMOS传感器)。CMOS主体电路设计如图1所示,SYSCLK脚接外部晶振使CMOS传感器工作模式为主模式,在主模式中,CMOS传感器不断采集图像。DOUT_0~DOUT_9为图像数字信号输出引脚,实际只用到了DOUT_0~DOUT_9,FRAME_VALID 为 帧 信 号 管 脚 ,LINE_VALID为行信号管脚,PIXCLK点信号管脚,SCLK、SDATA为设置CMOS的控制管脚。为了得到高质量的图像,系统对数字和模拟两部分电路分别独立供电。数字部分供电芯片采用的是MICREL公司生产的MIC5209-3.3BM,它是可以提供500 mA电流的低噪声低压差线性稳压器;模拟部分供电芯片采用的是TI公司生产的TPS79133-EP,它是可以提供100 mA电流的超低噪声、高电源抑制比低压差线性稳压器。

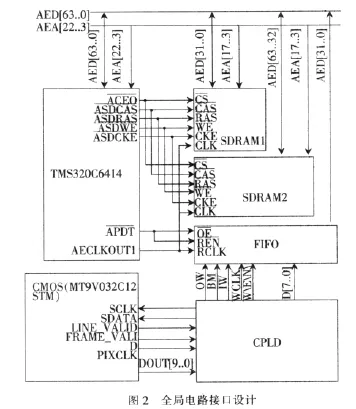

1.2 整体电路接口设计

为减少CPU负荷,系统采用了CPLD来实现辅助逻辑 控 制 ,CMOS 的 DOUT_0~DOUT_9、FRAME_VALID、LINE_VALID、PIXCLK、SCLK和 SDATA全 部 连 到 CPLD实现图像采集控制。CMOS传感器输出的图像数据首先要暂存于FIFO中,本系统应用的FIFO是IDT72V36110,并设置为 8 bit输入和 32 bit输出 (D0~D7为 8 bit数据输入端口,Q0~Q7、Q9~Q16、Q18~Q25、Q27~Q34 组成 32 bit数据输出端口,输入端D8~D35接地,输出端 Q8、Q17、Q26、Q35悬空)。由于CMOS传感器不断采集图像使得输出端不断有数据输出,而此时系统要求只有在需要数据时才去获取传感器输出的数据,因此,本系统中传感器的输出端和FIFO的输入端都连到了CPLD,通过CPLD实现CMOS和FIFO数据总线的连通。图像数据从CMOS到FIFO为写FIFO操作,全部通过CPLD实现,因此,FIFO的控制引脚除和外都连到CPLD以方便控制图像数据输入到FIFO中。图像采集结束后需要把FIFO中的数据转移到外部SDRAM中,即FIFO的读操作和 SDRAM的写操作(PDT写操作),由于传输的数据量大,为了减少CPU的开销并提高传输速度,本系统利用了TMS320C6414的PDT传输功能。因此,FIFO的读使能和输出使能连到DSP的读时钟RCLK连到 DSP的 AECLKOUT1,FIFO的数据输出引脚(Q0~Q7、Q9~Q16、Q18~Q25、Q27~Q34)则 与DSP的EMIFA的低32 bit相连。CMOS传感器采用默认的设置即 480 V×752 H (36 096万像素),为达到图像处理的容量需求,系统利用两片外部同步动态随机存储器(SDRAM)MT48LC2M32B2-5并联构成64 bit接在DSP的EMIFA上,并通过映射到CE0空间,其所有的输入与输出均由输入时钟CLK(接到DSP的 AECLKOUT1脚)来同步[4-5],从而简化了系统的设计,增强了高速处理器接口的能力。本系统电路接口如图2所示。

2 系统程序设计

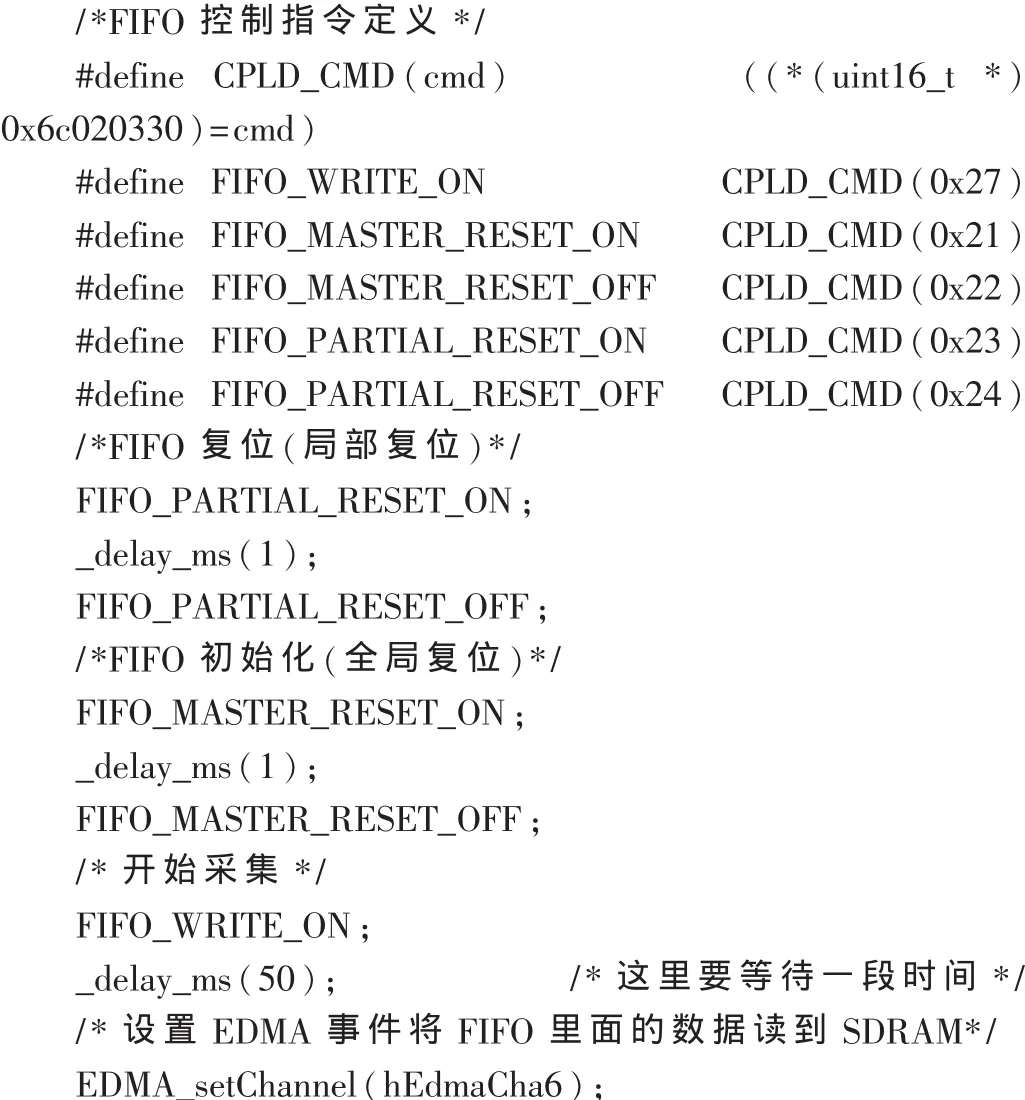

2.1 图像采集部分程序

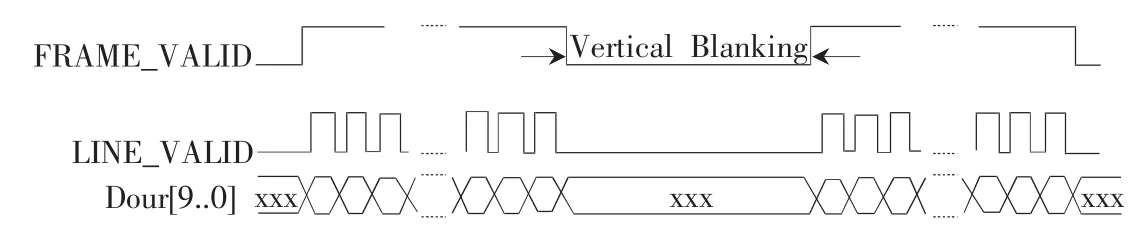

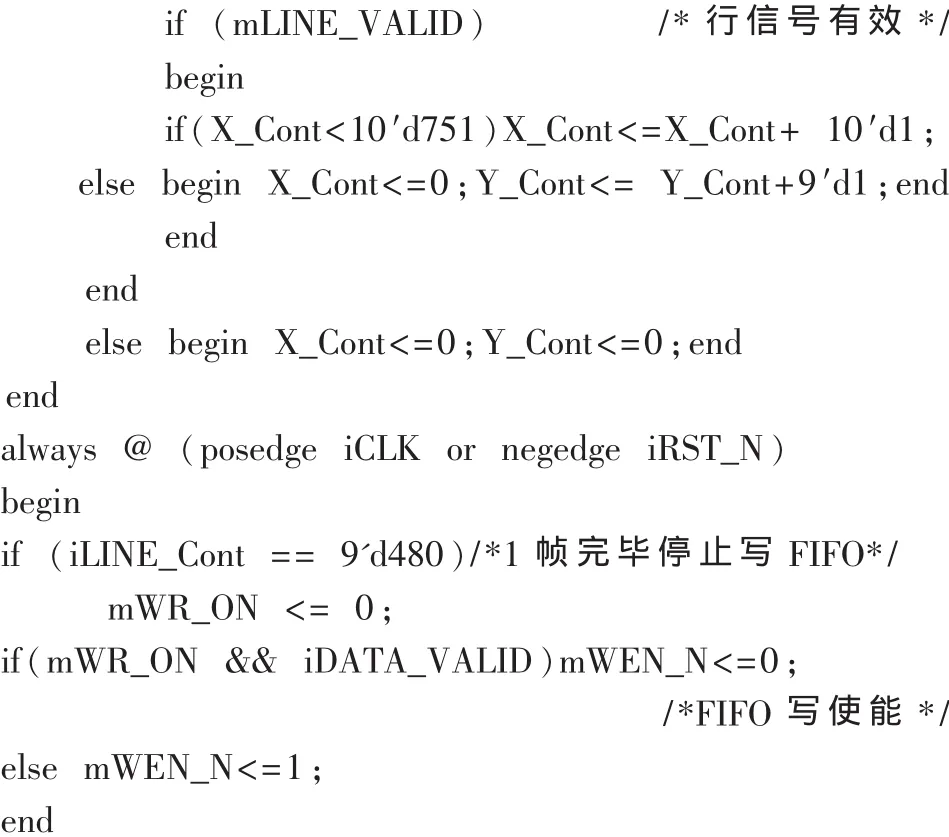

当系统需要采集一幅图像数据时,DSP发出获取图像命令,CPLD对该命令进行译码,然后检测CMOS的帧信号管脚FRAME_VALID,当有一个上升沿到来时,表明一幅新图像数据传输开始;当CMOS的行信号管脚LINE_VALID有一个上升沿到来时,表明一幅图像中的新的一行数据传输的开始;当CMOS的点信号管脚PIXCLK有一个上升沿到来时,表明有一个点的数据可以采集,其波形图如图3所示。CPLD根据这3个信号把数据写入到FIFO中。

图3 CMOS传感器数据传输波形图

图像采集的DSP部分程序为:

图像采集的CPLD部分程序为:

2.2 数据传输程序设计

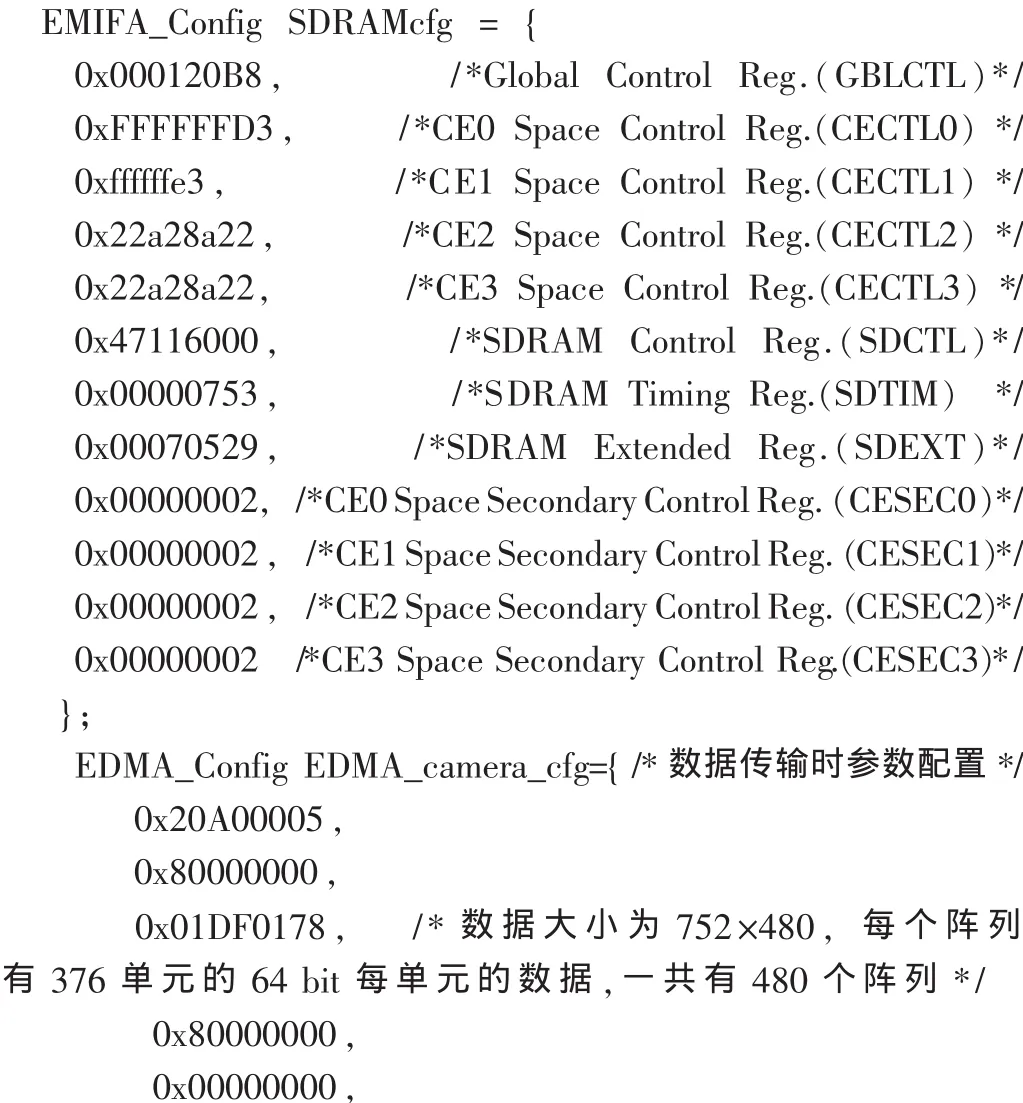

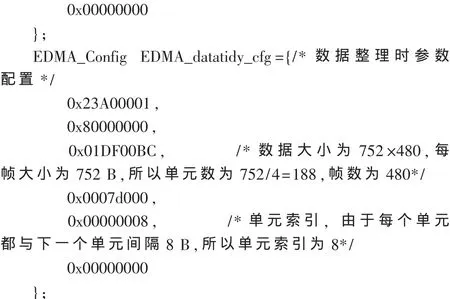

系统中的图像数据处理都在外扩SDRAM中进行,因此,FIFO中的数据需要先转移到SDRAM中。通常这种数据转移需要EMIF读取外设(FIFO),然后向目标存储器(SDRAM)写,整个过程需要两次EMIF操作。由于读取的数据量大,采用常规方法将导致读取和传输效率低下。对此,本系统将FIFO和SDRAM都挂在了DSP的外部总线上,并采用了PDT传输进行优化,整个过程只需占用一个EMIF总线周期,从而大大提高了数据的传输速度。系统中SDRAM是以64 bit方式连接在EMIFA的CE0空间,而FIFO与EMIFA是低32 bit相连,当用PDT模式从FIFO将数据读到SDRAM中必然会造成数据间隔32 bit存放的现象,因此本系统采用EDMA控制使数据成紧密排列方式。相关寄存器配置[6-7]如下:

图像采集系统的设计分为图像获取和图像传输两部分,为提高图像采集系统的工作效率,本文设计了一种以DSP和CPLD为基础的图像采集系统,其中,CPLD的灵活性使图像的获取变得简单,DSP的PDT传输功能使数据传输变得高效。此外,本文也对接口进行了设计。调试和实验表明本系统的采集和传输速度得到了较大的提高。

[1]刘春保,洪镇南,张小伟,等.基于 CMOS图像传感器OV7720的网络摄像机设计 [J].现代电子技术,2011(4):11-16.

[2]GORDON H.用CPLD进行设计 [J].电子设计应用,2009,35(3):52-54.

[3]卞红雨,纪祥春.TMS320C6000系列DSP的CPU与外设[M].北京:清华大学出版社,2007.

[4]李林,谢绍斌,高增来,等.基于 PDT与 EDMA的高速数据传输设计[J].微计算机信息,2008,(18):117-118.

[5]王艳梅,郑成文.TMS320C6701与SDRAM的接口设计[J].沈阳航空工业学院学报,2007(2):51-52

[6]Texas Instruments Incorporated.TMS320C6000 DSP enhanced direct memory access (EDMA)controller reference guide[Z].2004.

[7]Texas Instruments Incorporated.TMS320C6000 DSP External Memory Interface(EMIF)Reference Guide[Z].2004.