一种QPSK载波恢复环防错锁优化方法

2012-07-31朱云鹏

朱云鹏

(中国人民解放军驻北京地区军事代表室,北京100191)

0 引言

现代数字调制技术无论是在民用通信还是军事通信中都起着举足轻重的作用。其中,正交相移键控调制信号(QPSK)因其具有抗干扰能力强、频谱利用率高以及实现复杂度小等优点而在军事通信中得到了广泛的应用。

为了以较低的复杂度获得较好的接收性能,QPSK信号接收机通常采用锁相环技术来实现载频的捕获、跟踪和相干解调。

相干解调中要求收发两端的载波严格同频同相,但当载波跟踪环错锁后,会造成后端信号相关解调的失效,相应地,正确的调制信息就无法通过解调得到。因此,在QPSK的锁相接收系统中,必须采用有效的防错锁措施,确保锁相载波跟踪环能自动地正确锁定在所接收到的信号上。

1 产生错锁的原因分析

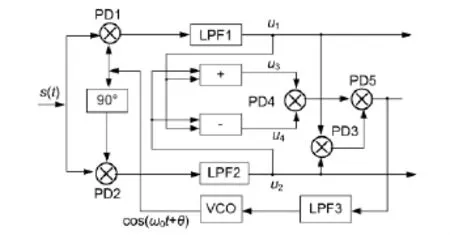

如图1所示,QPSK相干解调器所采用的载波恢复环路均为Costas环路。

图1 QPSK解调器中的Costas环

图中,环路的输入为QPSK信号,取其正交展开式:

式中,ak、bk是2路基带数字信号,取值为±1;ωc为载波角频率。经过环路后,最后一个鉴相器PD5的输出为:

一般可写成下述形式:

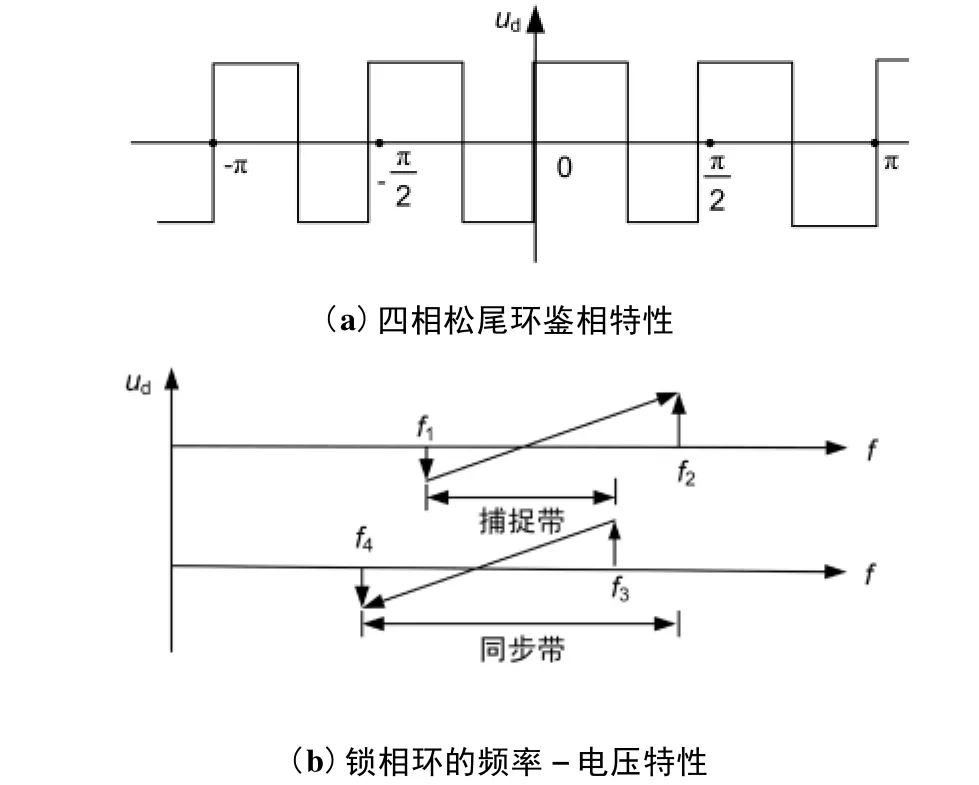

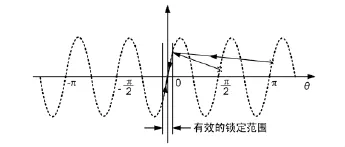

图2 鉴相器鉴相特性

Kd称为鉴相灵敏度,ud(t)是基带处理器的输出,正比于恢复载波和已调QPSK载波的相位误差θ。图2给出了其波形,图中,在(-π,π)内每隔π/2有一个稳定点,即鉴相曲线为正斜率,输出电压ud(t)趋向于零的点。在这些点,环路的输入载波可趋于锁定。在θ不等于零的点,会引起QPSK解调输出数据的错误。在(-π,π)内具有4个稳定的锁定点,称为四重相位模糊度。

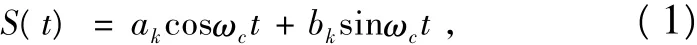

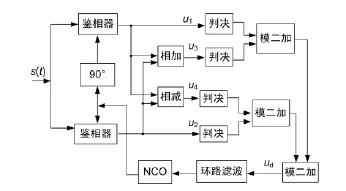

图3 QPSK数字Costas环(松尾环)

图4 载波恢复环路主要特性

图3是采用数字信号基带处理的Costas环,其基带处理器输出波形见图4(a),为矩形鉴相特性。环路中锁相环的典型“频率-电压”传输特性如图4(b)所示。当环路输入信号频率由低向高变化时,开始环路对输入信号不响应,直到f=f1时,环路锁定于该频率上,引起环路误差电压负的跳跃。接着环路误差电压ud以VCO的Kv的倒数(1/Kv)的斜率随频率改变,在这期间VCO的频率一直跟踪输入载频频率,直至f=f2时,环路失锁,误差电压降为0。这时再由高向低改变频率,在f=f3处又重新入锁,到f=f4又失锁。把f1~f3这段频率范围称为捕捉带,它表示环路由失锁到锁定的频率范围;把f2~f4称为同步带,它表示环路由锁定到失锁的频率范围。

同步带总是大于捕捉带,因为环路在锁定后,环路滤波器输出的直流电压是由其中的电容所维持,频差增大该电压也逐渐增大。当频率偏移,虽然超过了捕捉带,但直流电压仍能维持一段时间,直至频差很大,产生了幅度较大的差频信号,其幅度大于直流电压值时,环路才失锁。

由上述分析可知,NCO进入捕捉带可以正常捕获载波频率,进入锁定状态。然而从图2和图4(a)中可以看出,当NCO的初始频率设定在的整数倍,即为、-、π、等值时,其鉴相特性也会进入极小值点,则其相位会稳定在此相位附近。在锁相环中信噪比较低时,载波环中的NCO输出的频率是随机的,当NCO的初始中心频率与信号中心频率的偏差正好等于符号速率的1/4的整数倍时,即:

锁相环以符号周期工作,接收信号的载波频率为fc,则鉴相器前后采样点的相位差为:

鉴相器输出的相位误差正好在极小值点,鉴相误差使锁相环锁定在这个极小值点上,锁相环就会稳定地锁定在错误的频率上,导致出现错误现象。

2 防错锁的优化设计

2.1 防错锁的常用方法

从总的设计思路讲,防错锁采用数字处理方式最简洁且首选方法是频域处理法,即对输入的数字信号,经FFT变换后在频域内做防错锁的各项工作。

频域变换法可分为2种思路:① 宽带防错锁;②频率扫描。这2种方案的选择受限于信号输入的带宽。随着全数字化中频接收机的实现,接收机信号的处理带宽将远大于多普勒频率的变化范围。

对于宽带防错锁,采用FFT变换可求解防错锁。接收机处理带宽的设计略大于待解调信号的带宽。该方法的优点是处理速度快,只需经几次FFT运算(对应每一次的错频谱搬移),经简单的比对处理即可求解出载波频率;将求解出的载频正确值置入载波环路中,从而达到防错锁的目的。但缺点是错锁概率大,不能很好地解决影响防错锁性能的因素。但该方法提供了解决防错锁问题的基本思路。

频率扫描防错锁是在第1种思路基础上的一种改进型。扫频防错锁法是对信号带宽内的整个频谱进行全面分析,然后根据所设置的防错锁判决准则进行错锁判断。该方法中主要是采用直接数字合成(DDS)完成对所接收到的信号的整个信息带宽的扫描,从而实现锁相载波环防错锁所必需的频谱分析。该方法的优点是错锁出现的概率较低,且可以改善信号系统的其他指标;缺点是系统捕获时间较长,设计较为复杂,要求硬件平台的性能要高。

这2种方法虽然可以使得错锁概率有效降低,但由于其系统捕获时间长、设计复杂,同时对硬件要求较高,不利于工程实践中的广泛应用,特别是当系统捕获时间是一项很重要的技术指标时,更难以满足高实时性的需求。

2.2 防错锁方法的改进措施

这里是针对某实际工程项目中QPSK信号的锁相接收系统中曾出现的载波捕获错锁的问题,研究了相应的防错锁方法,下面将主要介绍分析和解决该问题的过程。

由于该系统中采用的是数字相干正交解调方式。当QPSK解调器出现错锁问题时,工程技术人员通过对锁相环路的仔细分析,发现:只有当设定中心频率与信号中心频率的偏差正好等于符号速率1/4倍符号速率的整数倍时,锁相环就会稳定地锁定在错误的频率上,导致出现错误现象。

首先采取的检测错锁措施如下:将这个可疑频点暂定为载波信号,利用系统监控的预置调制频率等信息在频谱上做分析,运用输入参量求证载波错锁现象的复现。将可疑频点送入载波的跟踪锁相环,进行疑点频率的跟踪处理,同时对已知边带信号进行相干正交解调,解调后正交信号做幅度检波,发现该可疑频点确实为造成错锁的主要原因。因此,如何在锁相环路的输入中将该可疑点频删除,或防止其进入载波捕获的支路,成为该QPSK接收系统中必须要解决的主要问题。

基于上述对载波捕获错锁原因的分析,提出了如下几点防错锁方法的改进措施。

(1)对数字锁相环载波频率增加限制条件

即当数控振荡器(NCO)的输出频率fo的绝对值大于符号速率 Rs的5%时,强制将 fo设定为 fo=±0.05Rs,保证NCO的输出频率在限定的范围内,无法输出导致错锁的频率。这样,通过增加限制条件的约束方法,相当于删除或滤除了造成错锁的可疑频点。

(2)优化相位跟踪和频率跟踪的工作流程

①为了避免相位跟踪对频率跟踪的影响(可能会导致频率跟踪不收敛),在频率未同步时,将相位支路从环路中断开,或让相位偏差检测器输出强制为0;

②在频率同步以后(即频率锁定检测指示器为“1”),连通相位支路,允许环路进行相位跟踪;

③相位跟踪阶段,频率支路既可以断开,也可以保持连通,可以通过工作模式设置;

④相位同步后,需要断开频率支路;需要使用频率锁定检测指示器和相位锁定检测指示器来判断环路是否己经锁定。

3 仿真试验与性能分析

3.1 仿真试验

试验条件:采用信号源Agilent E4438C作为仿真信号输入,设置信号参数为:调制样式QPSK,符号速率Rs=2 048 ksps,射频频率 fc=2 690.512 MHz。在QPSK接收机监控软件上设置解调频率=2 690 MHz,即人为地将信号源的射频频率和接收机接收频率相差512 kHz(即Rs/4),此时解调器已经稳定地锁定在虚假的频率点上,解出的码流与原始比特流不能完全对应,如图5所示。

图5 可能产生的错锁点

对载波环路中增加了NCO的输出频率范围的限制后,再次进行测试,如图6所示。将NCO的初始频率与实际载波频率值的偏差分别设置为符号速率的1/4、1/2和本身时分别进行测试,NCO都会被强制拉回载波频率附近,解决了载波恢复环路进入其他错误极小值点的问题。

图6 改进后避免进入错锁点曲线

3.2 性能分析

该系统中通过采用对数字锁相环载波频率增加限制条件和优化相位跟踪及频率跟踪的工作流程,确保了数字锁相环路从接收的数字中频信号中提取出正确的相干载波信号。该防错锁优化方法在可靠性、抗扰度和经济性等方面都有效地提升了QPSK信号解调器的性能。

4 结束语

相干解调中载波环路的设计将直接影响解调器的性能。由于环路噪声的存在,鉴相器初始频率的随机性会影响鉴相器进入错误的极小值点,导致锁相环发生错误锁定,不能完成载波频率的正常恢复。通过对载波恢复环路鉴相特性的分析优化工作流程设计,并对数字锁相环载波频率增加限制条件,弥补了解调器载波恢复环路的设计缺陷。通过仿真试验和工程测试,验证了该防错锁优化方法的有效性和可行性。

[1]梁保卫,陈仕进.大频偏低信噪比条件下QPSK载波环的设计[J].无线电工程,2009,39(9):51-54.

[2]SOME Y K,KAM P Y.Bit-error probability of QPSK with noisy phase reference[J].IEEE Proc Commun,1995,142(5):292-296.

[3]李荔,陈寅健.LEO小卫星突发数据通信系统中载波恢复环路的误捕获分析[J].电子学报,2002,6(30):839-842.

[4]李肃刚,杨家志.一种改进的全数字锁相环设计[J].微计算机信息,2005,21(25):42-43.

[5]蓝智,谢显之.基于DDS扫频频谱分析的锁相载波环防错锁实现[J].测控技术,2007,26(1):15 -17.

[6]李海涛,李国民.载波捕获防错锁技术新探[J].飞行器测控学报,2003,22(1):36 -40.

[7]王鹏毅.高动态扩频信号的捕获跟踪与解调[J].飞行器测控学报,2003,22(2):34 -36.