基于嵌入式方法的浮点单元验证系统设计

2012-07-25王云贵

王云贵,杨 靓

(西安微电子技术研究所,西安710054)

1 引言

目前芯片的验证已经成为IC领域面临的一大挑战。对于IC前端设计而言,用于设计和验证的时间比例达到了3:7,即不得不把大部分时间用于验证,由此可见验证对于IC的重要性。对浮点单元而言,验证更加困难。Intel曾经因为奔腾处理器的浮点错误而损失了数以亿计的美金,而且严重损害了公司的声誉。为了对某定浮点合并的FALU[1]进行验证,文献[1]采用特殊数据和随机数据相结合的方法对其进行了充分的功能仿真,但是只进行功能仿真是不够的。在芯片流片前为了在实际电路中对其进行验证,一般都需要用FPGA做原型验证。一种方法是直接把FALU综合后下载到FPGA里对其进行验证。这里采用另外一种方法,利用Xilinx公司FX系列带PowerPC 405硬核的FPGA,通过APU控制器把FALU连接到PPC 405核,然后编写测试程序,通过自定义指令访问FALU,然后通过程序的运算结果来判断FALU的功能是否正确,即设计一个嵌入式处理器系统来对FALU(其它IP也可以)进行验证。

2 创建硬件平台

2.1 PowerPC 405流水结构图

PowerPC405处理器拥有辅助处理单元控制器APU(Auxiliary Processor Unit),使得用户可以添加自定义指令集。用户通过FPGA设计自己的IP核,也称为结构性从处理模块FCM(Fabric Co-processor Module),完成必要功能(如加密解密、压缩解压缩以及浮点运算),FCM通过使用FPGA逻辑资源来实现[2]。通过APU控制器,扩展必要的指令,将FCM的功能流程与PowerPC405主处理器流水线更紧密的结合在一起,该方式具有的优势是其它方式,比如总线外设等方式无法达到的[3]。图1显示了PowerPC405处理器核、APU控制器以及结构性从处理模块三者之间的流水结构[4]。

APU控制器主要解决两个问题:一是进行快速PowerPC405时钟和慢速FCM接口时钟之间的同步;二是译码某些FCM指令,把指令需要的CPU资源(比如需要 CPU的 GPR作为源操作数)通知CPU。取决于FCM的应用,APU控制器能够译码所有指令,或者APU译码部分FCM译码部分,或者全部由 FCM 译码[5]。

当指令到译码阶段时,它同时被传给PowerPC处理器和APU控制器,如果这不是一条CPU能够认识的指令(即不是原生的PowerPC指令),处理器就期望APU控制器给其返回一个指令有效的响应信号,如果APU指令有效,则处理器把需要的操作数传送给APU。被传给APU的指令可以是在指令集体系架构(ISA)预先定义的也可以是用户自定义的[3]。

图1 PowerPC405流水结构图

2.2 创建一个基本系统

对大多数的嵌入式系统设计来说,Base System Builder(BSB)能够自动进行基本的硬件和软件平台配置任务。如果目标开发板来自Xilinx公司或者其合作伙伴,BSB支持从相应的开发板上选择可用的外围设备,自动使得FPGA管脚和目标板相匹配,创建一个完整的硬件平台。如果在用户自己设计的开发板上进行设计,BSB可以让你根据你的板子选择处理器核(MicroBlaze、PowerPC)和多种外围设备,并且连接它们,这样就创建了一个基本硬件平台,通过这个起点,可以根据需要添加更多的外围设备,通过XPS工具的支持,还可以添加定制的外设。

2.3 添加FCB总线

基本系统建好后,打开IP核目录子窗口,展开Bus and Bridge目录,选择Fabric Co-processor Bus(FCB),右击,选择添加IP,则将FCB总线添加到系统了,在编辑窗口的 Bus Interface子窗口中展开ppc405_0目录,在MFCB栏的下拉菜单中选择fcb_v10_0,这样就将FCB连接到了PowerPC405处理器上。

图2 添加FCB总线

APU控制器和FCM模块之间有很多信号,但是一般只用到其中的少部分。下面对用到的重要接口信号做简单介绍。

从FCM输出到APU的信号:

(1)FCMAPURESULT[0:31],通过 APU 传给CPU的FCM模块的执行结果。

(2)FCMAPUDONE,通知APU控制器:FCM中的指令执行完毕,对于自治指令来说,这个信号仅仅表示FCM能够接收下一条指令了。

(3)FCMAPURESULTVALID,表示结果FCMAPURESULT[0:31]等信号值有效。

从PowerPC405处理器通过APU控制器传给FCM模块的信号:

(4)APUFCMINSTRUCTION[0:31],通过 APU传给FCM模块的指令,当APUFCMINSTRVALID信号为高时,它的值有效。

(5)APUFCMINSTRVALID,在两种情况下这个信号会变高,一是APU控制器译码了一个有效的APU指令,二是一个未译码的指令传给 FCM,由FCM进行译码。

(6)APUFCMRADATA[0:31],从通用寄存器GPR传过来的源操作数(RA)。

(7)APUFCMRBDATA[0:31],从通用寄存器GPR传过来的源操作数(RB)。

(8)APUFCMOPERANDVALID,表示传过来的操作数有效。

(9)APUFCMDECUDI[0:2],指示 APU 控制器译码的是哪条UDI指令(总共8条)。

为了能够使用APU与UDI,需要在system.mhs文件中将其使能,在system.mhs中找到ppc405_virtex4,把APU使能控制参数添加到相应的位置,同时添加UDI的配置参数。下面夹在注释行中间的就是手动添加的配置参数,其它的由系统自动生成[7]。

2.4 添加FCM模块

在工程目录下,有个叫pcores的文件夹,这是用来放置用户自己IP的文件夹。文中设计的FCM模块就是需要验证的浮点单元FALU,在工程中的名字叫fcmfalu。在pcores目录下面新建一个子目录:fcmfalu_v1_00_a,在这个目录下新建两个子目录:data和hdl。如果FCM模块中要用到Xilinx公司提供的IP,则还需要建立一个叫netlist的目录,这个目录用来放置这类IP的网表文件。

在data目录下新建两个文件:fcmfalu_v2_1_0.pao和fcmfalu_v2_1_0.mpd。后缀为.pao(Peripheral Analyze Order)的文件包含了用于综合的HDL文件,定义了仿真时的分析顺序;后缀为.mpd(Microprocessor Peripheral Definition)的文件定义了IP的接口信号,它具有如下三个特点:列出了总线接口的端口和默认连接关系,列出了参数和默认值。另外还有一个后缀为.bbd(Black Box Definition)的文件,它定义了FCM模块中黑盒子部分的网表文件的存放位置,如果FCM模块中使用了这类IP,则需要这个文件,如果没有使用,则不需要。

Hdl目录用于存放FCM模块的IP源码,下面可以有两个子目录,如果IP是使用VHDL描述的,则将.vhd文件放在vhdl目录下;反之,如果IP是用Verilog HDL描述的,则将.v文件放在verilog子目录下。

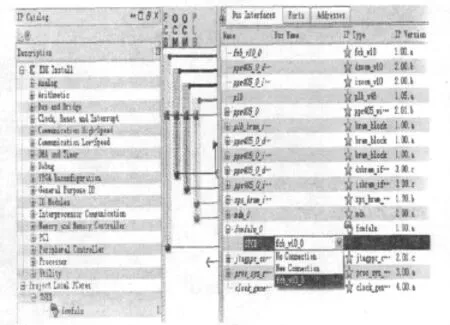

把data、hdl以及netlist文件夹下面的文件都设置好后,在XPS的菜单栏中选择Project->Rescan User Repositories,则XPS会把用户IP加载到工程信息域窗口的IP目录子窗口的Project Local PCores下面,右击用户IP核fcmfalu,选择添加IP,这样就把用户IP核fcmfalu添加到系统中了,然后在编辑窗口的Bus Interfaces子窗口的fcmfalu_0栏的下拉列表里面选择fcb_v10_0,这样就把FCM模块fcmfalu连接到FCB总线上了,如图3所示。2.3节中,把FCB总线连到了PowerPC405处理器的APU控制器上,这样FCM模块就通过FCB总线与APU控制器连接起来了。至此,浮点单元验证系统的硬件平台就建立完毕了,PowerPC 405处理器能够通过APU控制器访问被测的浮点单元。

图3 将被测浮点单元fcmfalu连接到FCB总线上

3 创建测试程序

有两种创建应用软件的方法:一是直接用XPS,二是使用SDK(Software Development Kit)。SDK是EDK工具中与XPS互补的一种工具,它用来开发应用软件工程,它基于Eclipse开源标准。对于较大的应用软件开发,Xilinx推荐使用SDK。

嵌入式软件平台为每个处理器定义硬件外设的驱动程序(板级支持包),库文件,标准输入输出接口,中断处理程序和其它相关的软件属性。基于软件平台,XPS可以进一步定义在各个处理器上运行的应用软件,在软件平台设置窗口可以设置驱动程序,库文件以及操作系统。

默认的操作系统是Standalone,它提供板级支持包,这意味着在应用程序和硬件平台之间没有操作系统,应用软件通过直接调用驱动程序操作硬件平台,应用程序可以使用驱动程序和基本的库文件。standalone是一种简单、低层次的软件层,它提供对基本处理器特征的访问,比如:高速缓存、中断以及基本输出等。这种模式不适合复杂的应用程序,但是它提供了基本的库文件,因此对简单应用是非常适合的,软件平台设置好后就可以编写用户程序了。

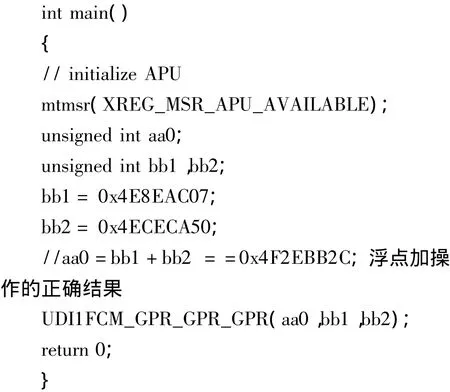

为了对浮点单元进行验证,需要编写相应的浮点测试程序让其执行,这样就可以通过程序的结果来判断浮点单元是否正确。文献[1]设计的FALU能够执行21条指令,为了简便起见,这里仅演示对浮点加法指令进行测试,其它指令的测试原理是一样的。自定义指令UDI1FCM_GPR_GPR_GPR(aa0,bb1,bb2)的作用是把bb1,bb2两个源操作数传递给浮点单元执行,浮点单元执行完毕后把运算结果返回给PowerPC 405处理器,PowerPC 405将结果保存在变量aa0中。最简单的测试程序如下所示。

4 系统仿真

硬件平台和测试软件都创建完毕后,对浮点单元FALU进行验证的嵌入式系统就建好了,下一步就可以进行仿真了。大多数现代仿真器要求在使用它们进行仿真之前首先编译HDL库,编译HDL库的好处包括更快的执行速度和更少的内存占用量。

在仿真库编译过程中如果没有错误产生,就可以进行下一步的操作:产生仿真模型。EDK产生一个后缀为.do的文件来编译产生的仿真模型,这个文件包含了仿真库的映射和编译命令,在Modlesim中输入do system.do编译仿真模型,仿真模型编译完毕之后,在仿真之前还必须加载仿真文件,加载命令取决于顶层的HDL语言,如果EDK创建的顶层文件是VHDL格式的,则用vsim system命令加载设计,如果是Verilog格式的,则用vsim system glbl命令加载设计。系统仿真波形如图4所示。

图4 系统仿真波形

从仿真波形可以看出PowerPC405处理器根据 测试软件中的指令向 FCM模块(在这里是被测FALU单元)发出了正确的控制信号,如instrvalid(指令有效)信号、instruction(指令)信号、decoded(指令译码)信号、decudivalid(UDI有效)信号、operandvalid(操作数有效)信号以及两个操作数afufcmradata、afufcmrbdata。FCM 接到 PowerPC405发出的指令信号和数据信号后进行计算,计算结束后把结果返回给PowerPC405,并给出相应的指示信号:fcmapudone,fcmapuresultvalid以及返回的结果:fcmapuresult。根据仿真波形可以看出,本系统能够有效的对被测IP进行验证。如果需要对浮点单元进行更完善的验证,可以编写更加复杂的测试程序。很明显,通过这种嵌入式方法对浮点单元进行验证(其它功能的IP也类似)比直接将其网表下载到FPGA里进行验证要好的多。

5 结束语

介绍了一种基于嵌入式系统对浮点单元进行验证的方法,该方法对其它IP的验证也一样适用。该验证系统的硬件平台基于Xilinx公司FX系列带PowerPC 405处理器硬核的FPGA,该FPGA有APU控制器接口,通过该接口PowerPC 405处理器可以对被测IP进行访问,然后通过编写测试程序对浮点单元进行测试,通过程序的运行结果来判断浮点单元的正确性。上面的例子说明了该方法的有效性。当然,也可以用这种方法构建一个嵌入式系统,让PowerPC 405处理器执行简单指令,让FCM模块执行复杂的运算密集型指令,通过这种方法可使系统速度提高数倍到数十倍[7]。

[1] 王云贵,杨靓.一种定浮点合并的FALU的设计与实现[J].微处理机,2011,32(2):7-9,13.

[2] Xilinx.Virtex-4FPGA User Guide UG070(v2.6)[Z].Xilinx.,2008.

[3] Xilinx.PowerPC 405 Processor Block Reference Guide Embedded Development Kit UG018(v2.4)[Z].Xilinx.,2010.

[4] Xilinx.PowerPC ProcessorReferenceGuideUG011(v1.3)[Z].Xilinx.,2010.

[5] Xilinx.Fabric Co-processor Bus(FCB)(v1.00a).Product Specification.DS308[Z].Xilinx.,2009.

[6] Xilinx.Implementing a Virtex-4 FX C-to-HDL Hardware Coprocessor Accelerator in a PowerPC Design Design Guide.UG096(v2.0)[Z].Xilinx.,2007.

[7] Endric Schubert,Felix Eckstein.Extend the PowerPC Instruction Set for Complex Number Arithmetic Using the APU inside a Xilinx Virtex-5-FXT[J].Xcell.Journal Fourth Quarter 2008:44-47.