基于FPGA的数字频率合成器设计与实现

2012-07-17贾伟伟李美凤

贾伟伟,李美凤

(徐州工业职业技术学院,江苏徐州221140)

数字频率合成器(DDS,Direct Digital Synthesizer)是一种数字控制的锁相倍频器。其输出频率是基准频率的整数倍,通过频率选择开关改变分频比来控制压控振荡器的输出信号频率。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,是实现设备全数字化的一个关键技术,广泛使用在通信与电子仪器领域[1]。

1 DDS基本原理

DDS的工作原理是以数控振荡器的方式产生频率、相位可控制的正弦波。电路一般包括基准时钟、频率累加器、相位累加器、幅度/相位转换电路、D/A转换器和LPF(Low Phase Filter,低通滤波器)。

DDS的具体工作过程如图1所示。N位相位累加器由N位加法器和N位累加寄存器组成。每来一个时钟脉冲,N位加法器将频率控制字K与N位累加寄存器输出的累加相位数据相加,并把相加后的结果送至累加寄存器的输入端。累加寄存器一方面将上一时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,使加法器在下一时钟的作用下继续与频率控制字K相加;另一方面将这个值作为取样地址,送入幅度/相位转换电路,使其输出相应的波形数据。最后经D/A转换器和LPF将波形数据转换成所需要的模拟波形。

图1 DDS的工作原理图

相位累加器在基准时钟的作用下,进行线性相位累加,当N位相位累加器累加N次后就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS信号的频率周期。

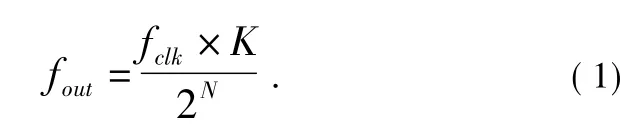

DDS模块的输出频率fout是系统工作频率fclk,相位累加器比特数N及频率控制字K三者函数,其数学关系由式(1)给出[2,3]:

其频率分比率为K/2N。

2 系统设计

2.1 相位累加器的设计

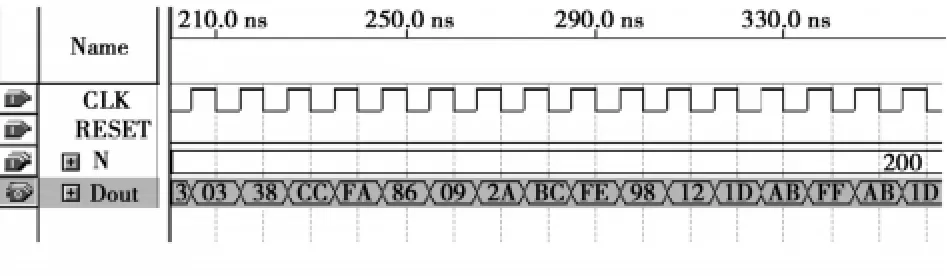

相位累加器是典型的反馈电路,由N位全加器和N位累加寄存器级联而成,对代表频率的二进制码进行累加运算[4]。相位累加器的位数N=32。可以达到较高频率分辨率。该模块通过Verilog语言编写。仿真电路如图2所示。

图2 相位累仿真图

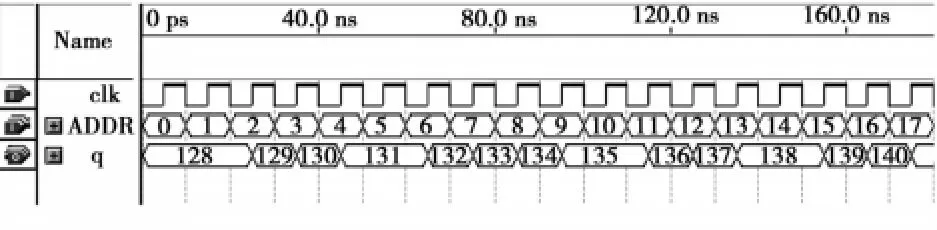

2.2 存储波形信号的ROM的设计

本模块ROM的设计,基于ALTERA公司的开放的IP核,自动生成,其存储的正弦波波形文件,即初始化文件,通过 C 语言编写,生成波形数据存储到 ROM 中[5,6,7]。由于采用的DAC器件为8位输入,因此本文设计的ROM数据宽度为8,不过为了提高精度,存储器深度选为1024。仿真电路如图3所示。

图3 波形文件仿真图

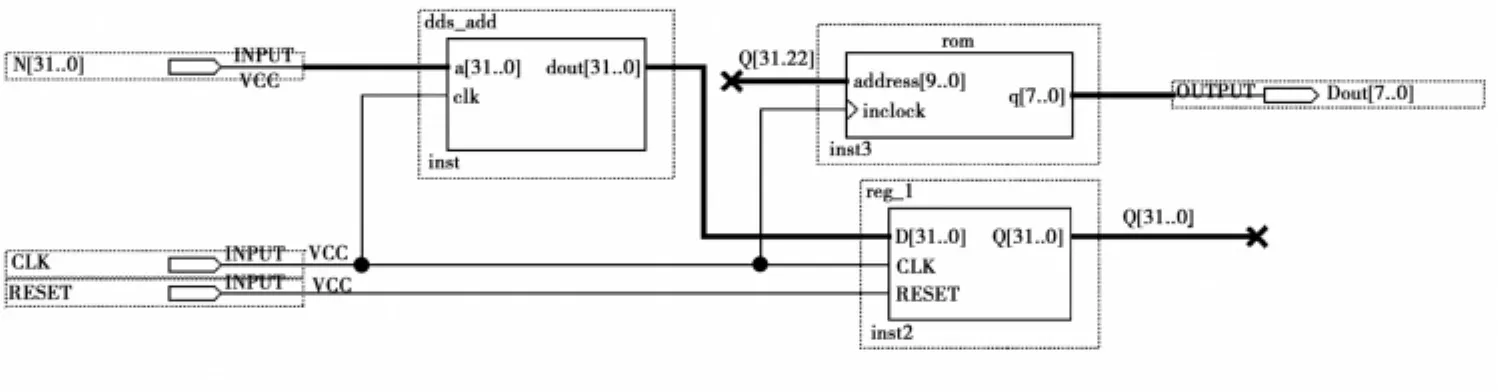

2.3 系统整体模块及仿真图

本系统整体电路图如图4所示,包括累加器、32位的寄存器、存储波形的ROM三部分组成。其中累加器进行DDS相位调节,输出的结果,送入32位的D触发器,产生读取ROM的地址信号,由于受到ROM的限制,我们截取高10位作为读取ROM的地址信号,产生稳定的信号。输入后续的ADC及滤波电路进行处理,输出稳定的波形[8]。仿真电路如图5所示。该系统很好地实现了波形数据的读取。

图4 系统设计模块图

图5 系统功能仿真图

3 结束语

本文在FPGA开发平台上,基于DDS工作原理,用VerilogHDL语言设计并实现了DDS直接频率合成,经过D/A转化和外加滤波整形电路处理波形数据,输出频率可调的正弦波。可以作为信号源使用。具有较好的实用价值[9]。

[1]黄仁欣.EDA技术实用教程[M].北京:清华大学出版社,2009.

[2]徐春河,张美华.基于PLL的直接数字频率合成器研究[J].煤炭技术,2011,1(1):140 -142.

[3]王本君.直接数字式频率合成器的设计[J].大众科技,2010,6(130):41 -42.

[4]熊兴中,杨平先,吴治隆.基于Verilog HDL的 DDS相位累加器的一种优化设计[J].四川轻工学院学报,2004,6(2):49 -53.

[5]罗杰汉,程光伟.基于FPGA的DDS设计[J].电子设计工程,2010,1(1):66 -70.

[6]李明,臧凤仙.基于FPGA的甚高频 DDS的设计[J].微计算机技术,2011,2(27):13 -15.

[7]常红霞,陈初侠,周平.基于FPGA的直接频率合成器的设计[J].皖西学院学报,2011,4(2):82 -84.

[8]范照盛,崔竹,胡志慧.一种基于DDS的宽带频率合成器设计[J].研究与开发,2011,1(1):32 -34.

[9]张敏,孙丽丽,乔晓林.直接数字频率合成器的PFGA实现[J].现代电子技术,2011,5(10):71 -73.