基于PMOS三维选通高速门控技术

2012-07-04杨金宝范松涛曾华林王新伟

杨金宝, 周 燕, 范松涛, 曾华林, 王新伟

(中国科学院半导体研究所光电系统实验室,北京 100083)

0 引言

选通三维成像可以广泛地用于导弹制导、夜视安防等技术领域[1-2]。选通三维成像与传统选通成像方式相比,对像增强器门控信号的脉宽和频率提出更高的要求。如基于步进延时的三维成像方式的脉宽和延时精度须达纳秒级甚至皮秒级[3]。用于制导等技术的三维成像方式须对大景深大目标进行实时成像,从而要求可变的脉宽以获取不同景深的目标切片和较高的重复频率以快速实时成像[4-5]。因此高重频、脉宽可变的大幅值、窄脉冲、快速上升、下降沿的可控的高速门控技术一直是三维选通成像技术的核心和难点。

实现高速门控技术主要有基于阴极选通、基于MCP选通和基于荧光屏选通3种方式,其中阴极选通方式由于选通幅值低,灵敏度高,是最常用的选通控制方式[6]。目前作为阴极选通像增强器的高速门控开关有基于雪崩三极管[6-7]和功率 MOSFET[8-9],雪崩三极管开关速度快,脉冲上升下降沿小,但脉宽不易控制;功率MOSFET开关速度快,抗干扰能力强,但寄生参数较大,且在控制电路中加入电平移位电路实现负压选通,控制电路的稳定性降低。另外也有报道使用推挽MOSFET开关的方法设计高速门控开关电路,但需要使用隔离驱动,反相器的制作需通过缠绕自制线圈,引入大量的寄生参数,结构复杂,时序控制精度不高,噪声信号干扰大[10]。

本文在传统基于功率MOSFET高速阴极选通门控开关的基础上,提出一种基于PMOS和功率三极管的互补级联高速门控开关技术,该方案可为三维选通实时成像系统提供高速门控信号。

1 高速门控开关的设计

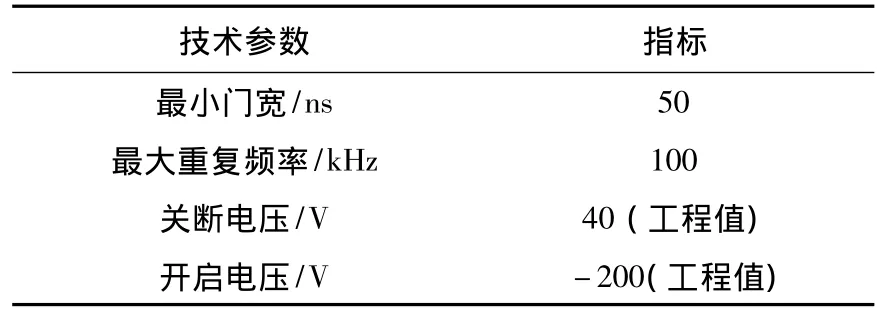

阴极选通电压为-200 V,关断电压40 V,由于选通时间很短,阴极开关时序信号的占空比接近于1,为实现大幅值的正负压快速选通,本文提出采用功率PMOS和功率三极管互补级联的方式,产生所需的阴极高压门控开关信号。所研制的三维选通门控开关主要技术指标如表1所示。

表1 三维门控开关技术指标Table 1 Technological parameters of 3D gate-control switch

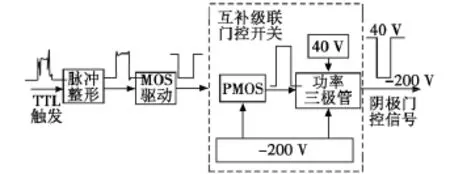

互补级联高速门控开关电路主要包括脉冲整形部分,前级开关部分和后级开关部分,电路原理如图1所示。

图1 互补级联选通开关原理图Fig.1 Complementary cascade gating switch

初始低压TTL信号由于边沿震荡大,经整形模块整形后进入PMOS驱动模块,得到峰值电流达数安的强驱动信号,该信号进入互补级联模块,先对PMOS进行开关,获得低电平为-200 V的高速正脉冲,进而触发功率三极管,最终获得低电平为-200 V,高电平为40 V的选通负脉冲信号。

脉冲整形部分,选通三维成像时序精度高,要求有较好的平顶脉冲触发信号,以免三维成像中触发电平误判,从而引起子帧信息的丢失。

选通三维门控开关的触发信号是TTL信号,该信号一般由高速数字处理电路(如CPLD或FPGA)产生[11]。但数字电路产生的信号波形边沿震荡较大,且数字电路产生的信号高电平一般为3.3 V,与后续驱动模块电平有时不兼容。

本系统设计采用TTL电平转换芯片74LVC4225将其转化为标准TTL信号电平并进行整形,减小信号震荡以防止出现电平误判。

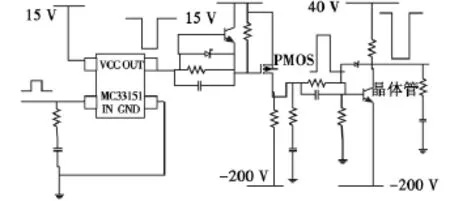

前级开关采用PMOS作为开关器件,PMOS开关性能优越,阈值电压高,抗干扰能力强,开关速度快,波形平整度好。为增加其导通速度,使用PMOS栅极驱动芯片,使之迅速导通,本设计中采用MC33151。在关断阶段,栅极电容需通过栅极串联电阻放电,放电速度受栅极串联电阻和前级负载限制,为加快栅极电容放电,使PMOS迅速关断,采用关断加速电路,使栅极电荷在关断时迅速放电。因此在级联电路的前级使用PMOS能够为后级开关提供干净的开关触发信号。

后级开关与-200 V的高压兼容,本设计中使用功率三极管ZTX857作为开关器件。功率三极管的频率特性好,开关速度快,基极驱动电流小,在级联电路中,不需使用驱动模块,开关电路简单,减少了级联电路的延时。功率三极管开关性能与MOSFET作后级驱动相比,减少了驱动延时,寄生参数少,信号畸变小,具有良好的脉宽保持特性和高重频性。

在实际电路的设计中,为增加功率三极管的关断速度,对功率三极管加上加速电容或钳位肖特基二极管,从而减小三极管关闭时的基区电荷存储时间。

功率三极管的导通阈值电压仅0.8 V,在实际电路中,为避免功率三极管关闭不完全的情况,将PMOS开关管的负压提高几伏,如器件PMOS的低端电压改为-203 V或使用一小型隔离电源芯片升压等。

由于选通开关信号高频成分十分丰富,导致尖峰脉冲较多,在电路中有时会引起电平的误判,因此在实际电路中加入RC尖峰吸收电路,对脉冲进行尖峰整形。设计完成的实际门控开关电路如图2所示。

图2 实际门控开关电路图Fig.2 Gate-control switch circuit in reality

2 门控开关电路性能分析与仿真

根据图3所示的门控开关电路结构图,其级联门控开关电路的高频信号模型如图3所示。

图3 互补级联开关模型Fig.3 Model of complementary cascade switch

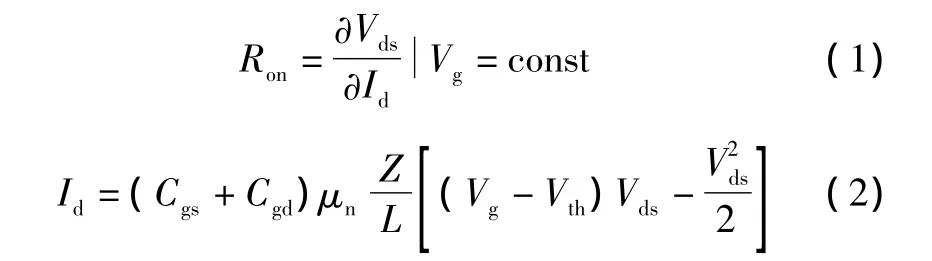

PMOS和功率三极管的导通和关断可以看作是电容充放电过程,PMOS栅极驱动可等效为一反相放大器U1,其输出电阻为R1,前级共源型PMOS开关采用高频开关模型,由栅极电阻Rg、栅源电容Cgs、栅漏电容Cgd、源漏电容Cds、沟道电流Id、源漏导通电阻Ron和寄生电感L组成,其中Cgs、Cgd主要由栅极绝缘层引起,器件封装时在漏源引入Cds。源漏导通电阻和源漏沟道电流分别为

式中:μn为电子迁移率;Z为沟道宽度;L为沟道长度;Vth为MOS导通阈值电压。

功率三极管采用高频混合π模型,即由发射结结电容 Cbe、结电阻Rbe,集电结结电容 Cbc、结电阻 Rbe和受控电流源Ic组成,它代表了基区贮存电荷的动态增长变化对发射结外加电压增长变化的依赖关系,即Vbe的改变导致基区电荷的改变,从而使Ic增加。

当输入为一正脉冲时,经PMOS驱动器后变为一负脉冲,进而对PMOS进行开关。当栅极电压为低时,栅电容Cgs开始放电,PMOS打开,导通延时时间为

PMOS导通后出现漏极电流Id,Rds迅速减小,存储在Cds和Cgd上的电荷开始通过沟道放电,Vds下降,输出脉冲上升时间

式中:CBin是功率三极管的等效输入电容;Rds为PMOS导通电阻。与导通类似,PMOS的关断过程是对栅电容进行充电,使Vgs低于阈值电压。PMOS关断时,栅极电容需经过栅极电阻放电,致使关断时间加大。由于已设计关断加速电路

关断后,Cds充电,Vds开始上升,设R2为漏极负载,则输出脉冲下降时间为

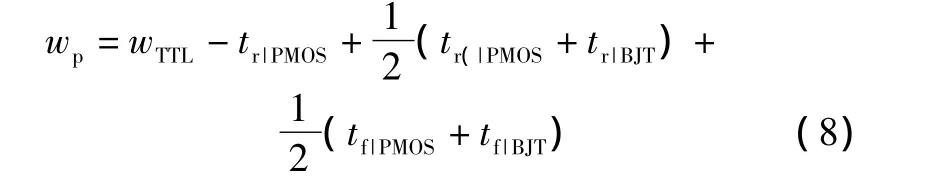

功率三极管的开关分析与场效应管相似,只是三极管是电流驱动,是出现一定基极电流后开始导通。当三极管由导通变为截止时,存储在基区的电荷需通过基极电阻释放,这段时间称为反向恢复时间,通过加速电容和肖特基钳位可大大减少反向恢复时间,其他分析方法与MOS相同,本文不再赘述。最后门控开关输出脉冲宽度为

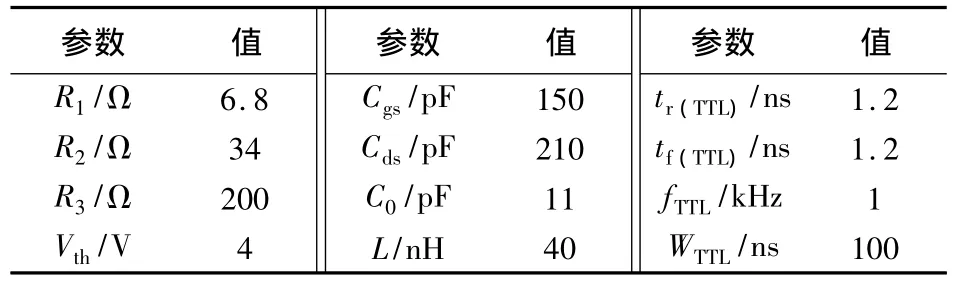

式中:WTTL为TTL触发信号脉宽;BJT为功率三极管;tr|PMOS为前级开关PMOS的上升时间;tf|PMOS为前级开关PMOS的下降时间;tr|BJT为后级开关功率晶体管的上升时间;tf|BJT为后级开关功率晶体管的下降时间。由式(8)知,前级PMOS开关脉冲的上升时间tr|PMOS需要被减去,主要是后级采用功率三极管作开关,导通电压仅0.8 V,因此在计算最终脉宽时,这项不应包括在内。由式(8)还可以看出本文设计的高速门控开关可以获得比TTL触发脉冲更窄的脉宽,这是传统门控开关所无法得到的。设置器件模型,使用PSPICE软件仿真,考虑到实际电路,设各寄生电感L设置为40 nH。参数设置如表2所示。

表2 仿真参数表Table 2 Parameters of simulation

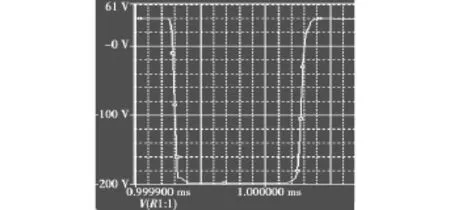

由式(7)知,选通脉冲下降时间tf=9.55 ns,由式(5)有,上升时间 tr=21.1 ns。由式(1)~式(8)有,Wp=105.75 ns,仿真结果如图4所示。

图4 门控开关仿真图Fig.4 Simulation of gate-control switch

从仿真结果可看出,选通脉冲上升沿时间为18 ns,下降沿时间为 8 ns,脉宽 97.5 ns,与分析符合较好,脉宽比触发TTL信号小的原因主要是因为寄生电感L使得前级PMOS开关的下降时间增大造成的。

3 门控开关的实现与实验

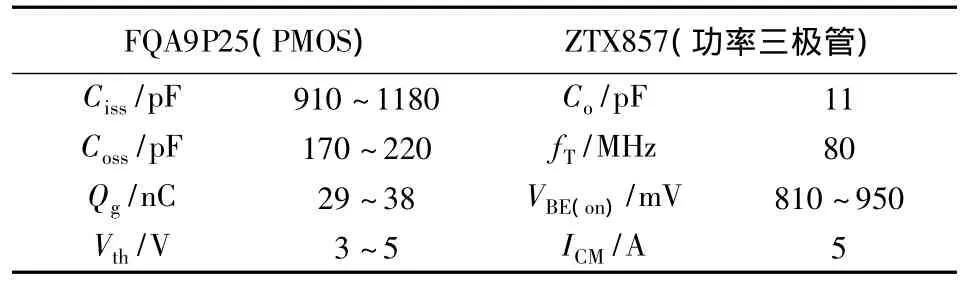

实际电路中,PMOS采用FQA9P25,功率三极管为ZTX857,二者电学参数如表3所示。

表3 PMOS与功率三极管电学参数Table 3 Electrical parameter of PMOS and power transistor

开关电路在PCB板上设计并实现,实物如图5a所示。实验中,示波器为力科WaveRunner 204MXi-A,PMOS漏极电阻 R2=25 Ω,功率三极管集电极电阻R3=300 Ω。通过FPGA输入脉宽50 ns,频率1 kHz的时序脉冲信号,经整形模块后的前后对比如图5d、图5e所示。由式(7)知,选通脉冲下降时间tf=7.0 ns,由式(5)有,上升时间tr=21.8 ns。由式(1)~式(8)有,Wp=48.72 ns。实验得到脉宽为 50 ns,上升时间24.6 ns、下降时间 13.4 ns,高电平为 40 V,低电平为-200 V的高速高压阴极选通脉冲,如图5b所示。理论与实验的差别主要是由于在实际电路板中,信号走线引起的寄生参数使得开关时域特性变差,脉冲上升、下降沿时间增大。但由于采用功率三极管作为后级开关,导通电压小,仅0.8 V,使得脉宽特性变好,刚好部分抵消寄生参数引起的不利影响,使得该门控开关具有良好的脉宽特性,而传统的门控开关,不管是基于雪崩三极管型还是普通MOSFET型,由于寄生参数的影响,脉宽特性均要变差。另外门控信号脉宽可调,图5c为脉宽是200 ns的门控信号。实验中最高重复频率100 kHz,如图5f所示。

5 实验结果图Fig.5 Experiment results

实验表明,文中设计的门控开关重复频率可调,最高达100 kHz,脉宽可调,最小脉宽为50 ns,开启电压-200 V,关断电压40 V,满足三维选通门控开关的技术要求,与传统门控开关相比,减小了寄生参数,具有良好的脉宽特性和快速的上升、下降沿。从实际的波形看出,实际信号波形与仿真波形存在差别,这主要是由于实际电路中存在寄生电感、电容,致使信号引起畸变造成的,所以在实际电路的布局布线时,要尽量减少寄生电感,如接线尽量短,走线要宽等等。

4 结论

通过理论和实验研究表明:互补级联方式选通高速阴极开关通过PMOS作为前级开关,产生好的脉冲波形,进而驱动后级功率三极管开关,实现-200 V和40 V的高速阴极选通。电路稳定性好,时序控制精度高,脉冲频率可调,脉宽可调,最小脉宽达50 ns,上升时间 24.6 ns,下降时间 13.4 ns,最高工作频率100 kHz,而且可以获得比TTL触发脉冲更窄脉宽,完全满足选通三维成像的高精度时序要求。另外在设计电路板时,应尽量减小布线时引入的寄生参数,接线尽量短,以免引起脉冲波形的畸变和震荡。

[1]董进武.机载激光雷达的背景辐射抑制技术研究[J].电光与控制,2009,16(7):84-87.

[2]WANG Xinwei,ZHOU Yan,FAN Songtao,et al.Four-dimensional flash trajectory imaging using time-delay-modulated range-gated viewing[J].Optical Engineering,2006,45(3):4301-4310.

[3]张毅,柏连发,陈钱,等.循环步进延时距离选通水下微光三维成像[J].南京理工大学学报:自然科学版,2007,31(6):753-757.

[4]ANDERSSON P.Long-range three-dimensional imaging using range-gated laser radar images[J].Optical Engineering,2006,45(3):4301-4310.

[5]贺敏,胡以华,赵楠翔,等.机载激光三维成像技术应用现状[J].激光与光电子学进展,2008,45(3):43-49.

[6]周旋.用于近贴聚焦微通道板象增强器的新颖控制电路[J].电子科学学刊,1984,6(6):473-480.

[7]LUNDY A,PARKER J R,LUNSFORD J S,et al.Avalanche transistor pulser for fast-gated operation of microchannel plate image-intensifiers[J].IEEE,1978,25(1):591-597.

[8]温伟峰,王伟,张登洪,等.像增强器微型高压电源设计[J].高能量密度物理,2008(4):177-178.

[9]韩振兴,李新碗,陈建平,等.像增强器高速选通脉冲形成电路的设计与实现[J].电光与控制,2008,15(12):72-74.

[10]张秀达.新型三维主动光学成像理论与系统研究[D].杭州:浙江大学,2008:95-98.

[11]YANG Jinbao,ZHOU Yan,FAN Songtao,et al.Picosecond timing synchronization control signal for 3D range-gated imaging[C]//SPIE,2011,8192:1-6.