一种低压工作的开关电流Σ-Δ调制器

2012-07-03牛洪军王卫东

牛洪军,王卫东

(桂林电子科技大学 信息与通信学院,广西 桂林541004)

Σ-Δ调制器采用过采样和噪声整形原理,使得噪声频谱搬移,获得高信噪比。此调制器具有高分辨率、高线性的特点。开关电流技术采用模拟电流取样实现信号处理,用CMOS工艺实现,可用MOS管的栅电容储存电荷,使得电路无需增加其他元器件,由单一MOS管就能完成电路功能,这种方式的突出优点是芯片面积小。此外,高速、低压工作、宽带及与标准数字工艺兼容也是其优势。采用开关电流技术实现Σ-Δ调制器兼具有上述两种优点,是实现模数接口的一种重要方法。

开关电流存在的时钟馈通误差对电路有严重的负面影响,影响分辨率和线性性能。本文采用全差分开关电流存储单元[1]来消除时钟馈通误差,设计了 12 bit分辨率的二阶开关电流Σ-Δ调制器并进行了仿真。

1 Σ-Δ调制器的结构

本文设计的二阶Σ-Δ调制器的结构如图1所示,采用传统结构。包括2个积分器、1个电流比较器(含延时功能)、加法器、2个电流模式DAC。

[2],在此取增益因子 a=0.5,b=1,c=1。电流模式中的相加可直接由信号线相连来完成。

2 电路设计

2.1 全差分开关电流积分器

图1包含了2个离散时间积分器。本设计的积分器框图如图2(a)所示,每个积分器电路包括2个电流模式采样保持电路,该电路采用了电流模式负反馈。负反馈开关电流记忆单元具有低输入阻抗和小传输跨导。此开关电流记忆单元的输入电阻能被降低到传统第一代开关电流存储单元的一半。电阻的降低缩短了响应时间。

图2(b)为全差分开关电流存储单元。对左半边电路加以分析,当开关Φ闭合时,转换函数是输出电流与输入电流之比,由式(1)给出:

gmi是MOS场效应管的跨导。显然,iout+=gm4VX,所以输入电阻由式(2)给出:

如果所有MOS管的偏置电流I设置相等,并且每个晶体管的宽长比调节成 gm13=gm17、gm14=gm15、gm16=gm18, 则此开关电流存储单元的输入电阻由式(3)给出:

显然,新的存储单元输入阻抗是传统第一代开关电流存储单元阻抗的一半。据此,传输误差是低的,并且运行速度高,即时间常数较低。

用全差分电路以消除时钟馈通误差[1]。当差分输出对“M5和M10”与“M4 和 M11”有一由工艺变化和电路适配引起的漂移电流Ierror时, 一个共模漂移电流Ierror将流进下一级,导致系统性能降低。为了解决这个问题,采用差分对来补偿漂移电流。如图2所示,当左侧的共模漂移 Ierror电流增加时,晶体管 M1、M2和M3的栅电压增加。节点B也一样,增加的节点电压VB产生一个补偿电流Icomp以吸收并抵消右侧的漂移电流Ierror。在右侧呈现同样的机理。最后,共模输出电流是稳定的。采用对管差分负反馈记忆单元与共模前馈电路相结合的方法,不仅加速了响应,而且也稳定了输出电流。

由存储单元构成的差分前向欧拉积分器,一个积分器电路包含两个电流模式采样保持电路。采样保持电路包含降低输入电阻的负反馈电路和改善共模失真的共模前馈(CMFF)电路两部分。积分器采用全差分结构,一方面可以在一定程度上消除偶次谐波引入的误差,另一方面可以减小孔径误差,从而提高调制器的分辨率[2]。由全差分存储单元构成的积分器即称全差分积分器。

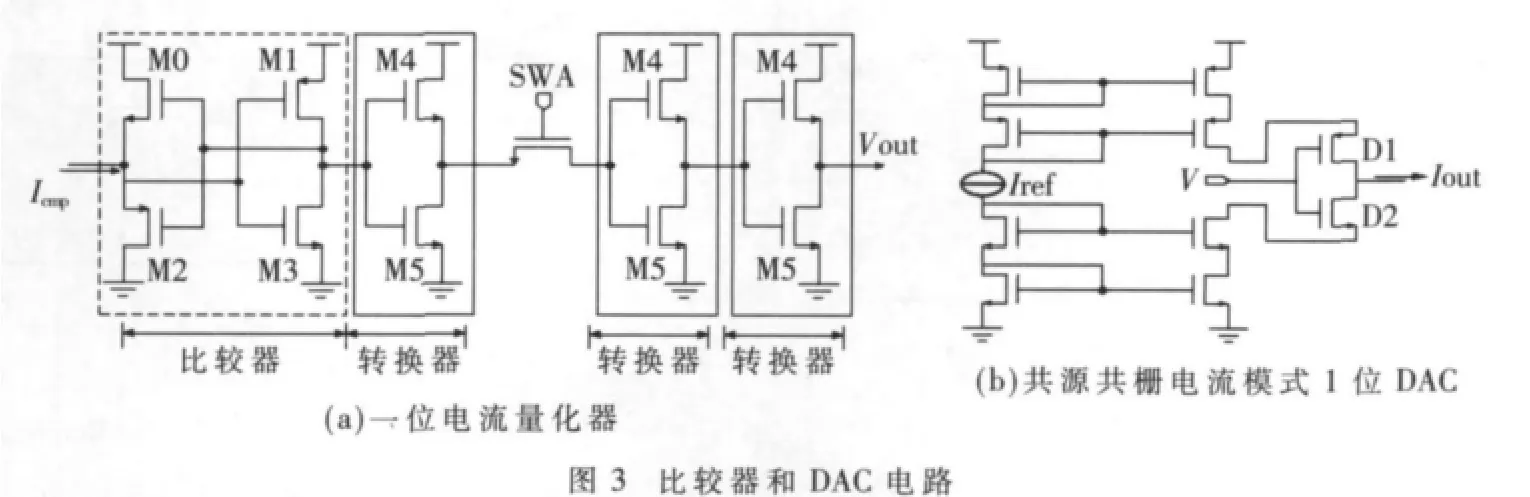

2.2 电流量化器及延时部件

比较器如图3(a)所示[3],它是通过探测电流的方向来产生正负电平的输出。积分器的输出电流分别对比较器的输入晶体管的栅电容充电或放电,从而使栅电容形成电位差并分别向电源和地电势变化,然后量化器输出发生翻转,完成电流的比较。如果输入电流Icmp流进电流比较器,则 M2(PMOS)的源电压增高,也就是M3的栅电压增高,导致M3的漏电压变低并且M2导通。相应地,输入电阻是低的,因为M2和M3同时输送。随着M3的漏电压通过级联反相器,输出电压是正的。仿真结果显示转换电流分别是+200 nA和-200 nA,即当输入电流超过200 nA时,输出级是高的,而当输入电流低于-200 nA时,输出级是低的。

增加两级反相器既可以使输出达到轨到轨电平,又可以增加驱动负载的能力。积分器输出的电流是很小的,为了提高比较器的灵敏度,比较器的放大倍数就必须设计得很大。在比较器的后面增加一个控制开关和两级反相器,输出延迟由时钟控制。

2.3 电流模式DAC电路(1位D/A转换器)

图 3(b)为带两个开关(D1和 D2)的共源共栅电流模式1 bit DAC,在此电路中,输出电流Iout镜像偏置电流Iref[4]。当开关D1打开,输出电流 Iout流出,以使Iout=Iref;然而当开关D2打开,输出电流 Iout流入,以使Iout=-Iref。

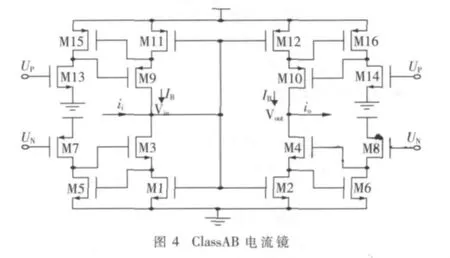

2.4 电流镜

本文设计了一款如图4所示的高性能的ClassAB电流镜,电流镜在电路中的作用有:(1)实现电流的比例输出;(2)电流镜可以起到减小传输误差的作用。设计输入电阻小、输出电阻大的高性能电流镜,这样用在电路级联中可以起到电流低误差传输的目的。两个基本电流镜就可构成同向电流镜,通过比例电流镜以实现不同的增益,组合起来可实现分流器和比例分流器。

2.5 偏置电流产生电路

在整个Σ-Δ调制器的电路设计中,会使用到几个偏置电流。而作为完整的片上系统,必须由自身电路产生这些偏置电流。因此设计了一个带隙基准电流源来产生所需的其他几个偏置电流。

2.6 开关和时钟

整个电路中包含两相非交叠时钟SWA和SWB。限于任务量,时钟采用理想时钟。另外,积分器中的开关都采用CMOS开关。

将上述基本电路模块按前文的调制器结构连接,即构成完整的调制器电路。

3 仿真结果

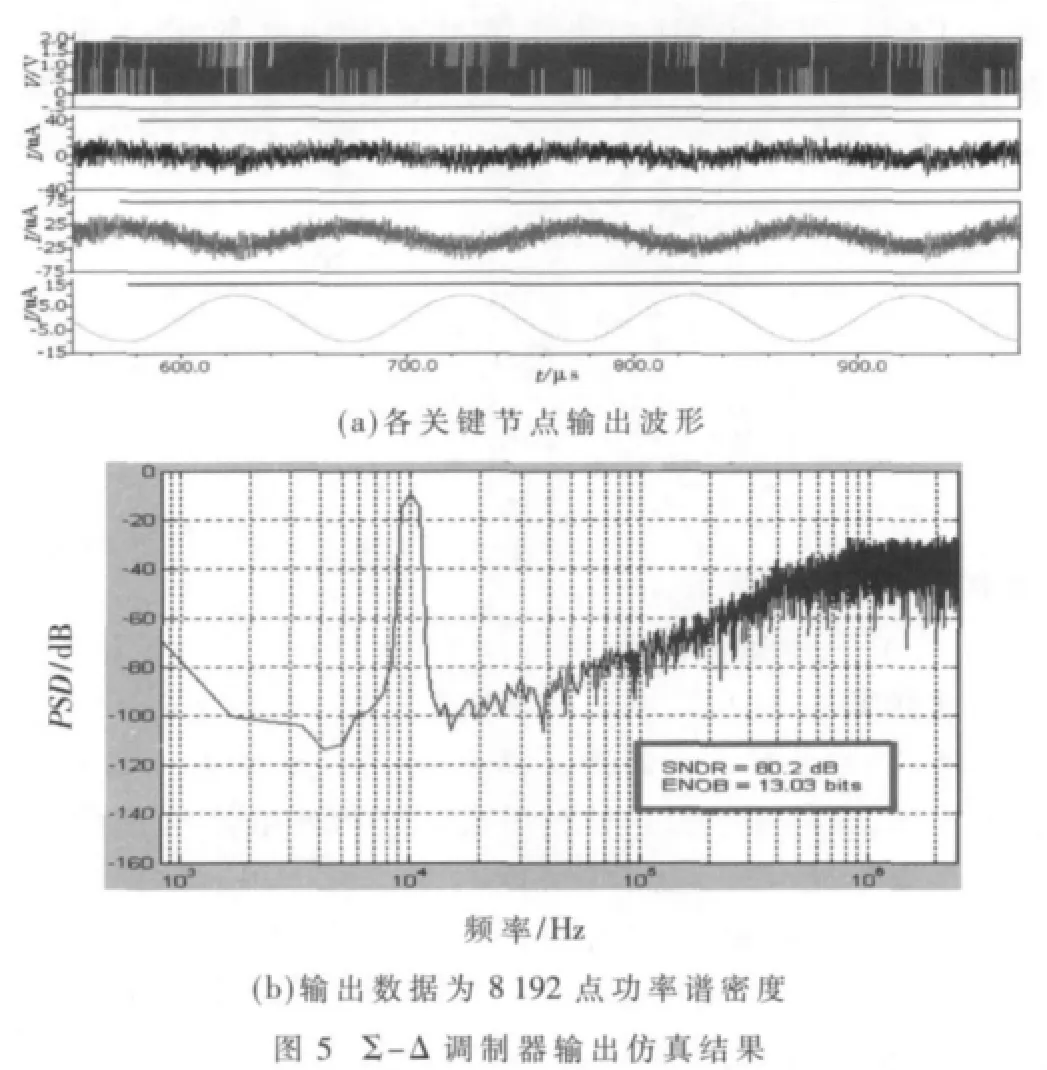

图5(a)输入信号为10 kHz、过采样比OSR为125时,二阶开关电流delta-sigma调制器的仿真输出,此输出与Matlab下的行为仿真波形一致。图5(b)为8 192点采样输出数据在Matlab下计算出的输出功率谱密度,它表明提出的调制器有80.23 dB的信噪失真比,相当于13 bit有效位数(ENOB)。在相同OSR下,越高的采样频率对应越低的信噪失真比(SNDR),即高输入频率会恶化调制器的分辨率。因此,在128倍的OSR和10.24 MHz采样频率下,建议最大输入频率为40 kHz[1,5]。Σ-Δ调制器的重要指标是信噪比,计算如下:

式中,N1表示量化器的位数,L表示调制器的阶数。

理想奈奎斯特调制器的最大信噪比如下:

由式(5)即可知道1位量化器的调制器的实际等效位数N2。

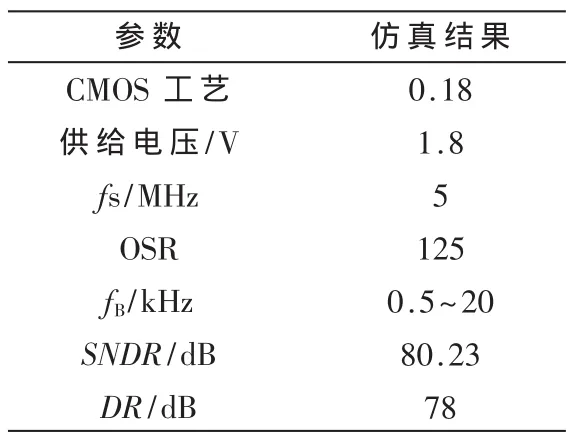

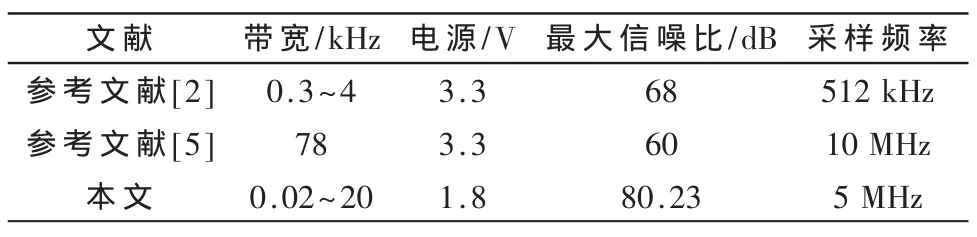

本文在 0.18 μm CMOS工艺下设计了一个二阶sigma-delta调制器。核心单元-开关电流存储单元采用全差分结构,显著地降低了时钟馈通误差和传输电导比误差。仿真表明,采样频率为 5 MHz、OSR为 125、信号频率为10 kHz时,SNDR和信号带宽分别是80.23 dB、0.5 kHz~20 kHz。本文设计的调制器不仅实现了低电压高速率的要求,而且综合性能也很优越。采用该结构调制器构成的过采样A/D转换器将是实现模数混合系统中A/D转换器的一种优选方案。其性能如表1所示。与相关文献所设计的Σ-Δ调制器性能参数的对比如表2所示。

表1 调制器性能

表2 性能比较

参考文献

[1]Sung Guoming,Yu Chihping,Hung Tsaiwang,et al.Mixedmode chip implementation of digital space SVPWM with simplified-CPU and 12-bit 2.56 ms/s switched-current delta-sigma ADC in motor drive[J].Power Electronics,IEEE Transactions on,2010(1).

[2]李拥平,石寅.一种低电压工作的高速开关电流 Σ-Δ调制器[J].电路与系统学报,2004,9(1):111-114.

[3]KUO J R,CWU H,SHIAU M S,et al.Error educed delta sigma modulator by improved memory cell for speech signal processing application[C]//Mixed Design of Integrated Circuits and Systems,2008.Mixdes 2008.15th International Conference on,2008:237-241.

[4]José M.de la Rosa Belén,Pérez-Verdú Angel,Rodríguez-Vázquez.Systematic design of CMOS switched-current bandpass sigma-delta modulators for digital communication chips[M].New York:Kluwer Academic Publishers,2004:147-345.

[5]潘宇,吴雨广.基于音频的 16位 Sigma-delta AD转换器的研究[D].西安:西安电子科技大学,2008.

[6]许刚,沈延钊.一种 12位开关电流型Σ-Δ调制器[J].微电子学,2000,30(4):234-237.