高精度SC PIPELINED ADC预放大锁存比较器的分析与设计*

2012-07-03吴金荣李晓潮郭东辉

李 扬 ,吴金荣 ,刘 磊 ,林 春 ,李晓潮 ,2,郭东辉 ,2

(1.厦门大学 电子工程系,福建 厦门361005;2.福建省集成电路设计工程技术研究中心,福建 厦门361005)

流水线型A/D转换器因其在功耗、精度上的优势而广泛应用于视频处理、数字通信、数据采集、超声和医学成像等应用领域。比较器作为A/D转换器中的关键模块,已经成为决定A/D转换器各项关键指标的重要因素之一。预放大锁存比较器因为其精度、速度上的折中,以及较低的失调电压与回馈噪声,成为高精度子ADC中必不可少的一部分。

目前多数40 MHz~50 MHz CMOS预放大锁存比较器都是采用0.18 μm或0.35 μm的工艺进行设计。采用0.18 μm工艺设计的预放大锁存比较器,其时延比较短,输入失调电压约在10 mV~30 mV之间,灵敏度在0.2 mV~0.3 mV,分辨率为 6 bit~8 bit[1]。 采用 0.35 μm/3.3 V 或2.5 V硅CMOS工艺设计的比较器,时延一般在230 ps~390 ps之间,失调电压6.8 mV,回馈噪声的毛刺峰值为6.35 mV[2-3]。为了平衡这些参数值之间的优劣,许多研究在预放大器输入、增益和输出等电路结构以及回馈噪声的隔离上进行了设计[2]。如采用交叉耦合负载、多级预放大的方式来提升预放大器的增益[3],则可减少失调,从而获得较好的精度。应用电容中和、电路隔离等方式来降低回馈噪声[3]。本文对所设计的预放大锁存比较器延迟时间进行了详细的理论建模和分析,在此基础上着重对锁存器的延迟时间、失调电压和回馈噪声进行了优化设计。

1 电路时序及原理

根据所应用的流水线工作原理可知,奇数级中的比较器必须在偶数级进入保持阶段前输出比较结果,以便控制偶数级产生保持所需要的电压余量,整个电路在两相不交叠时钟控制下工作。本文设计的流水线采样频率为 50 MHz,时钟周期为 20 ns,其中 φ1、φ2为开关电容电路的非交叠时钟,为了减少电荷注入效应(馈通效应),同时需要 φ1a、φ2a作为提前关断时钟。当 φ1为高电平时,偶数级MDAC进入保持阶段,因此比较器必须在φ2a下降沿与φ1上升沿的时间内完成比较并输出比较结果。本文中的非重叠时钟,其中 φ1、φ2的非重叠时间及 φ2a的下降沿提前时间均为0.3 ns,故比较器最大延迟时间为0.6 ns。

图1为所设计预放大锁存比较器的开关电容输入电路,当 φ1为高电平时,开关管 S2、S3导通,固定判决电平 Vrefp、Vrefn输入开关电容电路,进行电荷存储,其中Vcm为共模电平。当 φ2为高电平时,开关管 S1、S4导通,Vinp、Vinn输入开关电容电路,产生预放大锁存比较器所需差值输入电压。根据电荷守恒定律可得,预放大锁存比较器的输入电压为:

图2为本文分析的预放大锁存比较器,由预放大器、锁存器及输出缓冲器电路构成。图中M1~M7构成了预放大器,其中,NMOS管M1a、M2a构成中和电容用来减小回馈噪声[4];PMOS管 M6和 M7采用交叉耦合的形式,可以有效提高放大器的增益;M8~M15构成了锁存再生级,其中,M8、M9将预放大器的差分输出电压转换为电流,并输入到锁存器环路中,产生锁存器的初始电压差;M10、M11分别用来关断和复位锁存器;M12~M15是由两个交叉耦合的反相器构成的锁存环;M16、M17和 M18、M19分别构成两个反相器,用作比较器的输出缓冲器,提高比较器的带负载能力。

预放大锁存比较器的操作分两种模式:复位模式和锁存模式,采用来确定其操作模式。当为低电平时,比较器进入复位模式。此时,断开反相器组成的正反馈环路,预放大器对输入电压进行预放大,输出电压作用于 M8、M9。 锁存器中开关管 M10关断,复位管 M11导通,锁存环输出端被拉至同一电平;当为高电平时,比较器进入锁存模式。此时,开启反相器组成的正反馈回路,锁存器中开关管M10导通、复位管 M11关断,锁存器首先进入亚稳态[5],随后正反馈回路将M8、M9的电流差在锁存环输入端形成的初始电压差迅速放大到数字电平。

2 电路延迟时间分析与优化

式中,τL为锁存环时间常数,ΔVi为锁存环输入初始电压差。由式(2)可知减小锁存器延迟时间有两种方法:(1)减小锁存器的时间常数;(2)增大预放大器增益,增大初始电压差。 从式(2)可知,减少 τL比提高 ΔVi对缩短整个延迟时间效果更明显。

预放大锁存比较器的延迟时间包括初始电压差建立时间ta,锁存器延迟时间tp及输出缓冲器延迟时间 tbuffer。锁存环延迟时间在很大程度上决定了比较器的延迟时间。锁存环延迟时间为[6]:

2.1 锁存器设计

锁存器是由镜像管M8、M9及两个交叉耦合的反相器M12/M13、M14/M15构成,其交流小信号模型如图3所示。

图 3 中,Gm1、Gm2分别为反相器等效跨导,G1、G2分别为反相器等效电导,gm8、gm9分别为 M8、M9的跨导,C1、C2分别为Q1、Q2两点的寄生电容。由节点方程可得:

由于源区和漏区的扩散电容与栅电容的大小相当[8],且在TSMC工艺库下通过手算发现两者近似相等,为了便于计算,简化为:

进入锁存模式后,由于节点电压之间的差值很小,因此锁存器首先达到亚稳态,设此时锁存器两输出节点O1、O2的电压为 Vm,则:

考虑到功耗的因素,在设计时让M8、M9的静态电流远小于亚稳态时锁存环中的反相器工作电流,令:ID,M8/M9≈

由式(10)可以看到通过调整反相器 PMOS、NMOS管宽度比值可以获得最小的锁存器延迟。

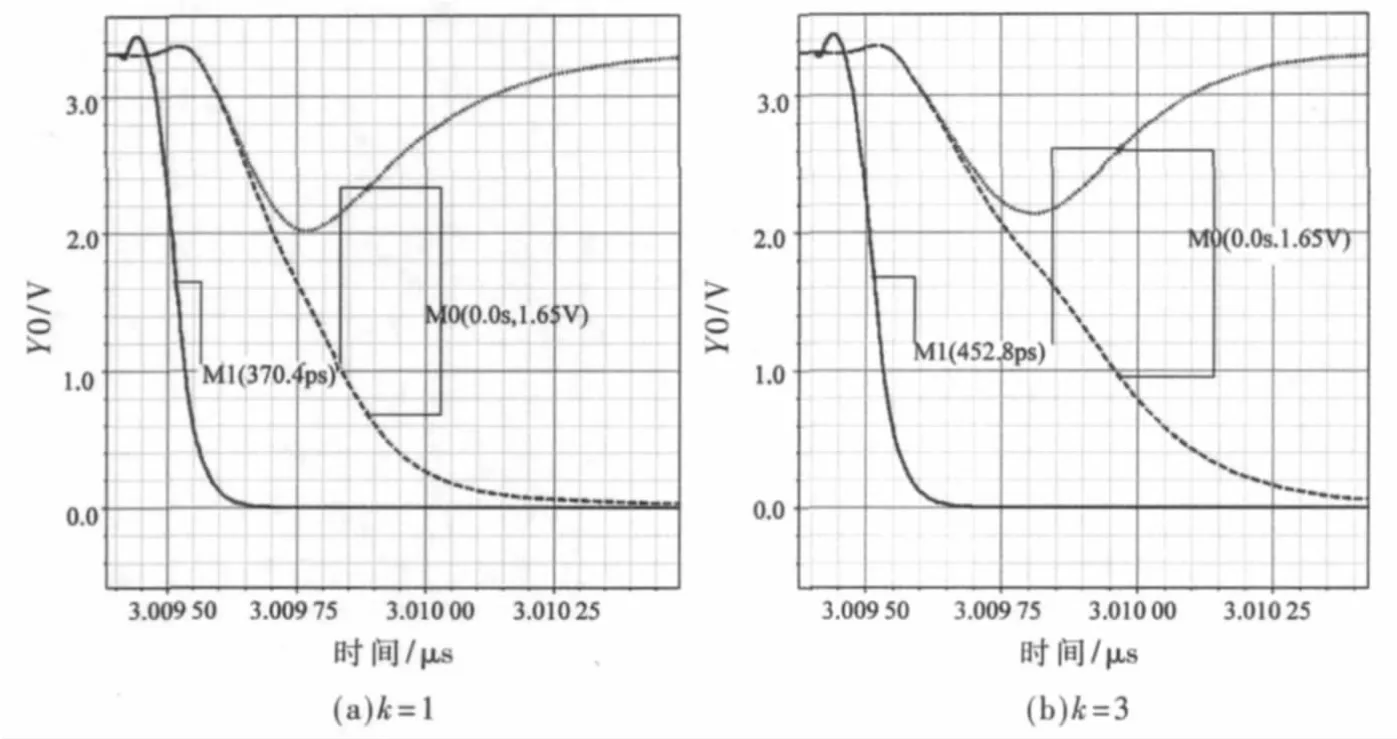

由式(11)可知,当 k=1,即 W12=W13时,锁存器的时间常数 τ具有最小值。 当k=1时,∂τL=0;当 k>1 时,τ∂k(k)>0;当 k<1 时,τ(k)<0。 因此由式(10)可知,当 k=2时,锁存器时间常数约增加6%;当k=3时,锁存器时间常数约增加15%。

2.2 预放大器优化

当比较器用于N位Flash子ADC时,比较器必须具有N+1位的精度。比较器的精度主要由比较器的回馈噪声与失调电压决定,在此假设预放大器的失调电压和锁存器的失调电压相互独立,则整个比较器的输入参考失调电压为:

为此,在预放大器设计中采用交叉耦合PMOS管作负载来提高预放大器的增益。其交流小信号模型如图4所示。

根据图4的小信号模型可得:

由式(14)可以看出只要 gm4>gm6的前提下,适当调整gm4、gm6的大小,即可有效提高预放大器的增益,从而增大锁存器的初始电压差。设计时

2.3 回馈噪声优化

回馈噪声主要是锁存器输出端的快速变化和开关管的时钟馈通通过输入管的栅漏寄生电容传递到输入端,对输入信号造成的干扰。本文采用了电容中和技术来减小回馈噪声,如图2所示。假设M1漏极电压变化ΔV,由差分对的互补性可知M2漏极电压变化为-ΔV。假设M1a、M2a的电容为 CN,M1、M2栅漏寄生电容 Cgd上的电荷变化为 ΔVCgd,CN上的电荷变化为-ΔVCN。 则当 Cgd=CN时,Cgd上电荷变化所需要的充电电流可以完全由中和电容提供,无需前级电路提供,从而避免了回馈噪声的产生。

3 仿真结果及分析

本文采用 TSMC 0.35 μm/3.3 V工艺设计了预放大锁存比较器核心电路。在Cadence环境下采用spectre对其进行仿真,时钟频率为 50 MHz,电源电压为 3.3 V,共模电压为1.65 V。

图5 不同值比较器锁存延迟时间仿真结果

图 5(a)、(b)是 M12~M15两个交叉耦合反相器 PMOS、NMOS管宽度比值k不同时,预放大器锁存比较器锁存延迟时间仿真结果。其中,Vo1为点线,Vo2为虚线,φ2a为实线。从图中可以看出,当k=1时,锁存器的延迟时间tp=370.4 ps;当 k=3时,锁存器的延迟时间 tp=452.8 ps,二者相比,前者明显减小了18%左右。最终整体仿真结果表明比较器的总延迟时间约为388tpps。

图 6(a)、(b)中实线与虚线分别给出了加入中和电容前、后预放大锁存比较器回馈噪声仿真结果,其中(a)为输入最大差分电压1.25 V时的仿真结果,(b)为输入差分电压 30 mV时的仿真结果。从图中可以看出,加入中和电容前,(a)中回馈噪声峰峰值约为23 mV(-14 mV~9 mV),(b)中回馈噪声峰峰值约为 13.8 mV(-7.5 mV~6.3 mV);加 入中和电容后,(a)中回馈噪声峰峰值约为 8.5 mV(-4.3 mV~4.2 mV),(b)中回馈噪声峰峰值约为0.14 mV(-0.06 mV~0.08 mV),可见回馈噪声得到了有效的抑制。

本文经过100次Monte Carlo模拟仿真后,通过Matlab对比较器失调电压分布进行了仿真。仿真结果表明,比较器失调电压的均值为4.92 mV,标准差为4.01 mV,分布在-14 mV~15 mV之间;比较器的输入范围为-1 V~1 V,其分辨率达到了6位。本文所设计的预放大锁存比较器满足各项设计指标,适用于采样速率为50 MS/s的高精度开关电容流水线ADC。

[1]吴笑峰,刘红侠,石立春,等.用于流水线ADC的预运放-锁存比较器的分析与设计[J].湖南大学学报(自然科学版),2008,35(11):49-53.

[2]宁宁,于奇.高速CMOS预放大-锁存比较器设计[J].微电子学,2005,35(1):56-58.

[3]杨赟秀,罗静芳,宁宁.新型高速低功耗CMOS预放大锁存比较器[J].微电子学,2006,36(2):213-216.

[4]FIGUEIREDO P M,VITAL J C.Low kickback noise techniques for CMOS latched comparators,Int SympCirc and Syst[C].Vancouver,Canada.2004.

[5]FLANNAGAN S T.Synchronization reliability in CMOS technology[J].IEEE Journal of Solid-State Circuits,1985,20(4):880-882.

[6]ALLEN P E,HOLBERG D R.CMOS analog circuit design[M].2nd Ed.北京:电子工业出版社,2003:386-396.

[7]KHOSROV D S.A new offset cancelled latch comparator forhigh-speed,low-power ADCs[M].IEEE,2010:13-16.

[8]WESTE N,HARRIS D.CMOS VLSI design-a circuits and systems perspective[M].3rd ed.,Ch2.3.1,Addison-Wesley,2005.